Test set generation and optimisation using evolutionary algorithms and cubical calculus.

TAKHAR, Jasbir S.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/20419/

# A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/20419/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

SHEFFIELD ST 1W3

101 755 600 8

REFERENCE

ProQuest Number: 10701065

# All rights reserved

# INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

# ProQuest 10701065

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code

Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

# Test Set Generation and Optimisation using Evolutionary Algorithms and Cubical Calculus

Jasbir S. Takhar

A thesis submitted in partial fulfillment of the requirements of

Sheffield Hallam University

for the degree of Doctor of Philosophy

December 2003

# **Acknowlegements**

I would like to thank, first and foremost, my supervisor Dr. Daphne Gilbert for her inspiration, encouragement and support throughout my PhD studies. There were many occasions on which her uplifting words would force me to think about a problem in another way or help me overcome the writer's block that many a thesis-writer inevitably experiences. Without her hard work and dedication, this work would not have been possible.

I would like to acknowledge other members of my supervisory and advisory team for their support including Dr. Hugh Porteous and Paul Davies of Sheffield Hallam University and Dr. Anthony Hall of Hull University. I would also like to thank Dr. Mike Thomlinson, who as a senior member of The School of Science and Mathematics, provided help in both administrative and academic matters, including the funding that enabled my participation in the IEEE Midwest Symposium on Circuits and Systems in California, USA. I must also mention Prof. Bob Green and Dr. Hamid Dehghani both, of Sheffield Hallam University, for providing an excellent laboratory environment in which I conducted much of this work.

The test set minimization algorithm was proven to be successful by minimizing test sets generated by Prof. Raimund Ubar's team at Tallin Technical University, Estonia. In particular, I would like to thank Jaan Raik and Annti Markus for actually generating the test sets and providing technical support. This collaboration was one of the highlights of this research project as it validated the minimization work.

# Dedication

To Mum, Dad, Sam and Didi.

#### **Abstract**

As the complexity of modern day integrated circuits rises, many of the challenges associated with digital testing rise exponentially. VLSI technology continues to advance at a rapid pace, in accordance with Moore's Law, posing evermore complex, NP-complete problems for the test community. The testing of ICs currently accounts for approximately a third of the overall design costs and according to the Semiconductor Industry Association, the per-transistor test cost will soon exceed the per-transistor production cost. Given the need to test ICs of ever-increasing complexity and to contain the cost of test, the problems of test pattern generation, testability analysis and test set minimisation continue to provide formidable challenges for the research community. This thesis presents original work in these three areas.

Firstly, a new method is presented for generating test patterns for multiple output combinational circuits based on the Boolean difference method and cubical calculus. The Boolean difference method has been largely overlooked in automatic test pattern generation algorithms due to its cumbersome, algebraic nature. It is shown that cubical calculus provides an elegant and economical technique for solving Boolean difference equations. Formal mathematical techniques are presented involving the Boolean difference and cubical calculus providing, a test pattern generation method that dispenses with the need for costly circuit simulations. The methods provide the basis for test generation algorithms which are suitable for computer implementation.

Secondly, some of the core test pattern generation computations outlined above also provide the basis of a new method for computing testability measures such as controllability and observability. This method is effectively a very economical spin-off of the test pattern generation process using Boolean differences and cubical calculus.

The third and largest part of this thesis introduces a new test set minimization algorithm, GA-MITS, based on an evolutionary optimization algorithm. This novel approach applies a genetic algorithm to find minimal or near minimal test sets while maintaining a given fault coverage. The algorithm is designed as a post-processor to minimise test sets that have been previously generated by an ATPG system and is thus considered a static approach to the test set minimisation problem. It is shown empirically that GA-MITS is remarkably successful in minimizing test sets generated for the ISCAS-85 benchmark circuits and hence potentially capable of reducing the production costs of realistic digital circuits.

**Keywords**: Digital testing, automatic test pattern generation, ATPG, Boolean difference, cubical calculus, testability analysis, controllability, observability, test set minimization and compaction, combinatorial optimization, evolutionary algorithms, genetic algorithms.

| CHAPTER 1. DIGITAL TESTING                                                      | 4                                |

|---------------------------------------------------------------------------------|----------------------------------|

| 1.1 Introduction                                                                | 4                                |

| 1.2 BASIC TERMINOLOGY                                                           | 12                               |

| 1.3 FAULT MODELS                                                                | 13                               |

| 1.3.1 Stuck-at Faults                                                           | 13                               |

| 1.3.2 Bridging Faults                                                           | 14                               |

| 1.4 THE BASICS OF TEST PATTERN GENERATION FOR COMBINATIONAL LOGIC CIRCUITS      | 16                               |

| 1.4.1 The Sensitive Path Concept                                                | 17                               |

| 1.4.2 The Boolean Difference Method                                             | 20                               |

| 1.5 Test Pattern Generation Algorithms                                          | 23                               |

| 1.5.1 The D-Algorithm                                                           | 24                               |

| 1.5.2 PODEM – Path Oriented DEcision Making                                     | 28                               |

| 1.5.3 FAN - Fanout-oriented Test Generation                                     | 31                               |

| 1.5.4 A brief comparison of the D-Algorithm, PODEM and FAN                      | 33                               |

| 1.6 TESTABILITY ANALYSIS                                                        | 34                               |

| 1.7 REFERENCES                                                                  | 36                               |

| CHAPTER 2. TEST PATTERN GENERATION FOR MULTIPLE OUTPUT CIRCUIT                  | ΓS                               |

| USING CUBICAL CALCULUS AND THE BOOLEAN DIFFERENCE                               | 40                               |

| 2.1 Introduction                                                                | 40                               |

| 2.2 TEST PATTERN GENERATION USING BOOLEAN DIFFERENCES                           | 40                               |

| 2.2.1 Single Output Case                                                        | 40                               |

| 2.2.2 Multiple Output Case                                                      | 43                               |

| 2.3 PROPERTIES OF BOOLEAN FUNCTIONS WITH APPLICATIONS TO THE BOOLEAN DIFFERENCE | E43                              |

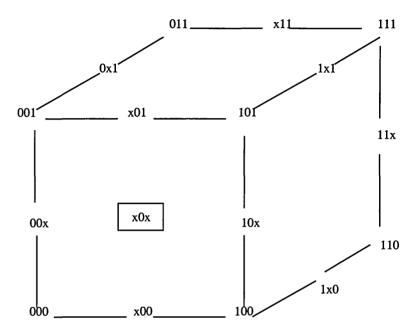

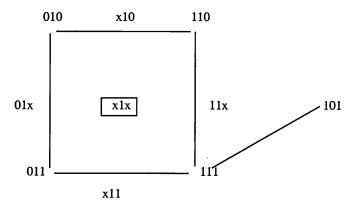

| 2.4 THE CALCULUS OF CUBES                                                       |                                  |

| 2.4.1 Cubical Definitions and Operations                                        | 46                               |

|                                                                                 |                                  |

| 2.4.2 Geometrical Visualisation                                                 | 46                               |

| 2.4.2 Geometrical Visualisation                                                 | 46<br>53                         |

|                                                                                 | 46<br>53                         |

| 2.4.3 Example to Deduce a Minimum Cover of a Function                           | 53<br>55                         |

| 2.4.3 Example to Deduce a Minimum Cover of a Function                           |                                  |

| 2.4.3 Example to Deduce a Minimum Cover of a Function                           |                                  |

| 2.4.3 Example to Deduce a Minimum Cover of a Function                           | 46<br>53<br>55<br>56<br>58<br>61 |

| 2.4.3 Example to Deduce a Minimum Cover of a Function                           |                                  |

| 2.4.3 Example to Deduce a Minimum Cover of a Function                           | 4653555661626262                 |

| 2.4.3 Example to Deduce a Minimum Cover of a Function                           | 465355566162626262               |

| 2.8 REFERENCES                                                                   | 81  |

|----------------------------------------------------------------------------------|-----|

| CHAPTER 3. GENETIC ALGORITHMS                                                    | 83  |

| 3.1 Introduction                                                                 | 83  |

| 3.2 GA TERMINOLOGY                                                               | 84  |

| 3.3 SEARCH SPACES AND FITNESS LANDSCAPES                                         | 85  |

| 3.4 GENETIC ALGORITHM FUNDAMENTALS                                               | 85  |

| 3.4.1 GA Overview                                                                | 85  |

| 3.4.2 The Simple GA - An Example                                                 | 87  |

| 3.5 THE MATHEMATICAL FOUNDATIONS OF GENETIC ALGORITHMS                           | 92  |

| 3.6 GA IMPLEMENTATION ISSUES                                                     | 100 |

| 3.6.1 Encoding Schemes                                                           | 101 |

| 3.6.2 The Fitness Function                                                       | 102 |

| 3.6.3 Selection                                                                  | 104 |

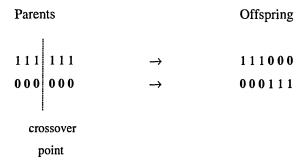

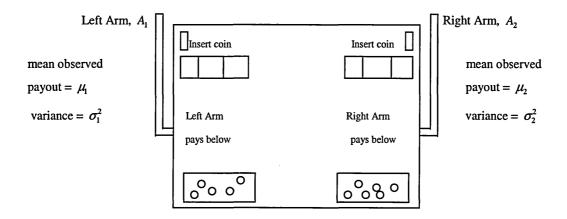

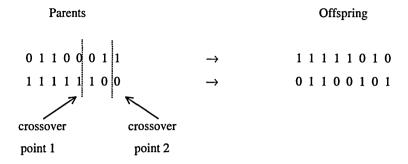

| 3.6.4 Crossover                                                                  | 109 |

| 3.6.5 Mutation                                                                   | 111 |

| 3.6.6 Selection of GA Operator Probabilities                                     | 112 |

| 3.7 GA APPLICATIONS                                                              |     |

| 3.8 SUMMARY                                                                      | 114 |

| 3.9 References                                                                   | 115 |

| CHAPTER 4. THE DERIVATION OF MINIMAL TEST SETS USING GENETIC                     |     |

| ALGORITHMS                                                                       | 120 |

| 4.1 Introduction                                                                 | 120 |

| 4.2 MOTIVATION                                                                   | 120 |

| 4.3 APPLICATION OF GAS IN COMPUTER AIDED DESIGN AND TEST OF INTEGRATED CIRCUITS. | 121 |

| 4.4 A SURVEY OF TEST SET MINIMISATION TECHNIQUES AND ALGORITHMS                  | 123 |

| 4.5 THE MINIMAL TEST SET PROBLEM                                                 | 127 |

| 4.6 GA-MITS : Genetic Algorithm based $MI$ nimisation of $T$ est $S$ ets         | 129 |

| 4.6.1 ATPG Data and the Generation of a Fault Matrix                             | 132 |

| 4.6.2 Encoding Scheme and Chromosome Structure                                   | 133 |

| 4.6.3 The Fitness Function                                                       | 134 |

| 4.6.4 Parent Selection Scheme used in GA-MITS                                    | 135 |

| 4.6.5 Selection of GA Parameters                                                 | 137 |

| 4.6.6 The Use of Inoculation and Elitism                                         |     |

| 4.7 CIRCUITS USED TO GENERATE FAULT MATRICES FOR GA-MITS                         |     |

| 4.8 TYPICAL PERFORMANCE OF GA-MITS                                               |     |

| 4.0 MINIMUSATION DESIGNATION A FAMILY OF SIMPLIFIED DISC DEOCESSORS              |     |

| 4.10 MINIMISATION RESULTS FOR THE ISCAS-85 BENCHMARK CIRCUITS144          |

|---------------------------------------------------------------------------|

| 4.11 GA-MITS DESIGN ISSUES                                                |

| 4.11.1 Inoculation of the Initial Population153                           |

| 4.11.2 The Use of an Exponential Ranking Scheme within GA-MITS157         |

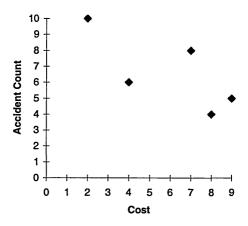

| 4.11.3 Selection of Crossover Operator and Crossover Rate                 |

| 4.11.4 Selection of Mutation Operator and Mutation Rate                   |

| 4.11.5 Selection of Population Size and Number of Generations in a Run167 |

| 4.12 SUMMARY                                                              |

| 4.13 REFERENCES                                                           |

| CHAPTER 5. CONCLUSION AND FURTHER WORK178                                 |

| APPENDIX A. SOFTWARE LISTING: GA-MITS181                                  |

| APPENDIX B. PUBLICATIONS191                                               |

| APPENDIX C. AWARDS                                                        |

# **Chapter 1. Digital Testing**

#### 1.1 Introduction

Over the last three decades, the dramatic advances in VLSI technology have produced tremendous challenges for the test community. As circuits become larger and new fabrication techniques allow increased gate density, the complexity of digital testing increases exponentially. As this work will show, many of the problems in digital testing are NP-hard and as a result, their solution requires a multi-disciplinary approach. Many of these hard problems have been tackled with traditional, established techniques as well as some of the more recent innovations within the fields of computer science, engineering, and mathematics. Historically, digital testing has been a game of 'catch-up' with circuit design and manufacture technology. As soon as one test problem is adequately solved, the blistering pace of VLSI technology introduces new, even more complex problems. This can be seen today with the rapid approach of nanotechnology which seemingly renders traditional testing techniques, such as  $I_{ddq}$  testing, as ineffective [1].

The microprocessor is the most important class of digital circuit and is, by far, the most complex. The microprocessor has changed the very fabric of everyday life in most parts of the world and continues to do so. As digital technology advances, giving rise to higher levels of integration, microprocessors increasingly find themselves in our everyday lives. In the late 1960s and early 1970s, integrated circuits and microprocessors superseded the slide-rule. In the 1980s they gave rise to the personal computer that today, provides more computing power on our desks than was used to put man on the moon. Over the last decade or so, advances in communications, including the internet and mobile technology, have changed the way people interact with one another. Looking ahead, the future for digital devices seems to hold promises of nanotechnology that may be as revolutionary as the microprocessor itself. One of the common threads in technology research has been to make things smaller and faster. Smaller and faster integrated circuits enable smaller and more powerful mobile devices for example. However, it is just this goal that gives rise to the enormous challenges in digital testing.

It is important at this point to understand the seemingly relentless pace of change in VLSI technology as it will offer the reader some perspective as to why digital testing remains such a fertile topic for researchers. This continual change in the semiconductor industry will be discussed in the context of the microprocessor and more specifically, those microprocessors developed by the Intel Corporation. The astounding evolution of this device over the past thirty years will help the reader understand the nature of the industry and the tremendous challenges it poses for the test community.

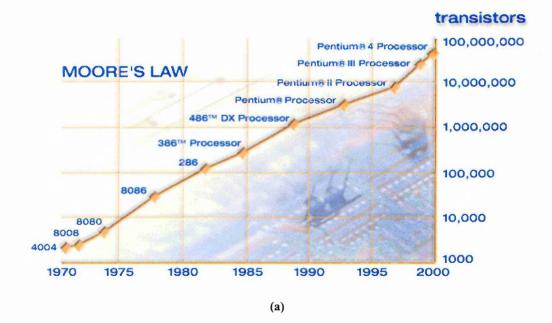

Gordon Moore, founder of the worlds largest microprocessor company Intel Corporation, made a very famous observation about the pace of change in the development and manufacture of integrated circuits. In his now famous paper [2], Moore predicted an exponential growth in transistor density on an integrated circuit and that this trend would continue for some decades. His observation, which was christened *Moore's Law* states,

The number of transistors on an integrated circuit doubles approximately every eighteen months, while the cost of the circuit decreases by half.

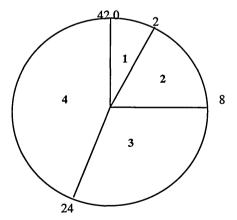

Moore made this prediction four years after the very first integrated circuit was developed in 1961 and over forty years later, his observation still holds true. Figure 1.1 illustrates Moore's Law at work by graphically depicting the number of transistors in Intel's family of microprocessors over the last thirty years or so.

| Processor Name        | Year of introduction | Transistors |

|-----------------------|----------------------|-------------|

| 4004                  | 1971                 | 2,250       |

| 8008                  | 1972                 | 2,500       |

| 8080                  | 1974                 | 5,000       |

| 8086                  | 1978                 | 29,000      |

| 286                   | 1982                 | 120,000     |

| 386™ processor        | 1985                 | 275,000     |

| 486™ DX processor     | 1989                 | 1,180,000   |

| Pentium® processor    | 1993                 | 3,100,000   |

| Pentium II processor  | 1997                 | 7,500,000   |

| Pentium III processor | 1999                 | 24,000,000  |

| Pentium 4 processor   | 2000                 | 42,000,000  |

(b)

Figure 1.1 Moore's Law illustrated by the history of Intel microprocessors. Figure (a) is a curve depicting the data points in (b) and shows the exponential growth in the number of transistors on an integrated circuit. Reproduced courtesy of Intel Corporation.

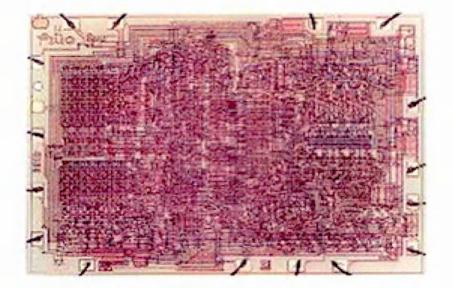

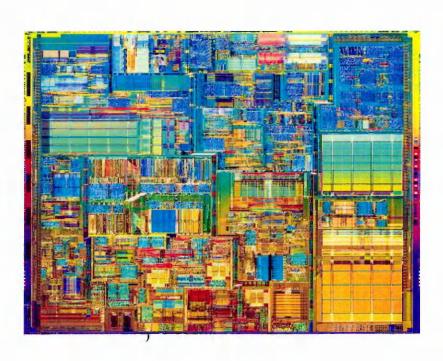

The world's first microprocessor, the Intel 4004 introduced in November 1971, contained 2,250 transistors, ran at a clock speed of 108k Hertz and was able to perform 60,000 calculations per second. The 4004 is shown in diagram 1.2(a). As can be seen from the above curve, the number of transistors increase exponentially over the years and in 2000, Intel introduced the Pentium® 4 processor, which contained 42 million transistors and ran at an initial clock-speed of 1.5G Hertz. The Pentium 4 is shown in Figure 1.2(b). Intel states that, if over the same period, increases in car speeds kept pace with the increases in microprocessor speeds, one could cover the distance from San Francisco to New York (a distance of approximately 3000 miles) in 13 seconds. This fact alone illustrates the astounding developments in VLSI technology and gives some indications of the challenges faced by designers and testers alike.

Moore's law cannot continue forever as we are approaching the limits of physics as we know it. However, there is confidence that integrated circuits will continue to follow the curve for at least another decade with innovations in process and fabrication technology. In fact, Moore himself, as recently as February 2003 gave a presentation entitled, "No exponential is forever... but we can delay it forever" [4], in which he expresses his confidence that the semiconductor industry will overcome many of the challenges that face it over the next decade and continue to pack ever more transistors on an integrated circuit. In fact, in early 2003, Intel introduced the latest in its line of microprocessors, the Pentium 4-M, containing over 70,000,000 transistors.

(a)

(b)

Figure 1.2 (a) Intel 4004 microprocessor containing 2,250 transistors, introduced in 1971. (b) Intel Pentium® 4 microprocessor containing 42,000,000 transistors introduced in 2000. Reproduced Courtesy of Intel Corporation.

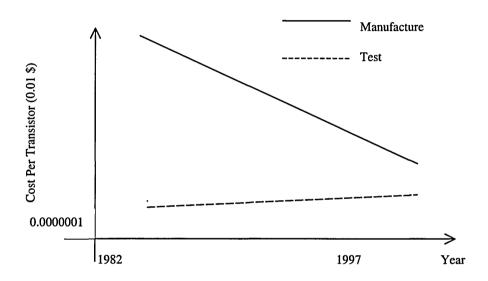

All of this VLSI research and development at the outer edges of our knowledge in such fields as chemistry, physics, engineering and mathematics is to be celebrated. However, these developments pose huge challenges for the test community who are in a continuous race to keep up. The costs associated with testing integrated circuits are huge and are of great concern to the semiconductor industry. In his paper [5] addressing many of the key issues in test, Kenneth Thompson of Intel, estimates his company spends a third of its capital expenditure on test and test equipment and he does not see this percentage decreasing any time soon. As further evidence of the increasing complexity and cost of test, the Semiconductor Industry Association (SIA), a well respected authority on the semiconductor industry, estimates that the cost of testing integrated circuits will actually surpass the cost of their production. The graph given in Figure 1.3 illustrates this.

Figure 1.3 Fabrication and cost trends

Integrated circuits are tested using automatic test equipment (ATE), also referred to as testers. It is the cost of these testers, according to Thompson [5], that represents a large proportion of the overall cost of test. He further states that Intel tests over 50 million microprocessors a year using 300 testers that consume 7.5 megawatts of electricity, enough to power a small town. Testers are very large, complex devices and to give the reader and idea of their size, one from a leading manufacturer of test equipment, Advantest Corporation, is shown in Figure 1.5

#### T6683

Figure 1.5 Automatic Test Equipment, model T6683, Advantest Corporation.

The purpose of test is, of course, to determine whether a circuit is defect-free and functions as intended. Under fault-free conditions, a given set of inputs to a circuit produces a corresponding set of outputs. In many cases, defects in the circuit will result in a deviation from the expected outputs. It is the detection of these deviations that is the central objective of post-fabrication digital testing. A circuit is tested by applying a given set of inputs, known as a test vector, and observing the output. For a given test vector, the fault-free output will be known and if the output deviates from this, a fault ewsawill have been detected in the circuit. The generation of these test vectors is known as test pattern generation. Test patterns are generated with a given fault (or faults) in mind and by generating a set of test vectors, known as a test set, a circuit can be tested for a given percentage of possible faults, known as the fault coverage. Once a test set has been generated, it is applied to an integrated circuit by automatic test equipment (ATE), which essentially observes the output in response to an input vector to determine whether the behaviour is as expected.

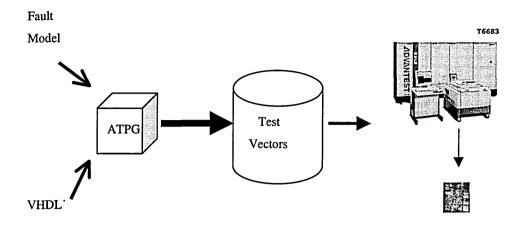

The task of generating test vectors for a circuit is one of the final stages of the overall circuit design life-cycle. Once a circuit design is almost complete, using the description of a circuit and a *fault model*, one is able to generate test vectors. Circuits are often designed using high-level description languages that, much like high-level software language such as C, C++, describe the functionality of a circuit in both machine and human readable form. One of the most widely used languages is VHDL (Very high speed integrated circuit Hardware Description Language) [6] and became an IEEE standard in 1987. Languages such as these enable designers to design and model a circuit. A fault model is an abstraction of physical faults in a circuit and enables engineers to generate tests for these faults (fault models will be discussed later). A description of a circuit and a given fault model are the main inputs to a test pattern generation (ATPG) algorithm. Once a test set has been generated, they are applied to the manufactured circuits by testers to determine whether they function correctly. A high-level depiction of this process is given in Figure 1.4.

**Figure 1.4** High-level description of test pattern generation and test set application for integrated circuits.

As stated above, one of the roles of ATE is to apply test vectors to an integrated circuit and compare the output vectors with the expected outputs for a fault free-circuit. This test may only take a fraction of a second, but when faced with testing many millions of ICs a year, this is a huge cost burden for IC manufacturers. ATE equipment is itself getting quicker, but as ICs increase in complexity and gate density, so do the number of possible faults. This in turn often implies that a larger test set has to be applied by the test equipment to achieve the same level of fault coverage and for a given tester, this inevitably translates to greater test set application time. Again, the test community is faced with the challenges of Moore's Law. Higher test set application times often translate into the need for more test equipment and therefore higher test costs. So, the need to reduce this test application time is critical for IC manufacturers in their continual quest for cost control.

Digital testing is a very large and diverse subject area, encompassing many disciplines. This thesis will describe the original work conducted by the author in three key areas of test; test pattern generation, test set minimisation and testability analysis.

#### Test Pattern Generation and Test Set Minimisation

Test pattern generation [7, 8] and test set minimisation [9] are two of the most important areas within the field of digital testing. Of course the generation of test vectors is necessary in order to actually test a circuit but the generation of high quality test vectors can contribute to lowering the cost of test. Small, optimised test sets, containing high-quality test vectors that achieve high fault coverage will obviously

take less time to apply to a circuit than ones that contain more test vectors. Given the complexity of integrated circuits, the process of actually generating the test patterns, is extremely challenging. The author will present a new technique for generating test patterns for combinational circuits that combines the Boolean difference [10] and cubical calculus [11]. The technique applies to multiple output, combinational circuits using the single-stuck-at fault model. Both the Boolean difference and the cubical calculus have been in existence for a number of decades but the Boolean difference technique has been overlooked within test pattern generation because of its cumbersome, algebraic nature. Cubical calculus is shown to overcome this problem and provides a very competent solution to this problem. Chapter Two will introduce cubical calculus and the Boolean difference and will provide a rigorous discussion on this new test pattern generation technique.

The increasing importance of minimised test sets in lowering test application time has already been discussed above. With this objective in mind, the author has successfully applied an evolutionary algorithm [12] to obtain minimised test sets. Chapter Three presents a detailed survey and analysis of a particular class of evolutionary algorithm known as a *genetic algorithm*. Once the reader has obtained an understanding of this optimisation method, Chapter Four goes on to describe the general problem domain of test set minimisation and the application of a genetic algorithm to solve the problem. The author developed genetic algorithm software to solve this problem for real-world test sets generating by a research group at Tallinn Technical University, Estonia. The data provided by this group and the software written by the author is described in Appendix A.

#### Testability Analysis

Testability analysis provides a means of determining how difficult a circuit would be to test before it is actually manufactured. By performing this analysis during the design stage, circuit designers are able to catch features in a circuit that would make certain faults difficult (or impossible) to detect, resulting in design modifications at an early (and less expensive) stage in the life-cycle of a circuit. Following the work on test pattern generation using cubical calculus and the Boolean difference, a new technique for measuring testability was devised. It was soon realised that much of the core computations in the test pattern generation algorithm could be applied to calculate measures such as *controllability* and *observability* [7]. This work is presented in the final part of Chapter Two and will be shown to make novel use of the Boolean difference and cubical calculus.

The remainder of this chapter will introduce some basic concepts of digital testing and more specifically, test pattern generation, as this area forms the nucleus of the work in this thesis. Once the terminology of the field is introduced, some of the basic ideas behind test pattern generation will be described, some of which have already been mentioned above. Once these preliminary topics have been covered, the final section in this chapter will introduce three of the most important test pattern

generation algorithms that form the basis of many of the commercially available ATPG tools in use today.

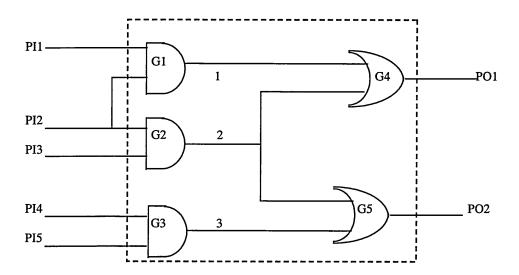

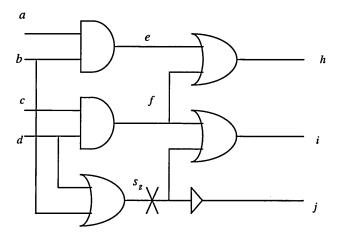

# 1.2 Basic Terminology

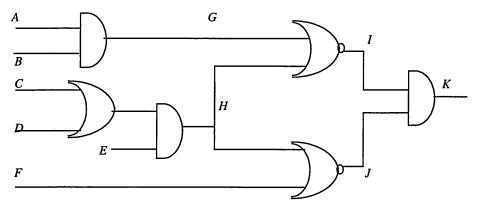

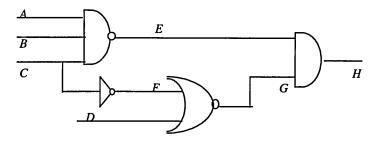

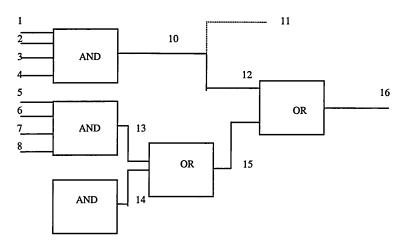

As in most subject areas, there is much jargon and terminology in digital test. Consider the combinational, digital circuit in Figure 1.5. This circuit contains five logic gates; three AND gates, labelled G1 to G3, and two OR gates, labelled G4 to G5. The connections to and from the gates are known as *circuit lines*, *lines* or *nodes*. There are 5 primary inputs, PI1 - PI5 to the circuit and two primary outputs, PO1 and PO2. The *primary inputs/outputs* to the circuit provide a means of connecting the circuit to the external environment. If the circuit were designed as an integrated circuit (IC), it would be contained in a plastic case and the primary inputs/outputs would be the pins of the IC, providing direct access to them.

Figure 1.5 Combinational, digital circuit. The hashed line around the circuit illustrates the casing or packaging of an IC.

This circuit also contains three *internal lines*, labelled 1, 2 and 3 and are the outputs of gates G1, G2 and G3 respectively. There is no direct, external access to these lines as they are completely enclosed within the IC packaging. In some complex IC designs it is deemed necessary to provide external access to some internal lines, to aid the test process, but they are still known as internal lines. A feature present in many digital designs is known as *fan-out* and is when a circuit line is routed into two or more gates. Line 2 is an example of fan-out. The primary input PI2 is another example of fan-out but differs slightly to the fan-out of line 2. In this case one path of the signal PI2 proceeds through gates G2 and G4 and another path is through G1 and G4. The original signal at PI2 recombines at the output of G4, at primary output PO1. This phenomenon of recombination is known as *reconvergent fan-out* and, as will be explained later holds special significance from a digital testing perspective.

Testing a digital circuit such as that given above involves applying sets of values to the primary inputs and comparing the corresponding outputs with the expected behaviour of the circuit. Each set of input values applied to the circuit is known as a *test vector* or *test pattern* and is often referred to as just a *test*. For a given test vector the corresponding, expected output is known as the *fault-free output*. In the above consider applying the values PI1=0, PI2=0, PI3=1, PI4=0, PI5=1. This set of input values produce fault free values at outputs PO1 and PO2 of 0 and 0 respectively. These inputs and the corresponding fault-free outputs constitute the test vector 00101 | 00. The values 00101 to the left of the vertical line correspond to the inputs values at PI1, PI2 and so on and the values to the right correspond to the corresponding output values, PO1 and PO2.

#### 1.3 Fault Models

Circuit defects due to the manufacturing process for example, manifest themselves electrically as faults. In order to compile tests for faults one must establish a fault model that defines the relationship between a defect and a fault. A number of fault models exist and the popular ones will now be discussed.

#### 1.3.1 Stuck-at Faults

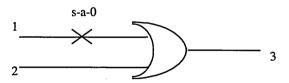

One of the most popular fault models is the stuck-at fault model. In this model a line in a circuit is either permanently set or stuck-at-1 or stuck-at-0. Regardless of the logic value that should be present at the line under normal working conditions, a defect in the circuit has resulted in the line being stuck-at a given logic value. The abbreviations s-a-1 and s-a-0 denote stuck-at-1 and stuck-at-0 respectively. Consider the two input OR gate given in Figure 1.6. Input 1 is stuck-at-0 and when the test vector 10|1 is applied to this gate, the actual output is 0 due the fault. In what conditions would a manufacturing defect result in a stuck-at fault?

Figure 1.6 Two input OR gate.

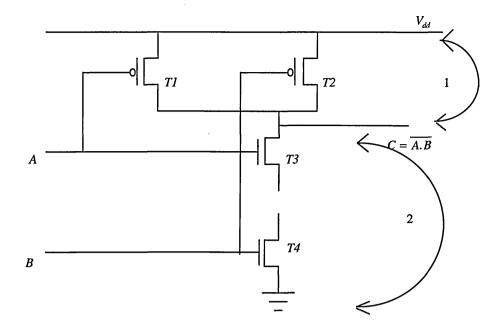

Figure 1.7 shows the CMOS (Complementary Metal-Oxide Semiconductor) implementation of a two input NAND gate [8]. The supply line (power line)  $V_{dd}$  is equivalent to logic 1 and the ground line is equivalent to logic 0. The symbols T1 to T4 represent transistors.

Figure 1.7 CMOS implementation of a two input NAND gate.

The numbers 1 and 2 signify two distinct defects in the circuit. Defect 1 is that the output of the gate has been short circuited with the power rail. This defect will result in the fault C s-a-1. Defect 2 on the other hand is a short circuit between C and the earth rail, resulting in the fault C s-a-0. These short circuit defects are common due to today's manufacturing processes and can be conveniently modelled using the stuck-at fault model.

There are two different stuck-at models. A single stuck-at fault model in which it is assumed that only a single stuck-at fault is present in any given circuit and the multiple stuck-at model [8] which assumes multiple faults in a circuit. The model adopted in the present work is the single stuck-at model and this discussion will therefore be limited to this variant.

#### 1.3.2 Bridging Faults

As integrated circuits become more densely packed with transistors, the probability of short circuits between circuit lines increases. These short circuits produce permanent faults known as *bridging faults* that cannot be modelled as stuck-at faults. Three main types of bridging fault exists. The first is an *input bridging fault* where the primary inputs if a circuit are shorted together. A *feedback bridging fault* occurs if there is a short circuit between the primary output(s) and inputs(s) of a circuit. A *non-feedback bridging fault* is a short circuit that does not fall into one of the two aforementioned categories. Figure 1.8 illustrates the different type of faults.

It must be noted that in general bridging faults are layout dependent and only occur between adjacent circuit lines. They differ from short circuits at the transistor level as described in section 1.3.1.

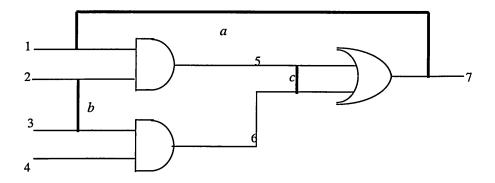

Figure 1.8 Combinational circuit with an input bridging fault between inputs 2 and 3, a feedback bridging fault between output 7 and input 1 and a non feedback bridging fault between lines 5 and 6.

Bridging faults cannot be tested using the stuck-at fault model since the bridged lines are able to assume both logic levels. If under fault free conditions two bridged lines assume the same logic value, then the circuit operation is unaffected. If however they assume complementary values a conflict arises. The actual logic values adopted in such a case depends on the technology used to fabricate the circuit as one logic value will dominate the other. In TTL logic (transistor-transistor logic) logic 0 dominates and if two bridged lines need to assume complementary values, both will be set to 0. In CMOS however, such a concept does not always apply and bridging faults have to be analysed at the transistor level [9, 10]. As this is beyond the scope of the present discussion, the reader is directed towards the references.

For s circuit lines, there is a total of s(s-1)/2 single bridging faults and obviously many more multiple bridging faults. Since the probability of bridging faults is higher for physically adjacent circuit lines, in general only faults between these lines will be tested for as it would be impractical to try and locate all bridging faults.

### 1.3.3 DELAY FAULTS

A number of circuit defects, such as bridging faults, result in faults that affect the logical behaviour of a circuit. Smaller defects such as only partial short circuits, although they may result in correct logical behaviour, often result in disrupting the timing of the circuit. In digital circuits, logic signals flow through the circuit in synchronisation with the clock signal. The correct timing of the signals through the circuit are imperative for the circuit to behave in the desired manner. Any delays in the transition of a signal from logic 0 to 1 or vice versa may disrupt the circuit. It is these transitional delays that are

known as *delay faults*. There are two main types of delay faults, gate delay faults [15] and path delay faults [16]. The main difference between the two models is that the gate delay model can only cope with delays due to single, isolated defects whereas the path delay model can deal with the affects of distributed delays due to a number of defects. Delay faults cannot be tested using the stuck-at fault model as the fault behaviour does not affect the logical operation of a circuit. Other methods for testing delay faults exist and the reader is directed towards the references for further details [8], [17].

#### 1.4 The Basics of Test Pattern Generation for Combinational Logic Circuits.

In general, electronic components and in particular integrated circuits, are very reliable devices. However due to imperfections in the manufacturing process that produce ICs, such as the presence of dust particles in the fabrication plant, faults will occur. Once the IC design has been finalised, the design engineer compiles a test set that may be applied to a device after it has been manufactured, to test for any defects.

For a non-redundant (meaning the function realised by the circuit under fault-free and fault conditions are different) combinational circuit containing n-inputs all faults may be tested by applying all  $2^n$  possible test patterns. This process of *exhaustive testing*, may be realised for small circuits but is impractical for circuits of say, 30 or more inputs. Exhaustive test pattern generation is obviously NP-hard since the number of test patterns increase as two to the power of n, the number of primary inputs. For example to exhaustively test a circuit containing 60 inputs there are  $2^{60}$  possible test vectors. If it were possible to apply 10,000 tests per second it would take approximately 3.5 million years to test a single circuit [8]. In practice however, it is unnecessary to apply all possible test vectors since a single test vector can cover a number of faults. The process of *fault simulation* [18] is used to determine which faults are covered by a given test vector. When the fault coverage of the test patterns has been generated it is possible to calculate the fault coverage of the test set. If there are x possible faults in a circuit and f faults can be detected by the test set, the fault coverage  $f_c$  is given by,

$$f_c = \frac{f}{x}$$

and is often expressed as a percentage. Many test pattern generation algorithms exist and will be discussed later in this chapter. The majority of them assume the single stuck-at fault model and that the circuit is non-redundant. In the following discussion, the single stuck-at fault model for non-redundant circuits will be adopted. At the simplest level, the process of testing a circuit consists of applying successive sets of values to the primary inputs, and of observing the resulting values appearing at the primary outputs. In order to assess the test, the outputs from the tests are compared to the fault-free outputs.

# 1.4.1 The Sensitive Path Concept

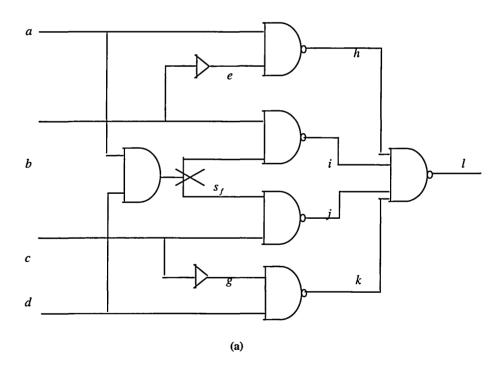

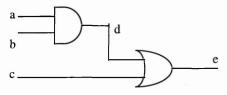

The first task of all test procedures is to compile a fault list, consisting of all the possible faults that can occur. As we are adopting the single stuck-at-fault model, it is assumed that these are the only faults that can occur. A test will then be written which will detect each fault in the fault list. Although each test may be written with the intention of covering one fault, it will invariably turn out in practice that it covers other faults in the list. To illustrate the basic principles of test, the circuit in Figure 1.9 (a) will be used as an example.

| Fault       | Test Pattern | Fault Coverage           |

|-------------|--------------|--------------------------|

| <i>a</i> /0 | 111/1        | a/0, z/0, b/0            |

| <i>a</i> /1 | 011/0        | a/1, z/1                 |

| <i>b</i> /1 | 101/0        | <i>b</i> /1, <i>z</i> /1 |

| etc.        | etc.         | etc.                     |

(b)

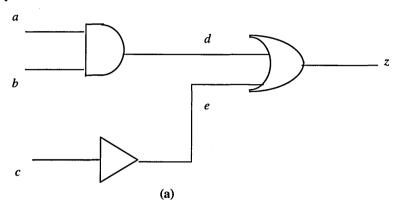

Figure 1.9 (a) Circuit realising the Boolean function  $z = a \ b + \overline{c}$  (b) Partial fault list, test pattern and fault coverage table for (a)

The Fault List

The first task when testing any circuit is to compile a fault list. The fault list for the above circuit is (the abbreviation x/0 means node x is stuck at logic value 0),

Now we have a fault list, tests must be generated to cover each fault.

Testing isolated logic gates, where one has access to its primary inputs and outputs is a trivial task with the use of logic probes. However, it is often the case with combinational circuits that they contain internal nodes that one cannot directly access because they are housed in I.C. casings. In such situations the *sensitive path* concept is central to the testing procedure. The concept ensures that a fault at a node appears at the output of the circuit. If we assume there is an error at input a in Figure 1.9, a path has to be sensitised between it and the output, making the output dependent only on the value of input a. This is achieved by manipulating the values of b, c, d and e.

So, to sensitise the path between a and z, we must first transmit the value at input a to the output of the AND gate (node d) i.e. enable the gate. This is achieved by setting b to 1. Now, to transmit the value of node d through to z, we must enable the OR gate. This is done by setting node e to 0. To set e to 0 we have to work backwards and set node e to 1. So by setting, b=e=1 we have sensitised a path between the input e and the output e.

#### Fault Cover and Test Pattern Generation

Once the fault list has been compiled, tests have to be written to cover each fault. There are two requirements when writing a test.

- i) Establish the fault free condition. So if we are testing whether a node is stuck at 1, we have to set the node at logic value 0.

- ii) Establish a sensitive path between the faulty node and the output.

Let us now write a test pattern for the first fault in the fault list, a/0. The sensitive path has already been calculated for input a, so to test for a/0 the test pattern is a=b=c=1, giving a value of 1 at the output z. The test pattern is written as, 111/1. It was mentioned earlier that some test patterns will cover more than one fault and this is one of them. As we are seeking the logic value 1 at the output z, we are also in effect testing z/0. In a similar manner b/0 is covered. The procedure is now repeated for the remaining faults on the fault list. The table given in Figure 1.9(b) is a partial list of faults and their corresponding test vectors along with each test vector's fault coverage.

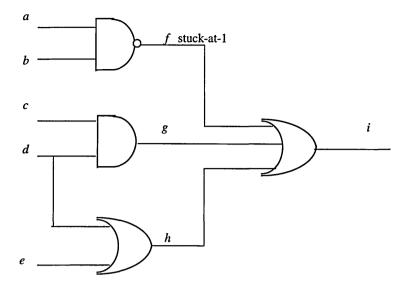

Once the test patterns have been derived for all of the faults a minimal test set is compiled which consists of the minimal number of tests that will cover all of the faults. It is this test set that is used in the final test procedure. As a further example consider a stuck-at-1 fault on line f for the circuit in Figure 1.10. To establish the logic value 0 (complementary to the fault condition) on f, logic values a = b = 1 are required. We must now sensitise a path between line f and the primary output i. To achieve this the we must set g = h = 0. The primary output i is now dependent on the logic value at f. There is one final stage left in the test pattern generation process that was not required in the previous example (due to the simplicity of the circuit) and that is to perform back-propagation (also referred to as back justification) to set the values of the primary inputs c, d and e required to set the appropriate logic

values at g and h. The required logic values are; c = 1 or 0, d = 0, e = 0, giving the test patterns 11100 | 1 and 11000 | 1.

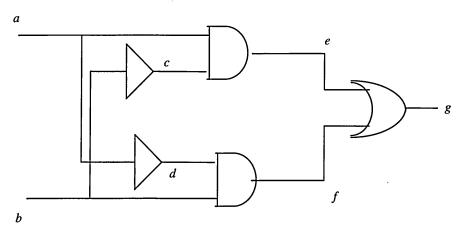

Figure 1.10. Combinational logic circuit with a stuck-at-1 fault at line f.

# Reconvergent Fan-Out and Undetectable Faults

Although most faults that may exist in a circuit can be detected, there are certain topological features that can make faults undetectable or difficult to test. As previously mentioned, testability analysis is a means to allow circuit designers to identify such features in their design before tape-out (i.e. a design is finalised).

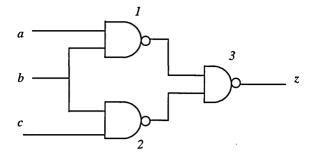

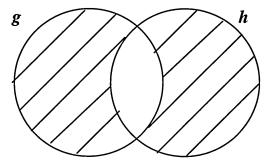

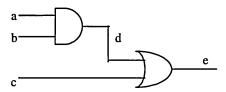

One such feature is known as reconvergent fan-out and is illustrated in Figure 1.11. The signal at input b leads to the two NAND gates i.e it 'fans-out'. The outputs of these two gates then lead to the single NAND gate preceding the output i.e they reconverge. This causes problems as faults are often masked and cannot be detected. To illustrate this point, consider the effect of the fault b/0. Because of the fan-out, the fault will affect the inputs of both gates 1 and 2, and, because of the values assigned to input a and c, the fault is transmitted through both gates, and hence affects both inputs of gate 3, the place of reconvergence. Since gate 3 is a NAND gate, a change of input from 00 to 11 will produce a change of output from 1 to 0, and hence the fault is transmitted through gate 3. In this case, although neither input change alone would have produced a change at the output (since 01 and 10 both give the output as 00), the two acting together result in fault transmission.

Figure 1.11:  $z = \overline{ab}.\overline{bc}$

Redundancy in a circuit can also create undetectable faults [8]. Often when one is seeking to sensitise a path, the situation arises where there are conflicting requirements e.g. a single gate needs to be set at the two logic values. In such cases testing difficulties have arisen because of the failure to minimise a circuit in the design stage.

Although they are not part of the simple stuck-at fault model, bridging faults, where two circuit nodes are accidentally connected together, are often included. Each node in a bridging fault can assume either logic value, the result depends on the type of technology used to implement the circuit. For example, in TTL (Transistor-Transistor Logic), the low node dominates and a high node will be pulled low. If the fault free value of each node is the same, then the circuit operation is unaffected. If however they are different, the fault needs to be detected and rectified. Similar techniques to those used for detecting stuck-at faults such as *sensitised path* are used to detect bridging faults. Unfortunately, as with reconvergent fan-out, some bridging faults are impossible to detect. Not all bridging faults can be included in the fault model. For a few thousand nodes there will be perhaps millions of node pairs. So in practice, only bridging faults involving adjacent nodes or tracks are included.

#### 1.4.2 The Boolean Difference Method

The Boolean difference [8], [10], [11] method of test pattern generation relies on Boolean algebraic descriptions of circuit lines. The Boolean difference is essentially an XOR of two closely related Boolean functions. If g and h are functions then, in the notation of Boolean algebra,

$$g \oplus h \equiv g \overline{h} + \overline{g} h \tag{1}$$

where  $\oplus$  denotes the XOR operation. Consider a Boolean function F(X) of a single output circuit, where  $X = (x_1, \dots, x_n)$  and the variables  $x_1, \dots, x_n$  represent the primary inputs. The Boolean difference of F(X) with respect to  $x_i$  is defined by

$$\frac{dF(X)}{dx_i} = F(x_1, \dots, x_i, \dots, x_n) \oplus F(x_1, \dots, \overline{x}_i, \dots, x_n)$$

(2)

It must be noted that the left hand side of the above equation is not a derivative, it is simply notation to represent the Boolean difference with respect to the primary input  $x_i$ . The most important property of the Boolean difference which forms the basis of its use in test pattern generation is that

$$\frac{dF(X)}{dx_i} = 1\tag{3}$$

if and only if the output of the function F(X) is different for normal and erroneous settings of the primary input  $x_i$ , in which case a fault at the primary input will be detectable, or *observable*, at the primary output. Conversely if

$$\frac{dF(X)}{dx_i} = 0$$

is true then F(X) is logically invariant under normal and erroneous settings of  $x_i$  and a fault in  $x_i$  cannot be detected at the primary output.

The solutions of equation (3) provide the input vectors that propagate a fault on line  $x_i$  to the primary output. A test for  $x_i$  exists if the other inputs can be chosen so that a change of logic value at  $x_i$  produces a change of logic value at the primary output. To actually generate a test vector for  $x_i$  stuckat-0/1, this primary input must first be set to 1/0 and then the fault has to be propagated to the primary output. By performing a logical AND operation between the logic value at the at-fault-line opposite to the fault condition and equation (3) one is able to generate test patterns for stuck-at faults at  $x_i$ . Thus the test vectors for  $x_i$  stuck-at-0 and stuck-at-1 are given by the solutions of equations (4) and (5) respectively.

$$x_i \cdot \frac{dF(X)}{dx_i} = 1 \tag{4}$$

$$\bar{x}_i \cdot \frac{dF(X)}{dx_i} = 1 \tag{5}$$

The above equations (4) and (5) generate test sets for faults at the primary inputs only. However, the ability to generate tests for faults at the internal lines of a circuit is of greater interest. For an internal circuit node,  $s_i$  say, the Boolean difference with respect to  $s_i$  becomes

$$\frac{dF(X,s_j)}{ds_j} = F(x_1,\ldots,x_n,s_j) \oplus F(x_1,\ldots,x_n,\overline{s}_j)$$

where  $s_j$  is regarded as a pseudo primary input [6]. The solution of the Boolean equation

$$dF(X,s_j)/ds_j = 1 (6)$$

provides all the input vectors for which a stuck-at fault on  $s_i$  alters the primary output.

As in the previous discussion, to generate a test vector for  $s_j$  stuck-at-0/1, the node must first be set to 1/0 and the fault propagated to a primary output. An internal node,  $s_j$ , can be expressed as a function of the primary inputs, viz.  $s_j(X) = s_j(x_1, \ldots, x_n)$ , and the solution of the Boolean equation

$$s_{j}(X) = k \tag{7}$$

yields the input vectors that set  $s_j$  to k for k=0,1. The input vectors required to propagate a fault at  $s_j$  to a primary output are given by the solutions to (6) above. To generate test patterns for a fault on  $s_j$ , it is therefore necessary to solve both equations (6) and (7) simultaneously. Hence, for a circuit with n inputs and m outputs, the test sets  $T_0$  and  $T_1$  for  $s_j$  stuck-at-0 and stuck-at-1 respectively are given by the solutions of

$$T_0: s_j(X) \cdot \sum_{i=1}^m \frac{dF_i(X, s_j)}{ds_j} = 1$$

(8)

$$T_{1}: \qquad \overline{s_{j}(X)} \cdot \sum_{i=1}^{m} \frac{dF_{i}(X, s_{j})}{ds_{i}} = 1$$

$$(9)$$

where  $F_i(X)$  denotes the *i*th output, for i=1,...,m.

In order to actually perform the above Boolean calculations, there are a number of Boolean properties which are required. A selection of properties taken from [10] are given below.

$$\frac{Aside}{property(1):}$$

$$\frac{d[F(X) + G(X)]}{dx_i} = \frac{d[F(X) + G(X)]}{dx_i} \oplus \overline{G}(X) \frac{dF(X)}{dx_i} \oplus \frac{dF(X)}{dx_i} \cdot \frac{dG(X)}{dx_i}$$

$$\frac{dG(X)}{dx_i} = F(X) \frac{dG(X)}{dx_i} \oplus G(X) \frac{dF(X)}{dx_i} \oplus \frac{dF(X)}{dx_i} \cdot \frac{dG(X)}{dx_i}$$

$$\frac{dF(X)}{dx_i} = 1 \qquad F(X) \text{ depends only on } x_i$$

#### Example 1.1

Under what conditions will an error in  $x_1$  cause the output to be in error if  $f(x) = x_1x_2 + x_3$ ? Since,

$$F(x) = x_1 x_2 + x_3$$

$$\frac{d}{dx_1} = \overline{x_3} \frac{d(x_1 x_2)}{dx_1} \quad by \ property (1) \ above$$

$$= \overline{x_3} x_2 \frac{d(x_1)}{dx_1} \quad by \ property (2)$$

$$= \overline{x_3} x_2 \qquad by \ property (3)$$

where we have used  $\frac{dx_i}{dx_j} = 0$  if  $x_i$  and  $x_j$  are independent (or if  $i \neq j$ ). The above result means that an error in  $x_1$  will ensure the output is in error if and only if  $\overline{x}_3x_2 = 1$ , i.e.  $x_3 = 0$  and  $x_2 = 1$ . Hence if  $x_1$  is stuck-at-1, we need to set  $x_1 = 0$  and use  $x_2 = 1$ ,  $x_3 = 0$  to detect the fault.

# 1.5 Test Pattern Generation Algorithms

Like all algorithms, the singular goal of test pattern generation algorithms is to apply the fundamental understanding of the domain to create efficient, automatic solutions for generating test patterns. The fundamental understanding of the domain encompasses the behaviour of digital circuits, the different types of defects within a circuit and of course the abstractions and faults models that have been created to conceptualise and test a defect. Given this important understanding of the structure of the problem, it

is left to the researchers to find efficient solutions by use of effective and robust algorithms coupled with efficient organisation of the underlying data through the use of novel data structures.

Given the size and density of integrated circuits, test pattern generation can be a very complex process and is a very active area of research. Many different approaches have been used to efficiently generate test patterns. These approaches include *random* test pattern generation [19], [20] in which the fault coverage for randomly generated test patterns, using fault simulation, is determined and used to form test sets. Pseudo-exhaustive [21] test pattern generation is a technique that tries to generate test patterns by trying to minimize the time required to exhaustively test a circuit by making use of circuit topology and input/output dependencies. Mathematical techniques such as graph methods [22] and statistical methods such as Monte Carlo [23] have also been used. In addition to algorithms based on some of the aforementioned and more traditional areas of mathematics, newer approaches have also been used in test pattern generation. These include evolutionary algorithms [24], [25] and cellular automata [26].

Many of the above mentioned approaches are underpinned by the basic processes of digital test pattern generation as described earlier in this chapter. Path sensitisation, simulation and the use of fault models are central to many ATPG algorithms regardless of their approach. These basic principles, as well as one or two others, were developed over the past two or three decades and form the basis of the early and now fundamental test pattern generation algorithms. Many of the techniques described in the previous paragraph therefore, also find themselves using these basic principles. The three algorithms described below, *The D-Algorithm*, *PODEM* and *FAN*, are widely recognized as the *gold standard* within the field of automatic test pattern generation and as such, must be described in any work on test pattern generation.

#### 1.5.1 The D-Algorithm

The D-algorithm [7], [11], published by John Roth in 1960, is by far the most famous test pattern generation algorithm for combinational circuits and the single stuck-at fault model. Given its age, it still remains as the center piece of the field and other algorithms, including PODEM and FAN are essentially extensions of this seminal work. Roth used many important concepts in his work including the use of cubical complex notation, backtracking, error propagation and line justification. He also employed a five-valued composite logic system where,

X = x/x

1 = 1/1

0 = 0/0

$\mathbf{D} = 1/0$

$\overline{\mathbf{D}} = 0/1$

In the above notation, a/b implies that a is the value of a line under fault-free conditions and b is the value of the line under a fault condition.  $\bf X$  represents 'dont care' or unspecified values. The most interesting notation is the  $\bf D$  notation, which represents a fault on a line, and is central to the algorithm. To detect a stuck-at-0 error on a line one must first set the line to 1, represented by a  $\bf D$ . Given the definition of  $\bf D$  above, this implies the value at the line under fault-free conditions will be 1 and under the fault condition it will be 0. In a similar manner, a stuck-at-1 fault can be represented by a  $\overline{\bf D}$ .

In order to generate a test for a particular fault, the fault line is represented by either  $\mathbf{D}$  or  $\overline{\mathbf{D}}$  (depending on the fault the test is being generated for) with all other lines initially set to  $\mathbf{X}$ . The next step is to sensitise a path from this line to one or more primary outputs of the circuit by setting the unspecified values from  $\mathbf{X}$  to either 1 or 0. This process is known as the *D-drive*. Then there is a backward implication process, starting from the fault line, back to the primary inputs of the circuit. In a similar manner to the D-drive stage, the circuit lines leading to the primary inputs are set to 1 or 0 in order to set the  $\mathbf{D}$  value at the faulty line. If one is able to set the primary inputs of the circuits to either 1 or 0, without conflict, then a test for the fault has been generated.

Before a detailed explanation of the algorithm is given, it is important to examine further, through example, the composite notation and the notion of *singular covers*. A singular cover is a compact representation of a truth table and each row in the cover is known as *a singular cube*. The singular cover for a two input NAND gate is given in Table 1. The truth table in (a) shows that when either (or both) of the inputs is set to 0, the output of a NAND gate is always 1, and when the inputs are both 1, the output is 0. An extended version of this table, using composite logic, is shown in Table 1(b). It illustrates some examples of backward implication. For example, in the *before* table, one row has c set to 0, b set to 1 and a unspecified. Through backward implication, it is obvious that for a NAND gate, a must also be set to 1. Another example in this table shows through backward implication, that b must be set to 0 if both a and c are set to 1. The final truth table in (c) shows that c0 and c1 can imply both backward and forward implication.

| A | b | c |

|---|---|---|

| 0 | х | 1 |

| x | 0 | 1 |

| 1 | 1 | 0 |

|   |   | ı |

(a)

| i              | before | 2 |                | after |   |

|----------------|--------|---|----------------|-------|---|

| $\overline{A}$ | b      | C | $\overline{A}$ | b     | C |

| х              | 1      | 0 | 1              | 1     | 0 |

| 1              | x      | 1 | 1              | 0     | 1 |

|                |        | J |                |       | • |

(b)

| *************************************** |                |                |

|-----------------------------------------|----------------|----------------|

| а                                       | В              | C              |

| 1                                       | D              | $\overline{D}$ |

| D                                       | 1              | $\overline{D}$ |

| D                                       | D              | $\overline{D}$ |

| D                                       | $\overline{D}$ | 0              |

|                                         |                | 1              |

(c)

**Table 1.11 (a)** Truth table for a NAND gate **(b)** truth table illustrating backward implication and **(c)** forward and backward implication.

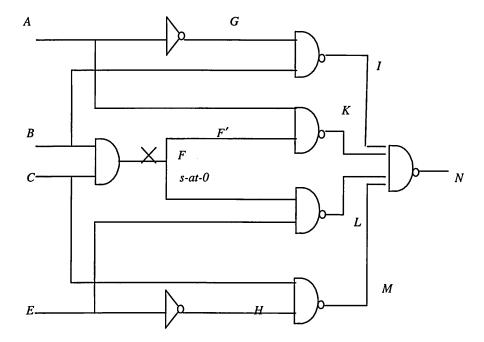

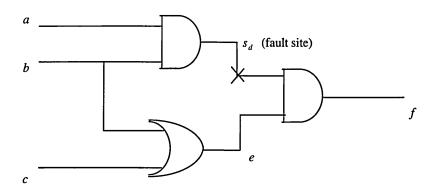

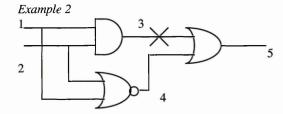

The D-algorithm also employs two key concepts; the *J-frontier* and the *D-frontier*, each being a list of gates that meet given criteria and are used to keep track of forward and backward implications. The J-frontier contains gates for which the output is assigned a logic value that is not implied by its inputs and for which no unique backward implication exists. For example, using the NAND gate as defined above, if a=b=x and c=1 there are three ways to satisfy this output. That is, either a=1, b=0, or a=0, b=1, or a=b=0. Thus, no unique backward implication exists and these gates are candidates for line justification or backward implication. The D-frontier contains gates whose outputs are X and one or more of their inputs are X or X or X or X or X are candidates for D-drive as introduced above. A procedure of imply-and-check is executed each time a line is set to a new value of 1 or 0 to ensure no conflicts have occurred. This procedure carries out all forward and backward implications based on the topology of the circuit. To explain the algorithm further, it will be used to generate a test for the stuckat fault in the circuit given in Figure 1.12

To aid the discussion in the examples, the following notation will be used;

- $P_0$  will denote the circuit line P stuck-at-0

- V(i) will be used to represent a line value  $V \in \{0,1\}$  assigned at a particular step i of the algorithm

Figure 1.12 Combinational circuit with a stuck-at-0 fault at line F

Example 1.2 Using the D-algorithm to generate a test for line F stuck-at-0 in Figure 1.12

The fault will be represented as  $F_0$ .

Step 1. Given the stuck-at-0 fault on F, we must set F=1 and perform the imply-and-check based on this setting. The backward implication of this is that we must set B=C=1. This stage produces the D-frontier  $\{K, L\}$  and the J-frontier  $\phi$ , the empty set.

Step 2. Select a gate from the D-frontier through which to drive the value at F'. Select gate K.

To get D through gate K we need to assign A = 1(1) and we get  $K = \overline{D}$ . Performing the 'imply-and-check' of these settings we see that,

$$G = 0(1)$$

,  $I = 1(1)$ .

- this step produces the D-frontier  $\{L, N\}$  and the J-frontier  $\phi$ .

Step 3. Now need to drive the error  $\overline{D}$  from K to N by selecting a gate from the D-frontier. We select gate N.

To drive the value through the primary output, we need to set L = 1(2) and M = 1(2). Carrying out the imply-and-check we see we require H = 0(2) and I = 1(2) which implies  $L = \overline{D}$  (2) which is a conflict as L has already been set to 1! Given this conflict, the D-algorithm now has to perform its backtracking step. That is, to unset all the values set in the current step (i.e. step 2) and select a different gate from the D-frontier  $\{L, N\}$ .

Step 4. Select gate L.

To drive the value through L we need to assign E = 1. Performing the imply-and-check, we see that,

$$E = 1(2), H = 0(2), M = 1(2)$$

- this step produces the D-frontier  $\{N\}$  and J-frontier  $\phi$ .

Step 5. Drive  $\overline{D}$  through N. This implies I = 1(3). Performing the imply-and-check, we see that,

$$A = 1(3), G = 0(3), N = \mathbf{D}$$

At this point we see that no conflicts exist, the D and J-frontiers are empty which in turn imply that all primary inputs have been set and that the fault has been driven through to the primary output. So a test vector for F stuck-at-0 is,

$$A = B = C = E = 1$$

As can be seen from the above example, the D-algorithm traverses the circuit, continuously driving faults through gates and performing the imply-and-check procedure to ensure no conflicts have occurred or been implied by the D-drive process. If conflicts have occurred, an attempt is made to resolve them through back-tracking, which is just a systematic way of undoing the previous D-drive step and selecting another gate from the D-frontier and attempting the drive process through this new gate. For a given stage in the algorithm, if all gates in the D-frontier result in conflicts then no test exists for that fault. The above example is merely a description of how a test can be generated for one particular fault in one particular circuit. It gives some hints to the algorithm but a formal description of the algorithm is given is Figure 1.13.

#### 1.5.2 PODEM – Path Oriented DEcision Making

The PODEM algorithm, conceived by Goel [27] and published in 1981, is based largely on the D-Algorithm (uses the same notation) and is also a circuit based, fault-oriented test pattern generation algorithm. Goel viewed test pattern generation as a finite space search problem and he staged the problem, "as a search of an *n*-input combinational 0-1 state space of primary input patterns of an *n*-input combinational logic circuit". PODEM is an implicit enumeration algorithm in which all primary input patterns are exhaustively selected and then determined to see whether they are tests for stuck-at

faults in a circuit. The goal of PODEM was to reduce the heavy computational load of the D-Algorithm and achieved it by re-staging the problem in terms of a finite search space.

The D-Algorithm considers every node in a circuit to be part of the search space when trying to locate a test vector for a particular fault. Goel reduced the search space by confining it to include only the primary inputs since all other nodes may be expressed as functions of these.

Suppose we have a set of primary inputs that have been assigned either logic 1 or 0 and we set another primary input p, to logic value 1. As we propagate these primary inputs settings through to the primary output(s), much like the D-drive, and we encounter a conflict, we would only have to set the primary input p to 0 and see whether the conflict has been resolved. If this complimentary value also results in a conflict, this input is removed as a candidate for a test pattern, thus reducing the search space.

```

D-alg

begin

if implyandcheck() = FAILURE then return FAILURE

if(error not at Primary Output (PO) then

begin

if D-frontier = \phi then return FAILURE

repeat

begin

select an untried gate (G) from the D-frontier

c = controlling value at G

assign \bar{c} to every input of G with value x

if D-alg() = SUCCESS then return SUCCESS

until all gates from D-frontier have been tried

return FAILURE

end

/* Error has been propagated to a primary output */

if J-frontier = \phi then return SUCCESS

select a gate (G) from the J-frontier

c = controlling value at G

repeat

begin

select an input (j) of (G) with value x

assign c to j

if D-alg() = SUCCESS then return SUCCESS

assign \bar{c} to j /*reverse decision*/

until all inputs of G are specified

return FAILURE

end

```

Figure 1.13 High-level flow diagram of The D-Algorithm

The back-tracking process in the D-Algorithm is very costly and PODEM reduces the amount of back-tracking that needs to be performed. Undoing previous decisions and performing the *imply-and-check* process with another gate from the D-frontier can be very costly in itself and in the worst case, all

possible choices will have to be tried to resolve a conflict. PODEM attempts to resolve conflicts by resetting primary inputs only and then performing the D-drive process. It is this reduction in search space that gives PODEM the performance advantages over the D-Algorithm which will continually search all nodes in a circuit. In PODEM, as soon as a conflict is encountered, only a subset of the primary inputs need to be reset before the D-drive process is started once more.

When attempting to generate a test, PODEM begins by assigning all primary inputs the value X. It then aims to achieve what is known as an initial objective, which is to set the at-fault node to the opposite value to the fault-condition. The next stage of the algorithm is the backtrace, and this stage aims to obtain primary input assignments given the initial objective. It must then determine whether these primary input assignments have resulted in a conflict with the initial objective through the process of implication (PODEM uses circuit simulation to do this). If no conflicts have been generated, PODEM then selects another primary input and assigns a value to it and performs the simulation again to ensure no conflicts have occurred. If a conflict has occurred through this new setting, this primary input is then set to the complement of the initial setting to see whether this too causes a conflict (again through simulation). If a conflict occurs once more, then this primary input is removed from the search space and is no longer considered in the test generation process. If however, no conflict has occurred with either settings, the process of assigning another primary input repeats until a test has been generated or a conflict occurs or there is no path to propagate the fault to a primary output. The actual propagation to a primary output is performed in a similar manner as the D-Algorithm by searching for a path from the current D-frontier to one or more of the primary outputs. As an illustration of the algorithm, an example from [8] will now be discussed that uses PODEM to generate a test for a stuck-at-0 fault in the circuit in Figure 1.14.

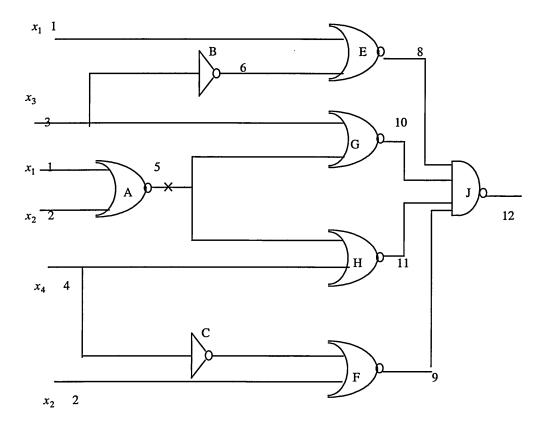

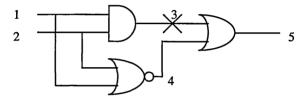

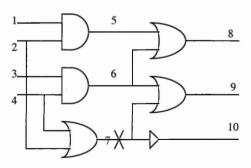

Example 1.3. The use of PODEM to generate a test for line 5 stuck-at-0 for the circuit in Figure 1.14

In the following discussion, the notion of a *net* will be used to describe the circuit topology. A net is essentially a circuit line that either feeds the input of a gate or leads from the output of a gate.

The initial objective is to set the output of gate A to 1. Then it is necessary to backtrace to one or more of the primary inputs. By backtracing, it can be seen that the input  $x_1$  has to be set to 0 ( $x_2$  could also have been selected). This input feeds net 1 so we set net 1 to logic 0.

Because 0XXX is not a test for the fault (determined through simulation), a second iteration of the algorithm is performed and the primary input  $x_2$  is also set to 0 in a similar manner and results in **D** as the output of gate A and hence the value at net 5.

Test Set Generation and Optimisation using Evolutionary Algorithms and Cubical Calculus

Since net 5 is now specified, PODEM will now try to find a gate with D as its input and X as its output towards the primary outputs, in a similar manner to the D-drive of the D-Algorithm. Gates G and H satisfy this condition. Selecting gate G and the subsequent initial condition results in the primary input  $x_3$  being set to 0:

1 2 3 4 5 6 7 8 9 10 11 12

0 0 0 X D 1 X 0 X

$$\overline{D}$$

X X

$x_1$   $x_2$   $x_3$   $x_4$  = 000X is still not a test, so the PODEM must proceed. Given gate J has  $\overline{D}$  on its input net 10, and Xs on input nets 9 and 11, the initial objective is now to set net 12 to logic 1 but we need to select net 9 as the next objective. This results in the primary input  $x_4$  being set to 0 as follows:

Hence, now all primary inputs have been set and the fault can be propagated to a primary output, we have a test vector,  $x_1$   $x_2$   $x_3$   $x_4$  = 0000, for this particular stuck-at-0 fault.

The same test could of course have been found by the D-Algorithm but substantially more trial-and error would have been required due to the number of propagation paths and other consistency operations [8], [27]. Also, for untestable faults, there is much wasted effort when compared to PODEM. It is these features of PODEM and the search space reduction feature described above that gives it significant performance improvements over the D-Algorithm. In some cases, these improvements are an order of magnitude better in terms of both processor time and memory usage [27]. For a deeper explanation of the algorithm, the readers are directed to Goel's paper and a number of undergraduate texts [7], [11].

#### 1.5.3 FAN - Fanout-oriented Test Generation

In 1983, Fujiwara and Shimono [28] published their research which sought to accelerate the test generation algorithms of the day. Their work resulted in a test generation algorithm they named FAN, which was an efficient extension of PODEM. The efficiency is largely due to the fact that FAN uses the concept of multiple backtrace. That is, when backtracking, it does so across multiple paths as opposed to single-path backtracking performed by PODEM. Multiple backtracing reduces the number of backtracks that have to be performed, hence the reduction in computational load.

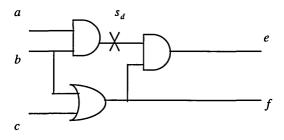

The explanation of the FAN algorithm requires the introduction of new terminology. A bound line is the output of a gate that is part of a reconvergent fan-out loop. A line that is not bound is considered to be free. A headline is a free line that drives a gate that is part of a reconvergent fan-out loop. Let us consider the circuit in Figure 1.15 below. Lines H, I and J are bound lines; A, B, C, D, E, F are free lines and G, H and F are headlines. Because by definition, headlines are free lines, they are considered as primary inputs and can be set arbitrarily. So, during backtrace, if a headline is reached, it as though a primary input has been reached and the backtrace ceases.

Figure 1.14 Combinational circuit with stuck-at-0 at line 5

Figure 1.15 Combinational circuit [8]

Consider the circuit in Figure 1.16 [8]. Lets assume an initial objective to set line H to logic 1, thus testing for H stuck-at-0. PODEM would backtrace to C, D or E. Lets assume the backtrace is done via the path H-E-C which sets E to 1. This would mean C = 0. But, this would result in F being set to 1, G to 0 and G to 0, which fails the initial objective. Now if the backtrace is performed along G instead, the initial objective is achieved. Thus, possibly two or more backtraces would be required by PODEM to achieve the initial objective.

Figure 1.16 Combinational circuit with stuck-at-0 fault on line H

FAN however, backtraces along multiple paths to the fan-out point, along say *H-E-C* and *H-G-F-C* ensuring the value 1 would be set at C, while all along, the initial objective is kept in mind.

Reconvergent fan-outs cause many conflicts when trying to backtrace to primary inputs. Only when FAN has traced all paths to a particular fan-out point, will the actual fan-out stem be assigned a value. PODEM on the other hand will backtrace from an initial objective all the way to a primary input, perform simulation and then detect a conflict if one is present. It is this additional effort that is avoided by FAN. By not proceeding with the backtrace until all paths have been traced to it, FAN is able to avoid conflicts before possibly reaching a primary input and without the need for costly simulation, as required by PODEM.

#### 1.5.4 A brief comparison of the D-Algorithm, PODEM and FAN

The three algorithms above were described in chronological order, PODEM and FAN each being refinements and improvements on their predecessor. The D-Algorithm considers all circuit nodes when trying to generate a test and uses much backtracing and forward justification. The algorithm blindly and stubbornly performs these simulations with little regard for what it has already encountered in terms of conflicts and without foresight of what may lay in ahead in for example, the D-frontier. PODEM tries to address these shortcomings by considering the test generation process as a search in a finite space. By only considering only the primary inputs and by discarding those that do not contribute to a test pattern, effectively reducing the search space, PODEM is able to remember and learn about the circuit topology

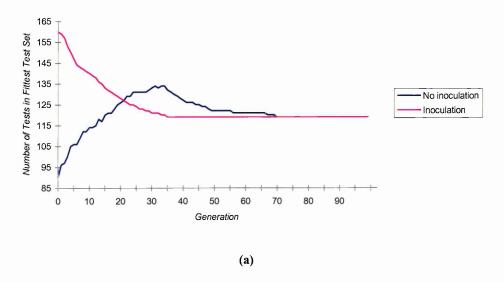

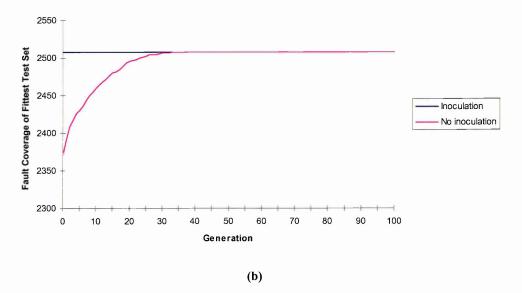

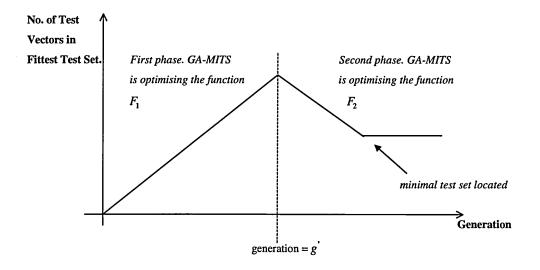

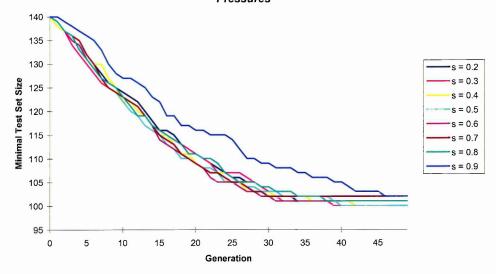

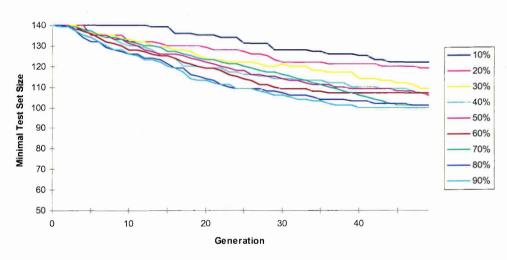

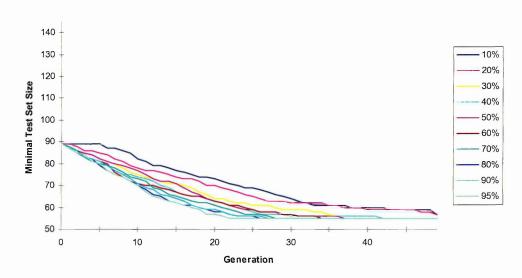

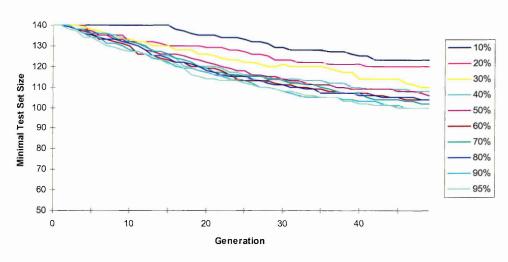

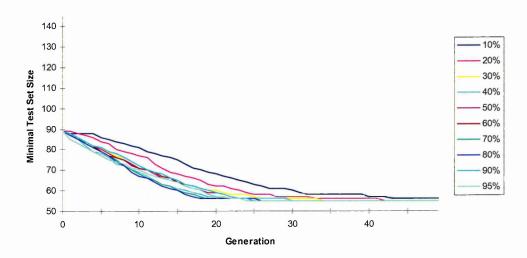

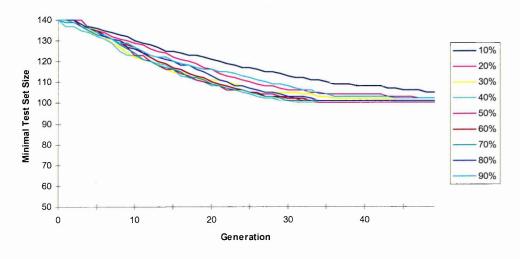

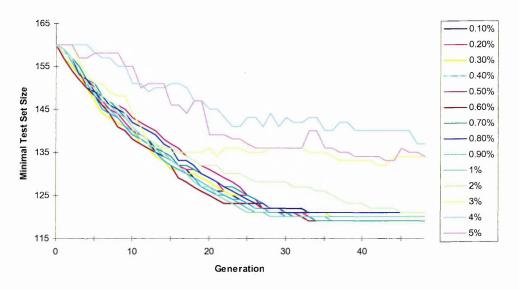

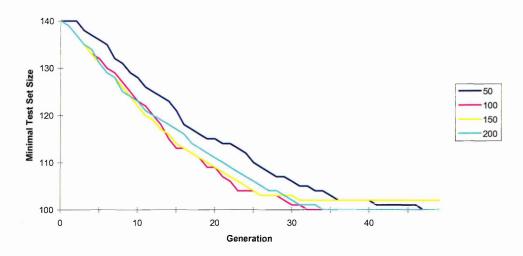

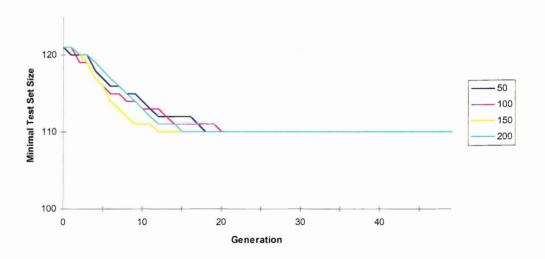

33