Optoelectronic devices based on graded bandgap structures utiliising electroplated semiconductors.

OLUSOLA, Olajide Ibukun-Olu.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/20142/

# A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/20142/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

## Sheffield Hallam University

Author: OLUSOLA. O. I.

Title/Thesis Number: OPTO ELECTRONIC DEVICES ... 28334

Degree Ph.D.

Year: 2016

## Copyright Declaration

# Consultation for Research or Private study for Non Commercial Purposes

I recognise that the copyright in this thesis belongs to the author. I undertake not to publish either the whole or any part of it, or make a copy of the whole or any substantial part of it, without the consent of the author.

I recognise that making quotations from unpublished works under 'fair dealing for criticism or review' is not permissible.

# Consultation for Research or Private study for Commercial Purposes

I recognise that the copyright in this thesis belongs to the author. I undertake not to publish either the whole or any part of it, or make a copy of the whole or any part of it, without the consent of the author. I recognise that making quotations from unpublished works under 'fair dealing for criticism or review' is not permissible.

Readers consulting this thesis are required to complete the details below and sign to show they recognise the copyright declaration.

| Date        | Name and Institution /Organisation (in block letters) | Signature |

|-------------|-------------------------------------------------------|-----------|

|             |                                                       |           |

| <i>11</i> ; | -                                                     |           |

|             |                                                       |           |

|             |                                                       |           |

|             |                                                       |           |

|             |                                                       |           |

|             |                                                       |           |

|             |                                                       |           |

|             |                                                       |           |

ProQuest Number: 10697449

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10697449

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code

Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346 Learning on Information Services Adsetts Centre, City Campus Sheffield St 1WD

102 114 703 6

**REFERENCE**

# Optoelectronic Devices Based on Graded Bandgap Structures Utilising Electroplated Semiconductors

# Olajide Ibukun-Olu Olusola

A thesis submitted in partial fulfilment of the requirements of Sheffield Hallam University for the degree of Doctor of Philosophy

August 2016

Declaration

## **Declaration**

I hereby declare that the work described in this thesis is my own work, done by me and has not been submitted for any other degree anywhere.

OLAJIDE IBUKUN-OLU OLUSOLA

#### Acknowledgement

To God be the glory, honour and adoration for the great things He has done. My sincere appreciation goes to the immediate past Vice-Chancellor of my home university (the Federal University of Technology, Akure (FUTA)), Professor Adebisi M Balogun for nominating me for the Commonwealth Scholarship award. I also want to appreciate the present Vice-Chancellor of FUTA, Professor A.G. Daramola for approving my study leave to pursue this programme. My gratitude also goes to the immediate past Dean of School of Science, FUTA, Professor I.A. Fuwape for recommending me for this award at the faculty level and also for her motherly roles. Dr. S.S. Oluyamo is greatly appreciated for his mentorship, help and for connecting me with my Director of Studies. Professor B. Adeyemi and Professor A. Adebayo are also thanked for their trust to be my guarantor for this award. I appreciate the contributions made by Professor M.T. Babalola, Professor O.S. Ajayi, Professor M.O. Ajewole, Professor A.M. Arogunjo and Dr. K.D. Adedayo towards the success of my academic career. All the staff, the present and the past Heads of Physics Department are acknowledged and appreciated. I am also grateful to the FUTA Director of Academic Planning, Mrs A.O. Adebayo for her motherly role and advice while processing the award. I sincerely appreciate the Commonwealth Scholarship Commission, UK and Sheffield Hallam University for funding this research programme.

My immense gratitude goes to my supervisor and Director of Studies, Professor I.M. Dharmadasa for the excellent training and professional mentorship that he gave me during this research programme. Being a research student under him has really exposed me to the fundamentals of electronics material and device physics. I appreciate the contributions of my second supervisor, Dr. Faris Al-Naemi towards the completion of my PhD programme.

I sincerely appreciate the useful advice and technical discussions of my colleagues (Dr. A.R. Weerasinghe, Dr. O.K. Echendu, Dr. F. Fauzi, Dr. N.A. Abdul-manaf, Dr. H.I. Salim, M.L. Madugu, and A.A. Ojo) in the Electrodeposition arm of Solar Energy Research Laboratory, Sheffield Hallam University. My dear friend, Abubakar Mohammed is greatly appreciated for the technical support he gave in the use of referencing software and MS-Word applications. Thanks to Burak Kadem and Yaqub

#### Acknowledgement

Rahaq for useful academic discussions during this research programme. I appreciate the friendship of A. Ogunsanwo, B. Ayomanor, O. Oluwafemi and O. Ojedokun.

Research collaborators from different research institutes such as Professor T. Druffel, Dr. R. Dharmadasa and their group members from Conn Centre, University of Louisville, USA are acknowledged for performing PL and UPS experiments. Professor M. Dergacheva from Institute of Organic Catalyst & Electrochemistry, Kazakhstan is also thanked for assisting in carrying out AFM measurements. Special thanks to MERI staff; to mention but a few, Professor Doug Cleaver, Professor Nabok Alexei, Professor Chris Sammon, Dr. Paul Bingham, Dr. Aseel Hassan, Dr. Nicholas Farmilo, Gary Robinson, Corrie Houton, Deeba Zahoor, Stuart Creasy, Rachael Toogood, Deborah Durmus, Gillian Hill, Gail Hallewell, Paul Allender, Bob Burton, Dr Tony for their technical and administrative helps during my research programme.

The Pastorate of Mountain of Fire and Miracles Ministries (MFM) Sheffield branch, Pastor and Pastor (Mrs) A. Macgregor, Pastor and Pastor (Mrs) T. Aisida, Pastor and Pastor (Mrs) A. Adewale are greatly thanked for both spiritual and physical support during my sojourn in Sheffield city, UK. I cannot but appreciate the support received from the Prayer and Youth Department of MFM Sheffield headed by Brother Gbenga Odele and Brother Muyiwa Babatunde respectively.

I acknowledge and appreciate the sacrifice of my aged parents, Elder Joshua Olusola Ojo-Eleka and Deaconess Eunice Ademolabi Olusola Ojo-Eleka to give us a befitting education right from our infant days to this present moment. May the good Lord grant you more strength in your old age and may you live long to enjoy the fruits of your labour in Jesus name. I greatly acknowledge the financial support received from my elder brother, Pastor (Dr) K.O. Olusola right from my teenager to this present time. Special thanks also go to all my family members, Mr and Mrs Johnson Oladeji, Pastor (Dr) and Deaconess Kolapo Olusola, Dr (Mrs) and Pastor Abioye Ayorinde, Pastor (Dr) and Dr (Mrs) Joshua Aransiola, Pastor and Mrs Femi Olusola, Mr and Mrs Wole Olusola, Mr and Mrs Seun Olusola and my in-laws. God bless you all.

Mr and Mrs Segun Olusola are also acknowledged for their supports. To my beloved wife, Olanike J. Olusola, I appreciate her support and encouragement throughout my stay in United Kingdom and during the PhD thesis writing stage. God bless you richly in Jesus name. Finally, I thank everyone who has assisted me in one way or the other and contributed positively to my success in life. Thanks and may God bless you all.

## **Dedication**

This research work is dedicated to the Almighty God, the Father of our Lord Jesus Christ for His salvation, protection, guidance and for seeing me through in my research work.

### **List of Publications**

#### **Journal Publications**

- 1. **O.I.** Olusola, O.K. Echendu, I.M. Dharmadasa, Development of CdSe thin films for application in electronic devices, J. Mater. Sci. Mater. Electron. 26 (2015) 1066–1076. doi:10.1007/s10854-014-2506-x.

- 2. N.A. Abdul-manaf, H.I. Salim, M.L. Madugu, **O.I. Olusola**, I.M. Dharmadasa, Electro-Plating and Characterisation of CdTe Thin Films Using CdCl2 as the Cadmium Source, Energies. 8 (2015) 10883–10903. doi:10.3390/en81010883.

- 3. **O.I. Olusola**, M.L. Madugu, I.M. Dharmadasa, Growth of n- and p-type ZnTe semiconductors by intrinsic doping, Mater. Res. Innov. 19 (2015) 497–502. doi:10.1080/14328917.2015.1105570.

- 4. **O.I. Olusola**, M.L. Madugu, N.A. Abdul-Manaf, I.M. Dharmadasa, Growth and characterisation of n- and p-type ZnTe thin films for applications in electronic devices, Curr. Appl. Phys. 16 (2016) 120–130. doi:10.1016/j.cap.2015.11.008.

- M.L. Madugu, O.I. Olusola, O.K. Echendu, B. Kadem, I.M. Dharmadasa, Intrinsic Doping in Electrodeposited ZnS Thin Films for Application in Large-Area Optoelectronic Devices, J. Electron. Mater. (2016). doi:10.1007/s11664-015-4310-7.

- H.I. Salim, O.I. Olusola, A.A. Ojo, K.A. Urasov, M.B. Dergacheva, I.M. Dharmadasa, Electrodeposition and characterisation of CdS thin films using thiourea precursor for application in solar cells, J. Mater. Sci. Mater. Electron. (2016). doi:10.1007/s10854-016-4629-8.

- D.G. Diso, F. Fauzi, O.K. Echendu, O.I. Olusola, I.M. Dharmadasa, Optimisation of CdTe electrodeposition voltage for development of CdS/CdTe solar cells, J. Mater. Sci. Mater. Electron. (2016). doi:10.1007/s10854-016-4844-3.

- 8. **O.I.** Olusola, H.I. Salim, I.M. Dharmadasa, One-sided rectifying p-n junction diodes fabricated from n-CdS and p-ZnTe:Te semiconductors, Mater. Res. Express. 3 (2016) 95904. doi:doi:10.1088/2053-1591/3/9/095904.

- 9. I.M. Dharmadasa, O.K. Echendu, F. Fauzi, N.A. Abdul-Manaf, **O.I. Olusola**, H.I. Salim, M.L. Madugu, A.A. Ojo, Improvement of composition of CdTe thin

- films during heat treatment in the presence of CdCl<sub>2</sub>, J. Mater. Sci. Mater. Electron. (2016). doi:10.1007/s10854-016-5802-9.

- A.A. Ojo, H.I. Salim, O.I. Olusola, M.L. Madugu, I.M. Dharmadasa, Effect of thickness: a case study of electrodeposited CdS in CdS/CdTe based photovoltaic devices, J. Mater. Sci. Mater. Electron. (2016). doi:10.1007/s10854-016-5916-0.

#### **Conference Proceedings**

- 1. **O.I. Olusola**, P.A. Bingham, S. Creasey and I.M. Dharmadasa, Schottky Barrier Formation at Au and Electro-plated n-CdSe Interface, in: Proc. of PVSAT-10, Loughborough University, Loughborough, UK, (2014) (Poster).

- O.I. Olusola, H.I. Salim, I.M. Dharmadasa, Fabrication of Rectifying p-n Junction Diodes from Heterogeneous n-CdS and p-ZnTe Semiconductors, UK Semiconductors & UK Nitrides Consortium Summer Meeting, Sheffield, United Kingdom, 9-10 July, 2014, pp. 103 (Oral Presentation).

- 3. Olajide I. Olusola, Vinay Patel and I.M. Dharmadasa, Optimisation of pH for Electrodeposition of n-CdSe Thin Films for Applications in Photovoltaic Devices, in: Proc. of 29<sup>th</sup> European Photovoltaic Solar Energy Conference and Exhibition, Amsterdam, The Netherlands, (2014) pp. 1852-1856. DOI: 10.4229/EUPVSEC20142014-3DV.2.49 (Poster).

- 4. M. L. Madugu, P. A. Bingham, H. I. Salim, **O. I Olusola** and I. M. Dharmadasa, Development of In<sub>x</sub>Se<sub>y</sub> Buffer Layers for Applications in CdTe Based Thin Film Solar Cells, in: Proc. of 29<sup>th</sup> European Photovoltaic Solar Energy Conference and Exhibition, Amsterdam, The Netherlands, (2014) pp. 1847-1851. DOI: 10.4229/EUPVSEC20142014-3DV.2.48 (Poster).

- 5. **O.I. Olusola**, M.L. Madugu and I.M. Dharmadasa, Growth of n- and p- type ZnTe Semiconductors by Intrinsic Doping, in: Proc. of PVSAT-11, University of Leeds, Leeds, UK, (2015) pp. 141–144 (Poster).

- 6. H.I. Salim, **O.I. Olusola** and I.M. Dharmadasa, Cathodic electrodeposition of CdS thin films from thiourea precursor for solar cell applications, in: Proc. of PVSAT-11, University of Leeds, Leeds, UK, (2015) pp. 149–152 (Poster).

- 7. **O.I. Olusola**, M.L. Madugu, I.M. Dharmadasa, Development of n- and p-type ZnTe Semiconductors for application in Electronic Devices, UK

- Semiconductors & UK Nitrides Consortium Summer Meeting, Sheffield, United Kingdom, 1-2 July, 2015, pp. 130 (Poster).

- 8. **O.I. Olusola**, M.L. Madugu, I.M. Dharmadasa, Improvement of CdS/CdTe Solar Cell Parameters using ZnS Buffer Layer, in: Proc. of PVSAT-12, University of Liverpool, Liverpool, UK, (2016) pp. 107–110 (Oral Presentation). <a href="http://www.pvsat.org.uk/proceedings/">http://www.pvsat.org.uk/proceedings/</a>.

#### **Submitted articles for Publication**

- 1. **O.I. Olusola**, M.L. Madugu, I.M. Dharmadasa, Investigating the electronic properties of multi-junction ZnS/CdS/CdTe graded bandgap solar cells, Submitt. to J. Mater. Chem. and Phys. (2016).

- 2. **O.I. Olusola**, M.L. Madugu, A.A. Ojo, I.M. Dharmadasa, Investigating the effect of GaCl<sub>3</sub> incorporation into the usual CdCl<sub>2</sub> treatment on CdTe-based solar cell device structures, Submitt. to J. Curr. Appl. Phys. (2016).

- I.M. Dharmadasa, M.L. Madugu, O.I. Olusola, O.K. Echendu, F. Fauzi, D.G. Diso, A.R. Weerasinghe, T. Druffel, R. Dharmadasa, B. Lavery, J.B. Jasinski, T.A. Krentsel, G. Sumanasekera, Electroplating of CdTe Thin Films from Cadmium Sulphate Precursor and Comparison of layers grown by 3-electrode and 2-electrode systems, Submitt. to Coatings. (2016).

- 4. A.A. Ojo, **O.I. Olusola**, I.M. Dharmadasa, Effect of the inclusion of gallium in normal cadmium chloride treatment on electrical properties of CdS/CdTe solar cell, Submitt. to J. Mater. Chem. and Phys. (2016).

#### **Abstract**

The main aim of the work presented in this thesis is to develop low-cost multi-junction graded bandgap solar cells using electroplated semiconductors. The semiconductor materials explored in this research are CdSe, ZnTe, CdS, CdMnTe and CdTe thin films. These layers were characterised for their structural, compositional, morphological, optical, and electrical features using XRD, Raman spectroscopy, EDX, SEM, UV-Vis spectroscopy, PEC cell, C-V, I-V and UPS measurement techniques respectively. The summary of the results depict that CdSe and CdS semiconductors have hexagonal crystal structures and are mainly n-type in electrical conduction within the explored range of deposition potentials. The crystal structures of ZnTe thin films are hexagonal and the electroplated ZnTe thin films have both n- and p-type electrical conduction. In the literature, the electrical conductivity type of ZnTe thin films has been reported to be p-type. In this work, the developments of n-type ZnTe thin films have been successfully achieved for the first time by using intrinsic doping. Also, the fabrication of p-n homo-junction diodes from intrinsically doped electroplated ZnTe layers have been developed for the first time. Results from analytical techniques showed that CdTe and CdMnTe thin films have cubic crystal structures and can exist as n- and p-type materials. The semiconductor materials investigated in this work have been used for solar cells fabrication. Some of the device structures explored are based on p-n hetero-junction solar cells fabricated from CdS/ZnTe hetero-structure and combination of n-n hetero-junction plus large Schottky barrier (n-n+SB) solar cells fabricated from CdS/CdTe hetero-structure. The highest efficiency obtained for the pn junction solar cell with device structure glass/FTO/n-CdS/p-ZnTe/Au was ~5.3% while the highest efficiency reported in this work for n-n+SB solar cells with device structure glass/FTO/n-CdS/n-CdTe/Au was ~7.6%. Multi-junction graded bandgap solar cells with different device structures were also fabricated in this research work. The two most important solar cells in this category are n-n-n plus large Schottky barrier (n-n-n+SB) solar cells fabricated from glass/FTO/n-ZnS/n-CdS/n-CdTe/Au device structures and n-n-p solar cells fabricated from glass/FTO/n-CdS/n-CdTe/p-CdTe/Au device structures. The n-n-p device structure is a combination of one n-n hetero-junction and one n-p homo-junction interface. The experimental investigations carried out on the effect of thickness of p-CdTe on n-n-p device structures showed that thinner p-CdTe layer of ~35 nm is most appropriate to be used in the n-n-p solar cells device configuration. The highest efficiency obtained for the n-n-p solar cell device structures was ~10.9% while the highest efficiency obtained for the n-n-n+SB solar cell device structures was  $\sim 12.8\%$  with an active area of  $\sim 0.031$  cm<sup>2</sup>.

| Declaration                                                                       |

|-----------------------------------------------------------------------------------|

| Acknowledgementii                                                                 |

| Dedicationiv                                                                      |

| List of Publicationsv                                                             |

| Journal Publicationsv                                                             |

| Conference Proceedingsvi                                                          |

| Submitted articles for Publicationvii                                             |

| Abstractviii                                                                      |

| Table of Contentsix                                                               |

| List of Figuresxvii                                                               |

| List of Tablesxxxii                                                               |

| Chapter 1 - Introduction 1                                                        |

| 1.1 Energy and its universal importance                                           |

| 1.2 Energy sources                                                                |

| 1.2.1 Non-renewable energy sources                                                |

| 1.2.2 Renewable energy sources                                                    |

| 1.3 Solar energy                                                                  |

| 1.4 Solar spectrum                                                                |

| 1.5 Air mass                                                                      |

| 1.6 Photovoltaic technology6                                                      |

| 1.6.1 Energy of photons6                                                          |

| 1.6.2 Brief history of photovoltaic technology                                    |

| 1.6.3 Brief history of CdTe-based solar cell                                      |

| 1.6.3.1 Principle of operation of substrate and superstrate device configurations |

| 1.7 Present challenges in CdTe-based solar cell device structures                 |

| 1.8 Research Aim and Objectives                                                   |

| 1.9 Summary                                                                       |

| References                                                                        |

| Chapter 2 - Semiconductor materials, solar cell interfaces and types of solar cells23 | 3 |

|---------------------------------------------------------------------------------------|---|

| 2.1 Introduction                                                                      | 3 |

| 2.2 Solid materials                                                                   | 3 |

| 2.3 Semiconductor materials                                                           | 1 |

| 2.3.1 Classification of semiconductor materials based on dopants addition             | 1 |

| 2.3.1.1 Intrinsic and extrinsic semiconductor materials                               | 5 |

| 2.3.2 Classification of semiconductor materials based on elemental composition        | 3 |

| 2.4 Types of junctions/interfaces in solar cell devices                               | ) |

| 2.4.1 Homo-junction and Hetero-junction                                               | ) |

| 2.4.2 p-n junction                                                                    | ) |

| 2.4.3 One-sided p-n junction                                                          | l |

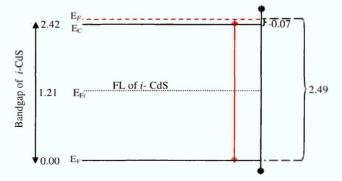

| 2.4.4 p-i-n interface                                                                 | ) |

| 2.4.5 n-n and p-p interfaces                                                          | 3 |

| 2.4.6 Metal-Semiconductor (MS) interface                                              | ŀ |

| 2.4.6.1 Ohmic contacts formation                                                      | ŀ |

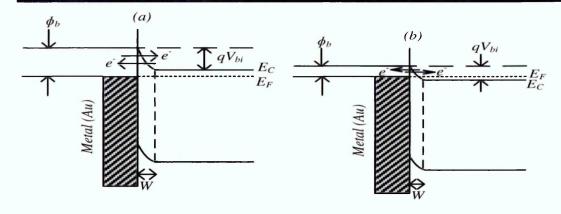

| 2.4.6.2 Rectifying contacts formation                                                 | 5 |

| 2.4.6.3 Current transport mechanisms in Schottky diodes                               | ) |

| 2.4.7 Metal-insulator-semiconductor interfaces                                        |   |

| 2.5 Types of solar cells                                                              | ) |

| 2.5.1 Inorganic solar cells                                                           | ; |

| 2.5.2 Organic solar cells                                                             | } |

| 2.5.3 Hybrid solar cell (Perovskite solar cell)                                       | ļ |

| 2.5.4 Multi-junction graded bandgap solar cells                                       | í |

| 2.6 Summary                                                                           | ) |

| References                                                                            | ) |

| Chapter 3 - Techniques for materials growth, materials and device                     |   |

| characterisation52                                                                    | , |

| 3.1 Introduction                                                                      |   |

| 3.2 Substrate selection and preparation                                               | , |

| 3.3 Electrodeposition growth technique53                                              |   |

| 3.4 Cyclic Voltammetry                                                                | 1 |

|     | 3.5 Techniques used for material characterisation                                                                                                                                                                                                                                                                                                       | 57                                            |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

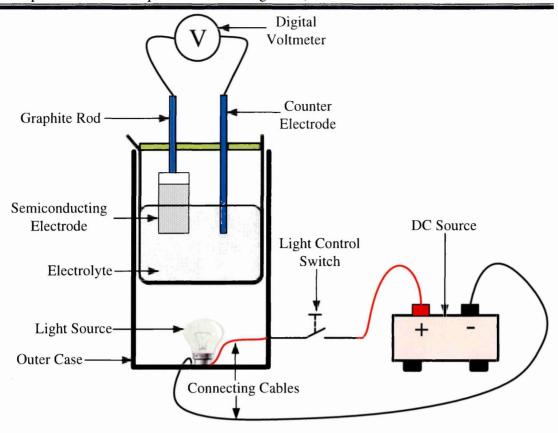

|     | 3.5.1 Photoelectrochemical cell measurement                                                                                                                                                                                                                                                                                                             | 57                                            |

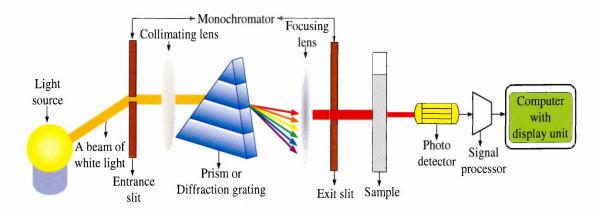

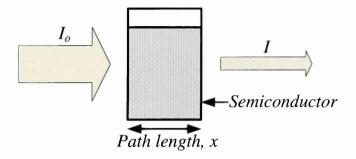

|     | 3.5.2 UV-Vis Spectrophotometry                                                                                                                                                                                                                                                                                                                          | 60                                            |

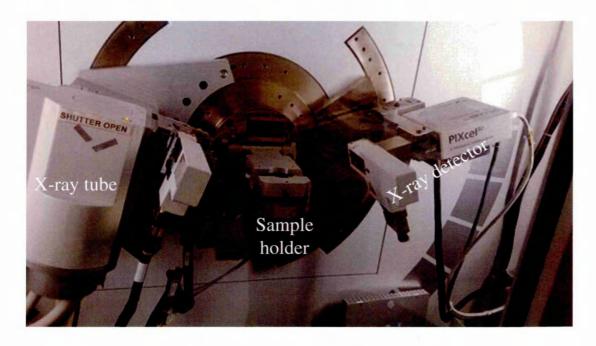

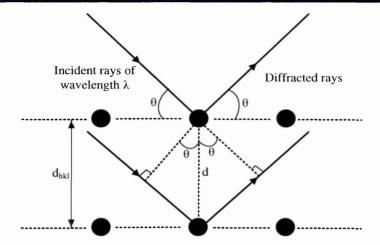

|     | 3.5.3 X-ray diffraction (XRD)                                                                                                                                                                                                                                                                                                                           | 63                                            |

|     | 3.5.4 Raman spectroscopy technique                                                                                                                                                                                                                                                                                                                      | 66                                            |

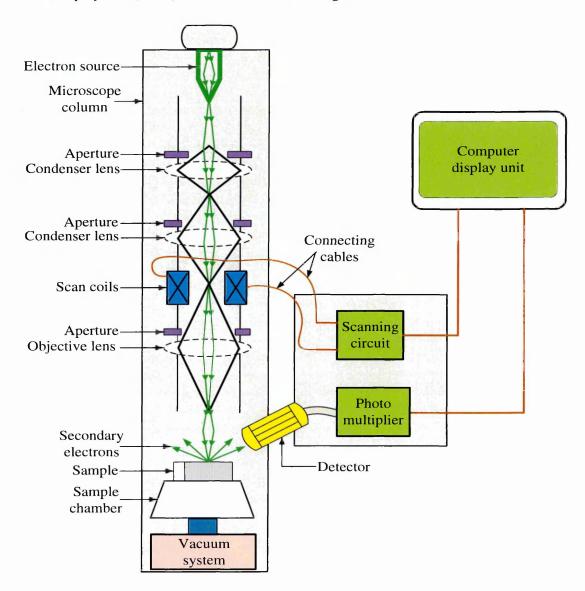

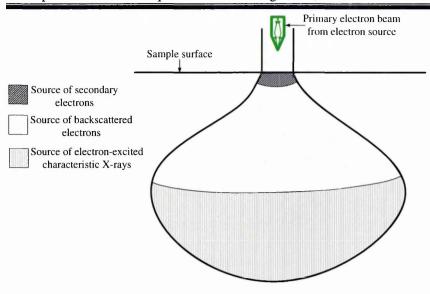

|     | 3.5.5 Scanning electron microscopy technique                                                                                                                                                                                                                                                                                                            | 66                                            |

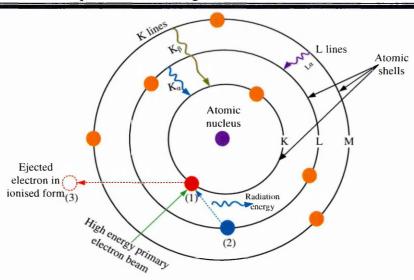

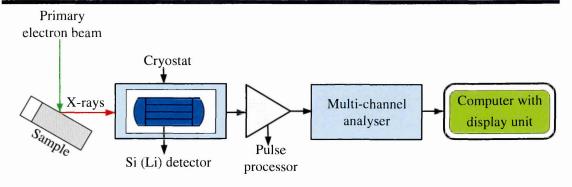

|     | 3.5.6 Energy Dispersive Spectroscopy (EDS)                                                                                                                                                                                                                                                                                                              | 70                                            |

|     | 3.5.7 Ultra-violet photoelectron spectroscopy (UPS)                                                                                                                                                                                                                                                                                                     | 72                                            |

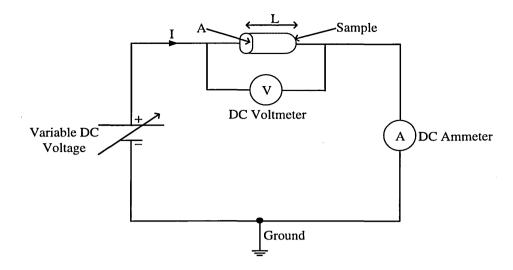

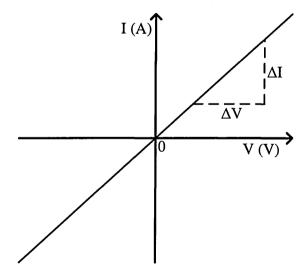

|     | 3.5.8 Direct current (DC) conductivity measurement                                                                                                                                                                                                                                                                                                      | 73                                            |

|     | 3.6 Analytical techniques for device characterisation                                                                                                                                                                                                                                                                                                   | 75                                            |

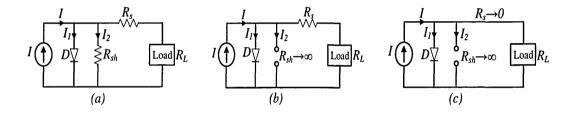

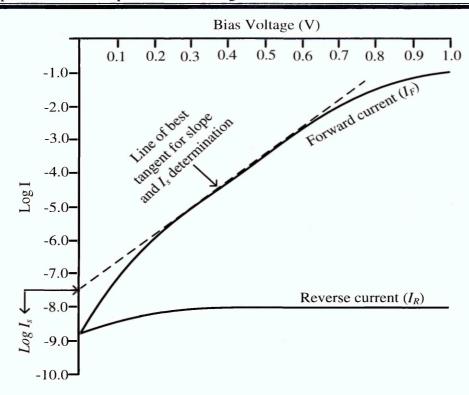

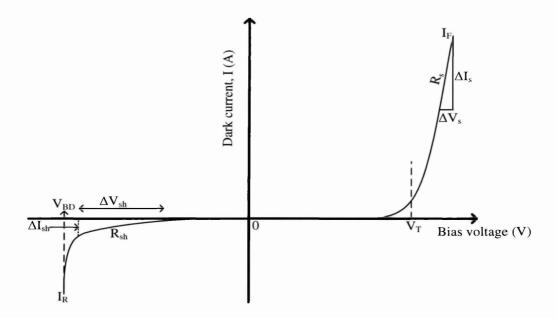

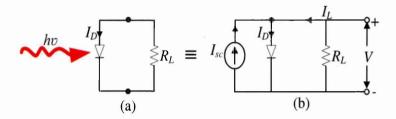

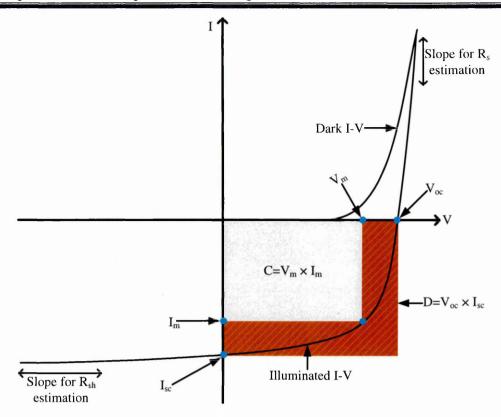

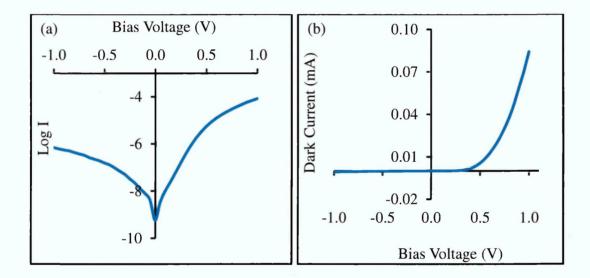

|     | 3.6.1 I-V characteristics of a typical thin film solar cell                                                                                                                                                                                                                                                                                             | 75                                            |

|     | 3.6.1.1 I-V characteristics of solar cell under dark condition                                                                                                                                                                                                                                                                                          | 77                                            |

|     | 3.6.1.2 I-V characteristics of solar cell under illumination                                                                                                                                                                                                                                                                                            |                                               |

|     | condition                                                                                                                                                                                                                                                                                                                                               | 82                                            |

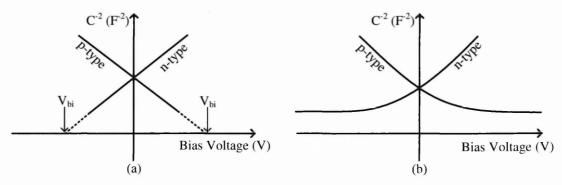

|     | 3.6.2 Capacitance-voltage (C-V) technique                                                                                                                                                                                                                                                                                                               | 84                                            |

|     | 3.7 Summary                                                                                                                                                                                                                                                                                                                                             | 89                                            |

|     | References                                                                                                                                                                                                                                                                                                                                              | 90                                            |

|     | References                                                                                                                                                                                                                                                                                                                                              | ,                                             |

| Cha | pter 4 - Growth and characterisation of CdSe thin films                                                                                                                                                                                                                                                                                                 |                                               |

| Cha |                                                                                                                                                                                                                                                                                                                                                         | 94                                            |

| Cha | pter 4 - Growth and characterisation of CdSe thin films                                                                                                                                                                                                                                                                                                 | <b> 94</b><br>94                              |

| Cha | pter 4 - Growth and characterisation of CdSe thin films                                                                                                                                                                                                                                                                                                 | 94<br>94<br>94                                |

| Cha | <ul> <li>4.1 Introduction</li> <li>4.2 Preparation of CdSe electrolytic bath</li> <li>4.3 Voltage optimisation and growth of CdSe thin films</li> </ul>                                                                                                                                                                                                 | 94<br>94<br>94                                |

| Cha | <ul> <li>4.1 Introduction</li> <li>4.2 Preparation of CdSe electrolytic bath</li> <li>4.3 Voltage optimisation and growth of CdSe thin films</li> </ul>                                                                                                                                                                                                 | 94<br>94<br>94<br>95                          |

| Cha | <ul> <li>4.1 Introduction</li> <li>4.2 Preparation of CdSe electrolytic bath</li> <li>4.3 Voltage optimisation and growth of CdSe thin films</li> <li>4.3.1 Cyclic voltammogram</li> </ul>                                                                                                                                                              | 94<br>94<br>95<br>95<br>95                    |

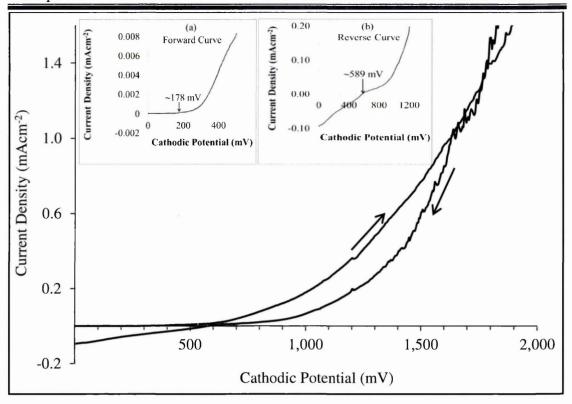

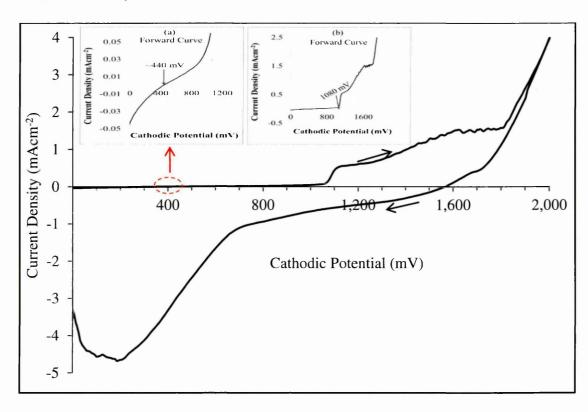

| Cha | 4.1 Introduction                                                                                                                                                                                                                                                                                                                                        | 94<br>94<br>95<br>95<br>95                    |

| Cha | 4.1 Introduction  4.2 Preparation of CdSe electrolytic bath  4.3 Voltage optimisation and growth of CdSe thin films  4.3.1 Cyclic voltammogram  4.3.1.1 Cyclic voltammogram of 0.3M CdCl <sub>2</sub>                                                                                                                                                   | 94<br>94<br>95<br>95<br>95<br>96              |

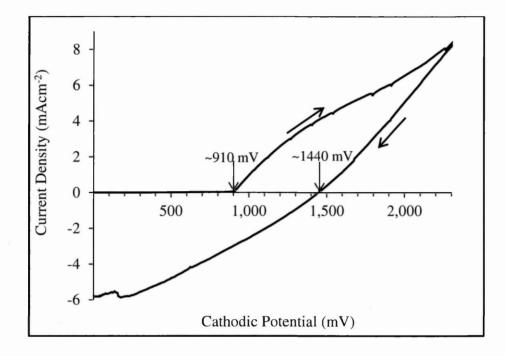

| Cha | 4.1 Introduction  4.2 Preparation of CdSe electrolytic bath  4.3 Voltage optimisation and growth of CdSe thin films  4.3.1 Cyclic voltammogram  4.3.1.1 Cyclic voltammogram of 0.3M CdCl <sub>2</sub> 4.3.1.2 Cyclic voltammogram of 0.003M SeO <sub>2</sub> 4.3.1.3 Cyclic voltammogram of mixture of 0.3M CdCl <sub>2</sub> + 0.003M SeO <sub>2</sub> | 94 94 95 95 95 96 97 99                       |

| Cha | 4.1 Introduction                                                                                                                                                                                                                                                                                                                                        | 94 94 95 95 95 96 97 99                       |

| Cha | 4.1 Introduction                                                                                                                                                                                                                                                                                                                                        | 94 94 95 95 96 97 99 99                       |

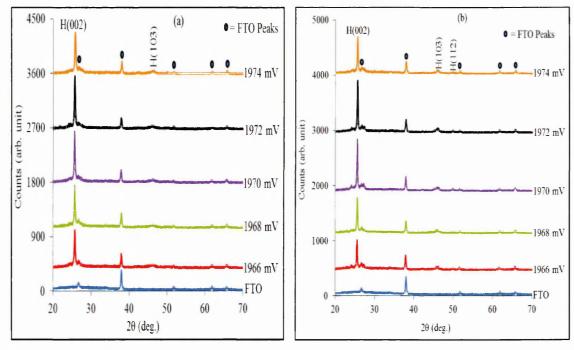

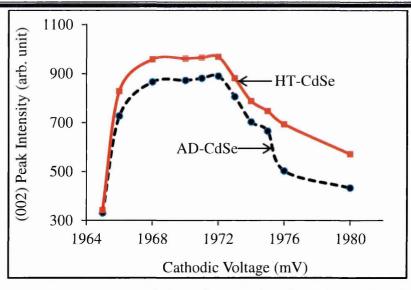

| Cha | 4.1 Introduction                                                                                                                                                                                                                                                                                                                                        | 94 94 95 95 95 96 97 99 99 . 102 . 103        |

| Cha | 4.1 Introduction                                                                                                                                                                                                                                                                                                                                        | 94 94 95 95 95 96 97 99 99 . 102 . 103 . 104  |

| Cha | 4.1 Introduction                                                                                                                                                                                                                                                                                                                                        | 94 94 95 95 95 96 97 99 102 . 103 . 104 . 105 |

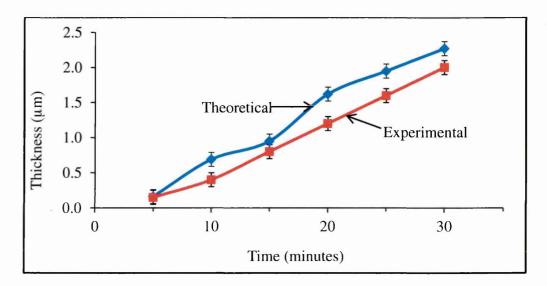

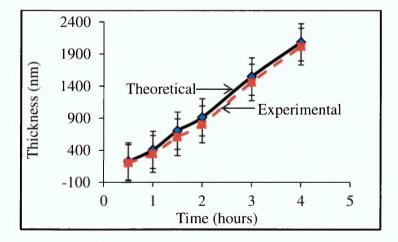

| 4.3.7 Thickness of ED-CdSe layers                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.4 pH optimisation of CdSe thin films                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

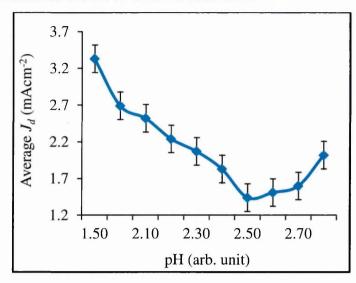

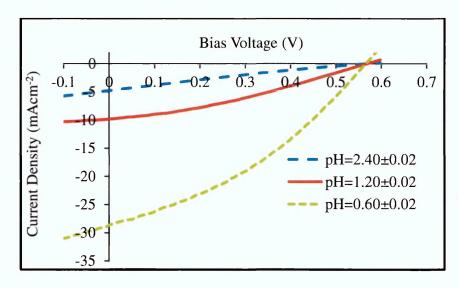

| 4.4.1 Effect of pH variation on deposition current density 109                                                                                                                                                                                                                                                                                                                                                                                                                                       |

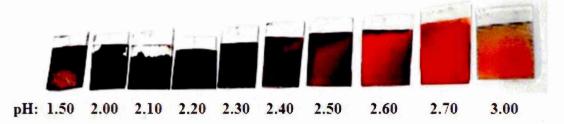

| 4.4.2 Effect of pH on the visual appearance of electrodeposited CdSe layers                                                                                                                                                                                                                                                                                                                                                                                                                          |

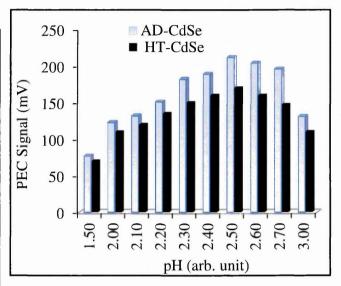

| 4.4.3 Effect of pH variation on the electrical conductivity type of ED-CdSe                                                                                                                                                                                                                                                                                                                                                                                                                          |

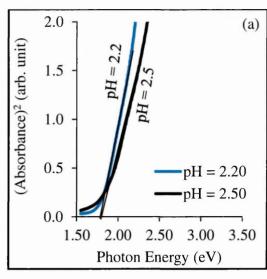

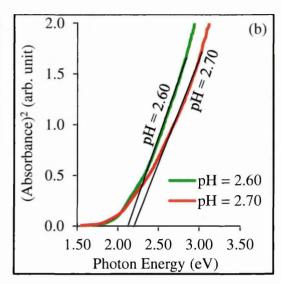

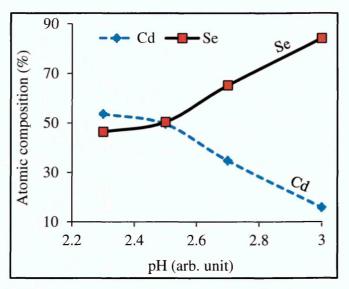

| 4.4.4 Effect of pH variation on the optical properties of CdSe thin films                                                                                                                                                                                                                                                                                                                                                                                                                            |

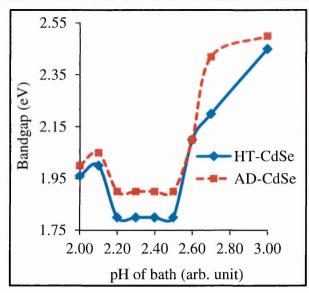

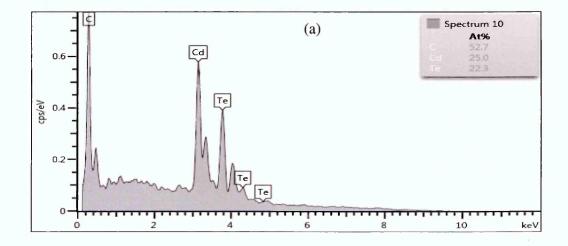

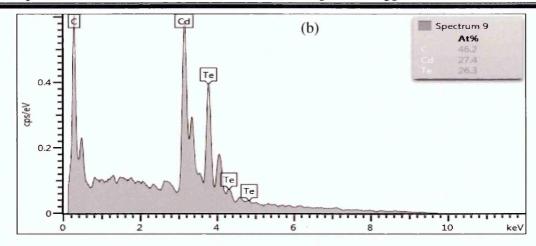

| 4.4.5 Effect of pH variation on the compositional properties CdSe thin films                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.5 Testing the electronic quality of CdSe thin films                                                                                                                                                                                                                                                                                                                                                                                                                                                |

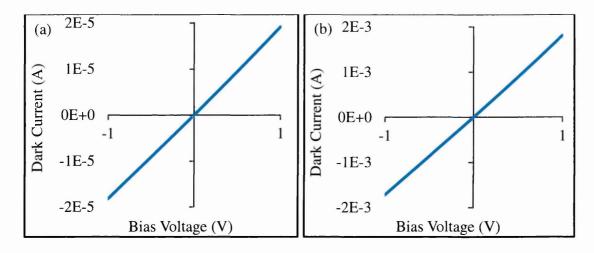

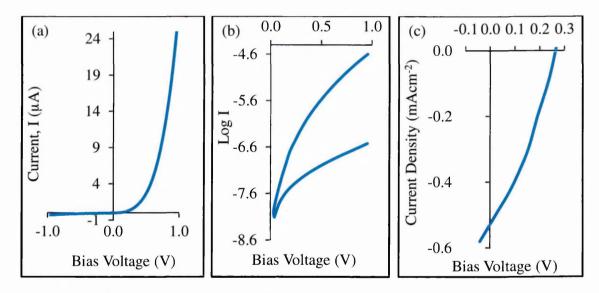

| 4.5.1 Ohmic behaviour of electrodeposited n-CdSe layers 115                                                                                                                                                                                                                                                                                                                                                                                                                                          |

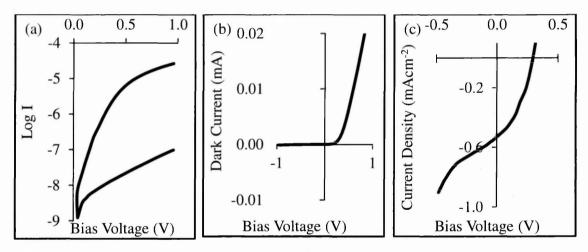

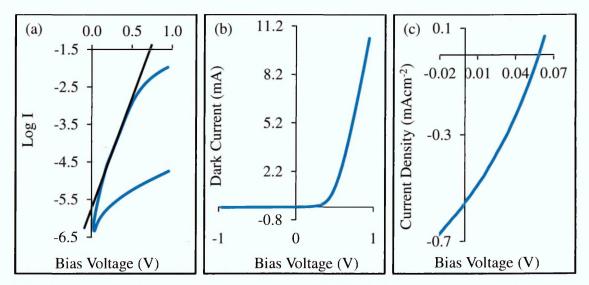

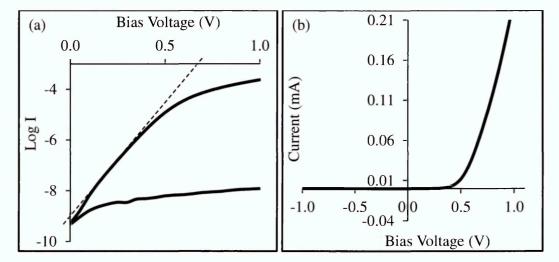

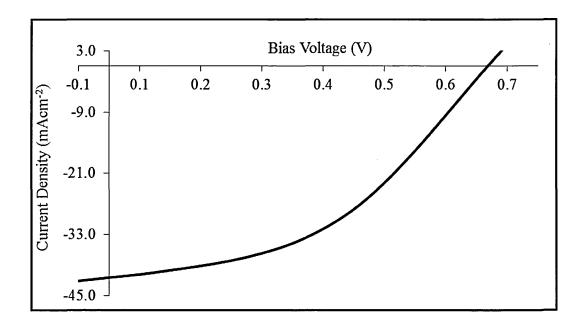

| 4.5.2 Rectifying behaviour of electrodeposited n-CdSe layers 117                                                                                                                                                                                                                                                                                                                                                                                                                                     |

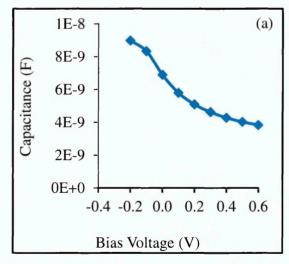

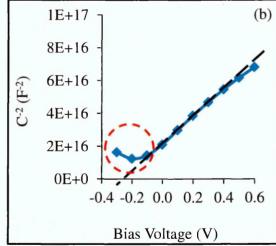

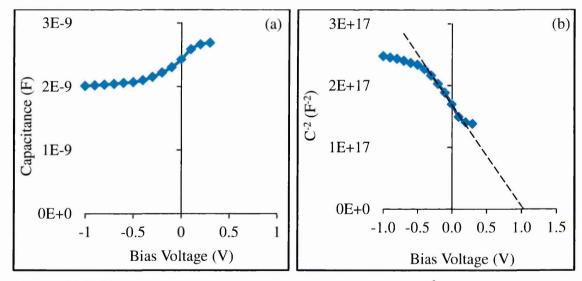

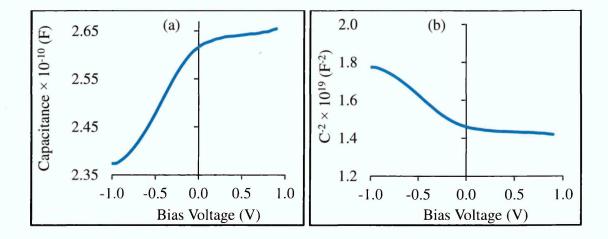

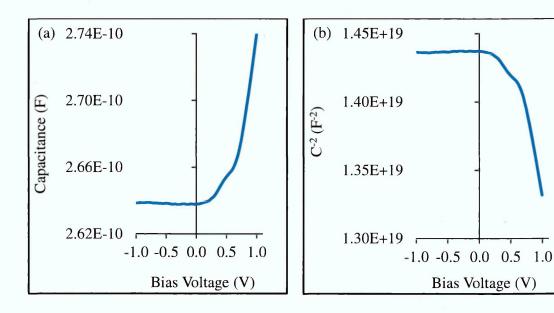

| 4.5.3 Capacitance-voltage measurement of n-CdSe Schottky diodes 119                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.6 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 5 - Growth and characterisation of ZnTe thin films 126                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

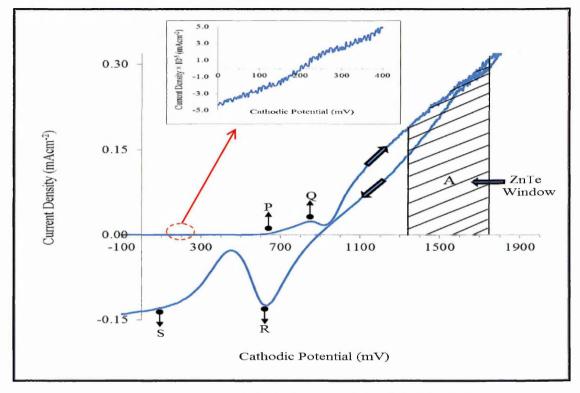

| 5.1 Introduction1265.2 Preparation of ZnTe electrolytic bath1275.3 Voltage optimisation and growth of ZnTe thin films1285.3.1 Cyclic voltammogram1285.3.2 Structural Analysis130                                                                                                                                                                                                                                                                                                                     |

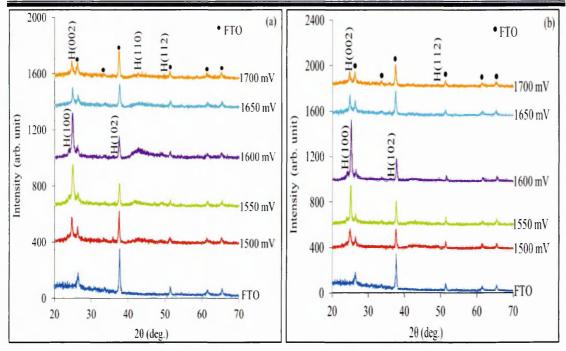

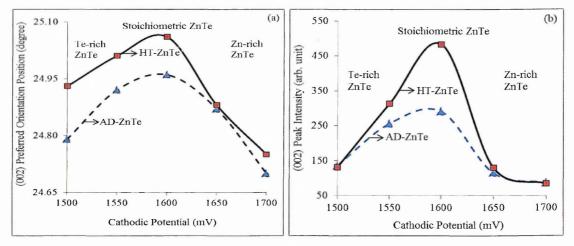

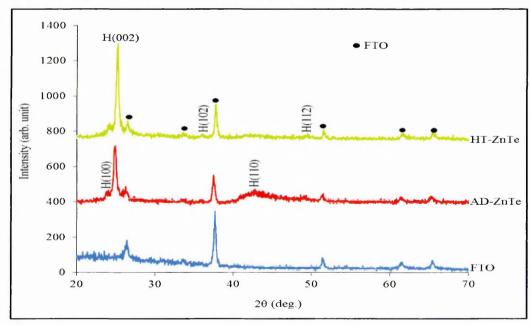

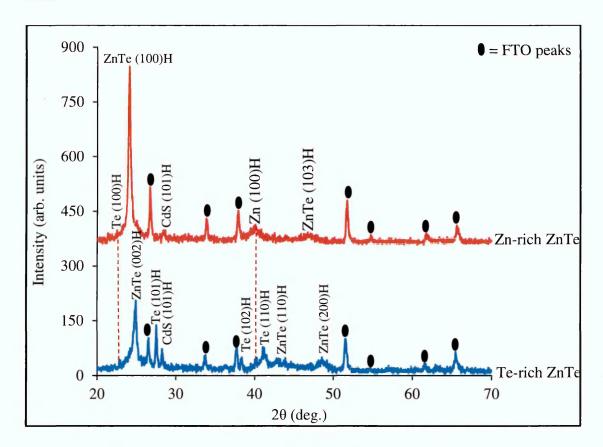

| 5.1 Introduction1265.2 Preparation of ZnTe electrolytic bath1275.3 Voltage optimisation and growth of ZnTe thin films1285.3.1 Cyclic voltammogram1285.3.2 Structural Analysis1305.3.2.1 X-ray diffraction studies130                                                                                                                                                                                                                                                                                 |

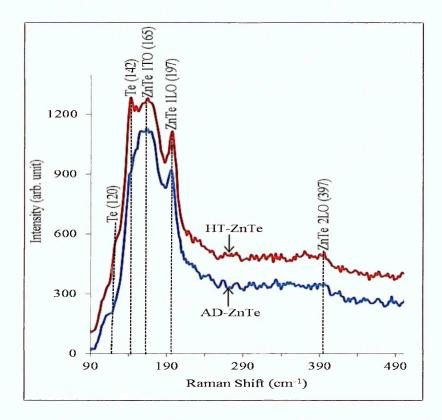

| 5.1 Introduction1265.2 Preparation of ZnTe electrolytic bath1275.3 Voltage optimisation and growth of ZnTe thin films1285.3.1 Cyclic voltammogram1285.3.2 Structural Analysis1305.3.2.1 X-ray diffraction studies1305.3.2.2 Raman spectroscopy134                                                                                                                                                                                                                                                    |

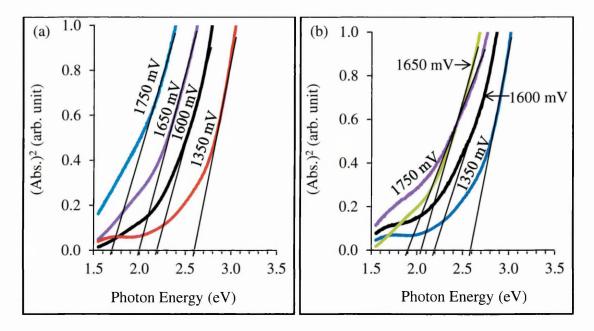

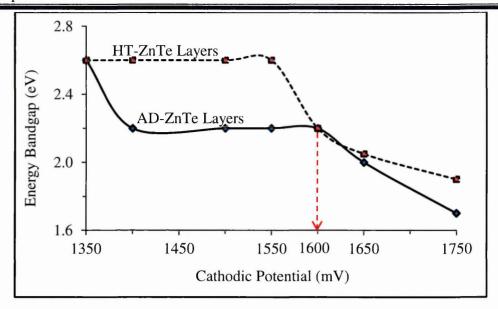

| 5.1 Introduction1265.2 Preparation of ZnTe electrolytic bath1275.3 Voltage optimisation and growth of ZnTe thin films1285.3.1 Cyclic voltammogram1285.3.2 Structural Analysis1305.3.2.1 X-ray diffraction studies1305.3.2.2 Raman spectroscopy1345.3.3 Optical absorption studies135                                                                                                                                                                                                                 |

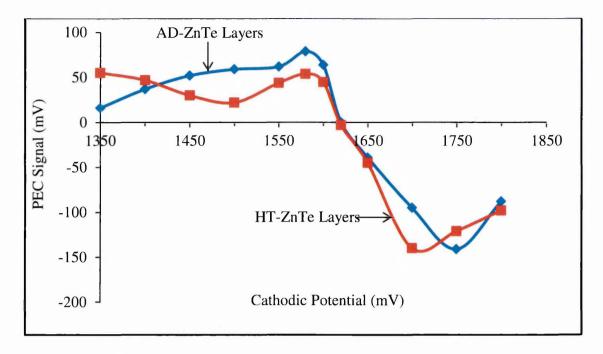

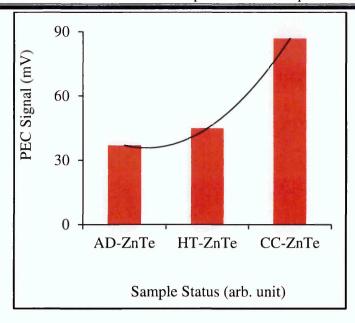

| 5.1 Introduction1265.2 Preparation of ZnTe electrolytic bath1275.3 Voltage optimisation and growth of ZnTe thin films1285.3.1 Cyclic voltammogram1285.3.2 Structural Analysis1305.3.2.1 X-ray diffraction studies1305.3.2.2 Raman spectroscopy1345.3.3 Optical absorption studies1355.3.4 Photoelectrochemical cell measurements137                                                                                                                                                                  |

| 5.1 Introduction1265.2 Preparation of ZnTe electrolytic bath1275.3 Voltage optimisation and growth of ZnTe thin films1285.3.1 Cyclic voltammogram1285.3.2 Structural Analysis1305.3.2.1 X-ray diffraction studies1305.3.2.2 Raman spectroscopy1345.3.3 Optical absorption studies1355.3.4 Photoelectrochemical cell measurements1375.3.5 Morphological Analysis138                                                                                                                                   |

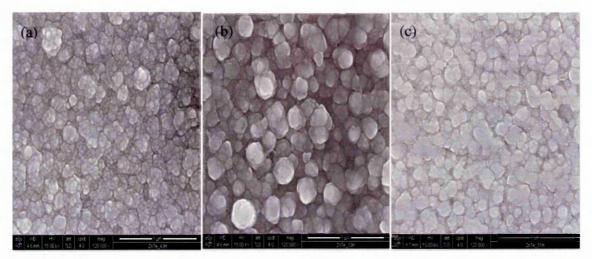

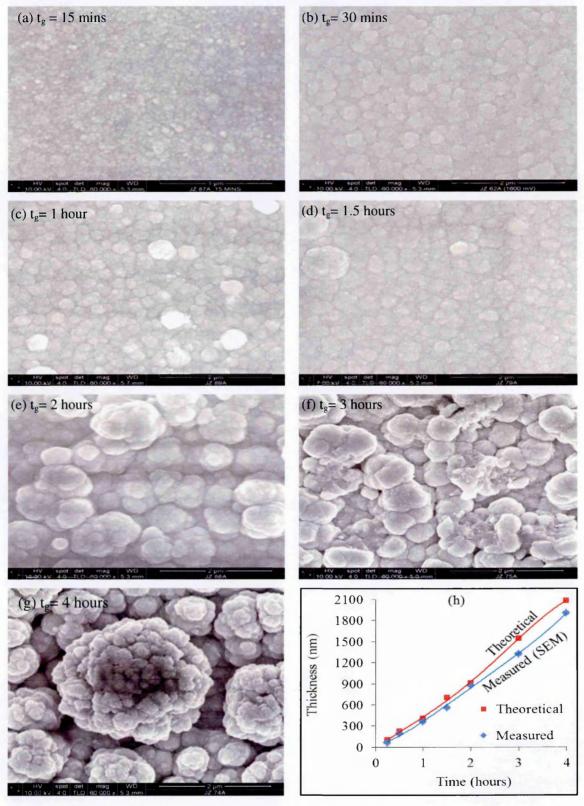

| 5.1 Introduction1265.2 Preparation of ZnTe electrolytic bath1275.3 Voltage optimisation and growth of ZnTe thin films1285.3.1 Cyclic voltammogram1285.3.2 Structural Analysis1305.3.2.1 X-ray diffraction studies1305.3.2.2 Raman spectroscopy1345.3.3 Optical absorption studies1355.3.4 Photoelectrochemical cell measurements1375.3.5 Morphological Analysis1385.3.5.1 Scanning electron microscopy138                                                                                            |

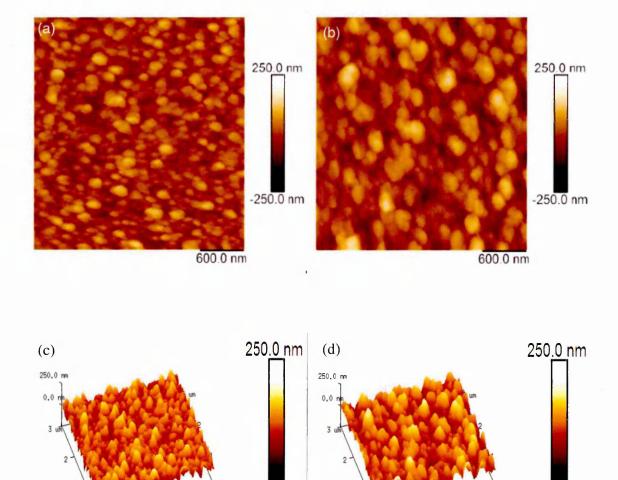

| 5.1 Introduction1265.2 Preparation of ZnTe electrolytic bath1275.3 Voltage optimisation and growth of ZnTe thin films1285.3.1 Cyclic voltammogram1285.3.2 Structural Analysis1305.3.2.1 X-ray diffraction studies1305.3.2.2 Raman spectroscopy1345.3.3 Optical absorption studies1355.3.4 Photoelectrochemical cell measurements1375.3.5 Morphological Analysis1385.3.5.1 Scanning electron microscopy1385.3.5.2 Atomic force microscopy139                                                          |

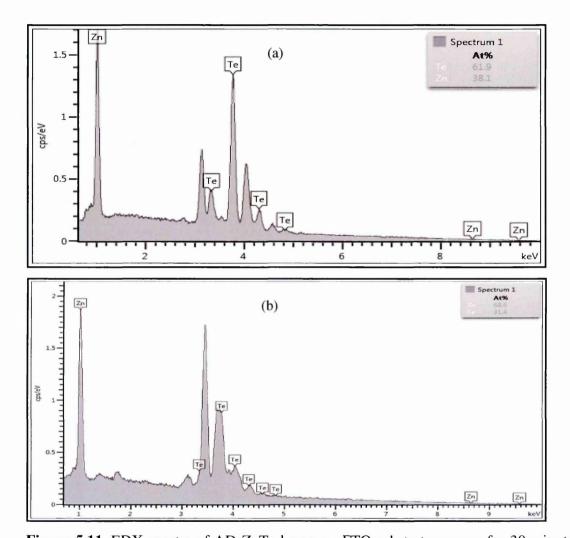

| 5.1 Introduction1265.2 Preparation of ZnTe electrolytic bath1275.3 Voltage optimisation and growth of ZnTe thin films1285.3.1 Cyclic voltammogram1285.3.2 Structural Analysis1305.3.2.1 X-ray diffraction studies1305.3.2.2 Raman spectroscopy1345.3.3 Optical absorption studies1355.3.4 Photoelectrochemical cell measurements1375.3.5 Morphological Analysis1385.3.5.1 Scanning electron microscopy1385.3.5.2 Atomic force microscopy1395.3.6 Compositional study of electroplated ZnTe layers140 |

|     | 5.4.1.2 Thickness effect on mobility and Fermi level position 144                                         |

|-----|-----------------------------------------------------------------------------------------------------------|

|     | 5.4.2 Effect of thickness on morphological properties of ZnTe layers . 146                                |

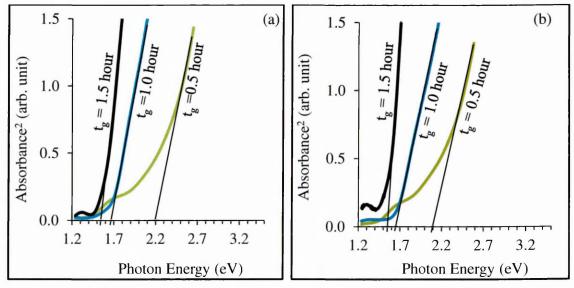

|     | 5.4.3 Effect of thickness on optical absorption                                                           |

|     | 5.5 Testing the electronic quality of ZnTe thin films                                                     |

|     | 5.5.1 DC conductivity measurements of ED-ZnTe layers                                                      |

|     | 5.5.2 Development of p-n homo-junction diodes from electroplated  ZnTe thin films                         |

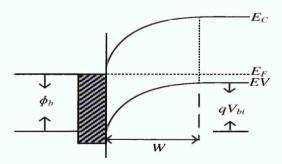

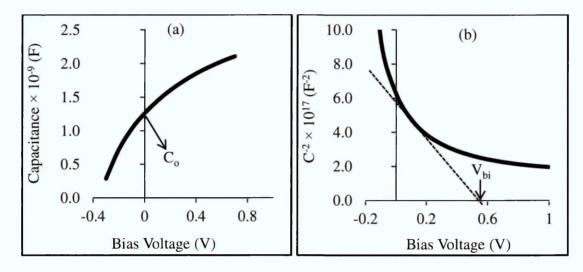

|     | 5.5.3 Capacitance-voltage measurements of p-n homo-junction diodes153                                     |

|     | 5.6 Summary                                                                                               |

|     | References                                                                                                |

| Cha | apter 6 - Growth and characterisation of CdS thin films158                                                |

|     | 6.1 Introduction                                                                                          |

|     | 6.2 Preparation of CdS electrolytic bath                                                                  |

|     | 6.3 Voltage optimisation and growth of CdS thin films                                                     |

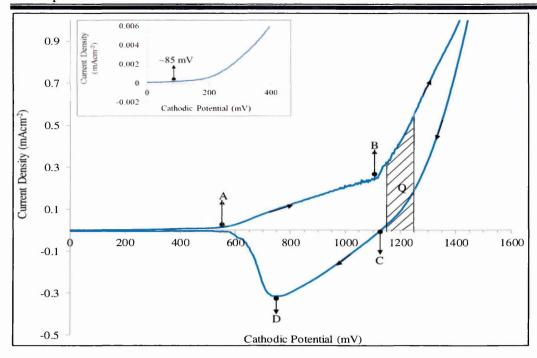

|     | 6.3.1 Cyclic voltammogram                                                                                 |

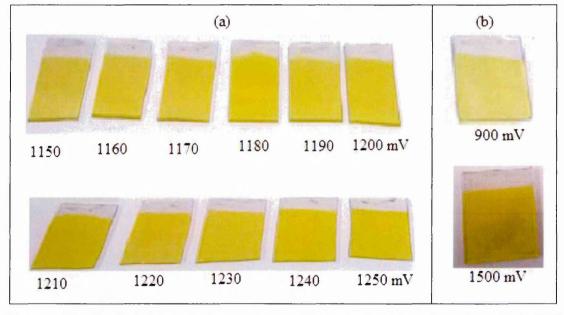

|     | 6.3.2 Visual appearance                                                                                   |

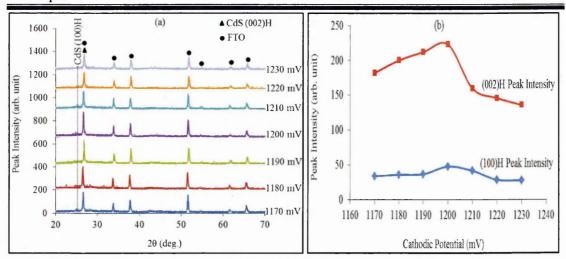

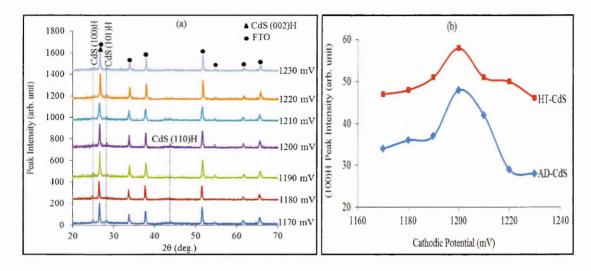

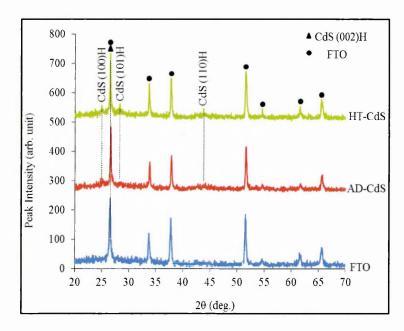

|     | 6.3.3 X-ray diffraction                                                                                   |

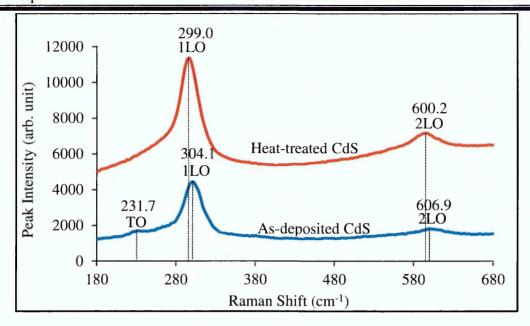

|     | 6.3.4 Raman spectroscopy measurements                                                                     |

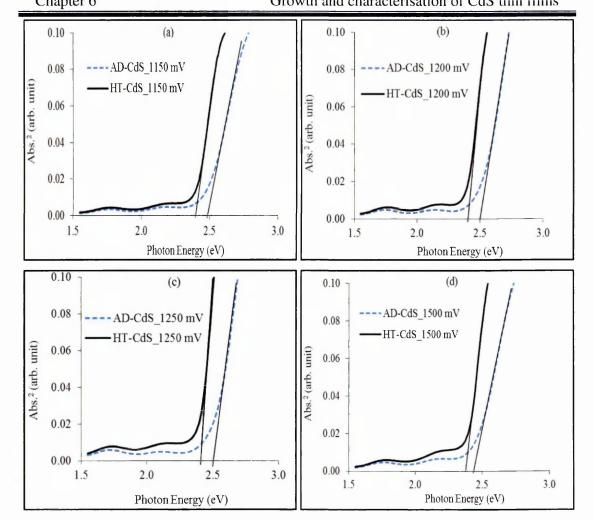

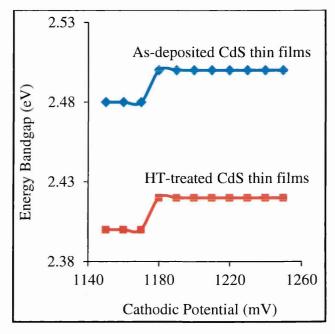

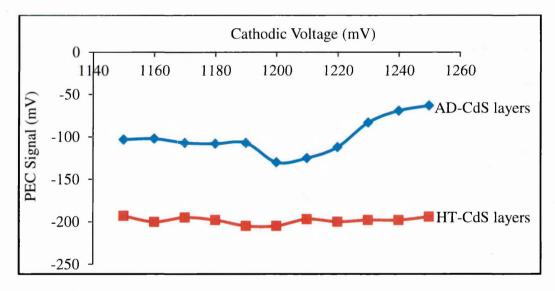

|     | 6.3.5 Optical absorption study                                                                            |

|     | 6.3.6 Photo-electrochemical (PEC) cell measurements study                                                 |

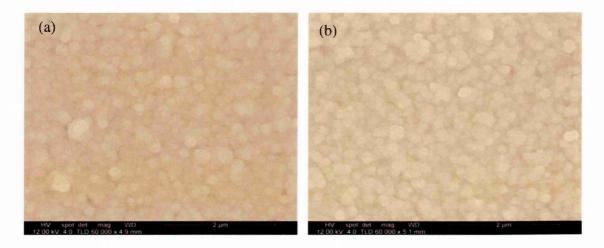

|     | 6.3.7 Morphological study                                                                                 |

|     | 6.4 Summary                                                                                               |

|     | References 173                                                                                            |

| Cha | pter 7 - Development of n-CdS/p-ZnTe heterostructures                                                     |

|     | 7.1 Introduction 177                                                                                      |

|     | 7.2 Characterisation of n-CdS/p-ZnTe hetero-structures                                                    |

|     | 7.2.1 Structural characterisation of n-CdS/p-ZnTe hetero-structure 178                                    |

|     | 7.2.2 Morphological characterisation of n-CdS/p-ZnTe hetero-structure180                                  |

|     | 7.2.3 Compositional characterisation of n-CdS/p-ZnTe hetero-structure180                                  |

|     | 7.3 Effects of CdCl <sub>2</sub> surface treatment on ZnTe mono-layers                                    |

|     | 7.3.1 Effect of CdCl <sub>2</sub> treatment on structural properties of p-ZnTe as hetero-partner to n-CdS |

|     | 7.3.2 Effect of CdCl <sub>2</sub> treatment on PEC cell measurements of p-ZnTe as hetero- partner to CdS  |

|      | 7.4 Application of n-CdS/p-ZnTe heterostructures                                                                                                                                                                                                                                                                                                                                                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 7.4.1 One-sided p-n junction diodes fabricated from n-CdS/p-ZnTe 186                                                                                                                                                                                                                                                                                                                                                                       |

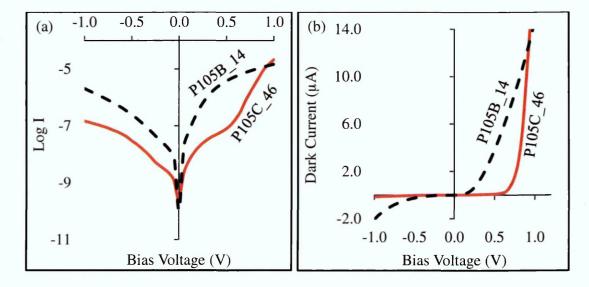

|      | 7.4.1.1 I-V characteristics of n-CdS/p-ZnTe hetero-junction diodes under dark condition                                                                                                                                                                                                                                                                                                                                                    |

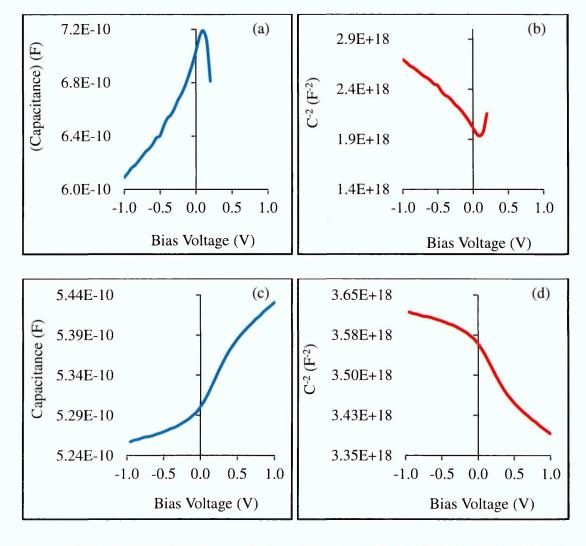

|      | 7.4.1.2 Discussion of results from C-V measurements for CdS thin films                                                                                                                                                                                                                                                                                                                                                                     |

|      | 7.4.1.3 Discussion of results from C-V Measurements for ZnTe thin films                                                                                                                                                                                                                                                                                                                                                                    |

|      | 7.4.1.4 Discussion of results from C-V measurements for CdS/ZnTe hetero-junction                                                                                                                                                                                                                                                                                                                                                           |

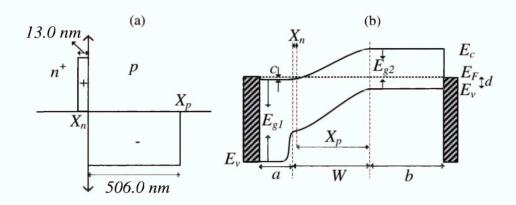

|      | 7.4.1.5 Proposed space charge density and energy band-diagram for CdS/ZnTe hetero-junction devices                                                                                                                                                                                                                                                                                                                                         |

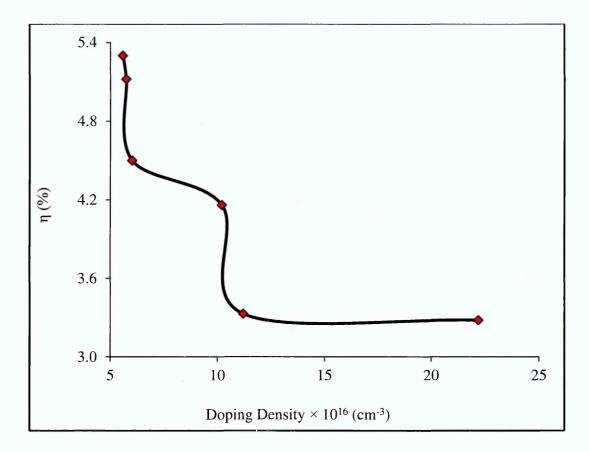

|      | 7.4.2 The n-CdS/p-ZnTe hetero-junction as a PV solar cell                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 7.4.2.1 Analysis of electronic parameters obtained from n-CdS/p-ZnTe device structures using I-V and C-V techniques 197                                                                                                                                                                                                                                                                                                                    |

|      | 7.4.2.2 C-V analysis of best cells selected from n-CdS/p-ZnTe device structures treated without and with CdCl <sub>2</sub> treatment202                                                                                                                                                                                                                                                                                                    |

|      | 7.5 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | References                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Chaj | Page 206 pter 8 - Electrodeposition and characterisation of CdTe thin films 209                                                                                                                                                                                                                                                                                                                                                            |

| Chaj |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Chaj | pter 8 - Electrodeposition and characterisation of CdTe thin films209                                                                                                                                                                                                                                                                                                                                                                      |

| Chaj | pter 8 - Electrodeposition and characterisation of CdTe thin films 209  8.1 Introduction                                                                                                                                                                                                                                                                                                                                                   |

| Chaj | 8.1 Introduction 209 8.2 Electrolyte preparation for CdTe thin films deposition 209                                                                                                                                                                                                                                                                                                                                                        |

| Chaj | 8.1 Introduction 209 8.2 Electrolyte preparation for CdTe thin films deposition 209 8.3 Voltage optimisation and growth of CdTe thin films 210                                                                                                                                                                                                                                                                                             |

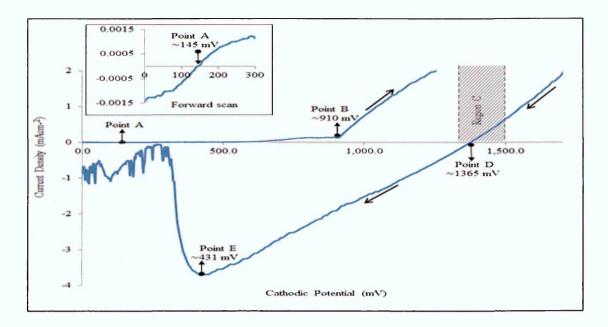

| Chaj | 8.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chaj | 8.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                           |

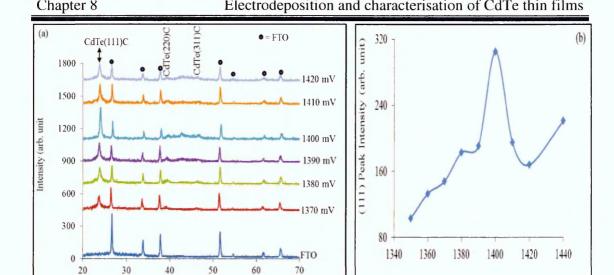

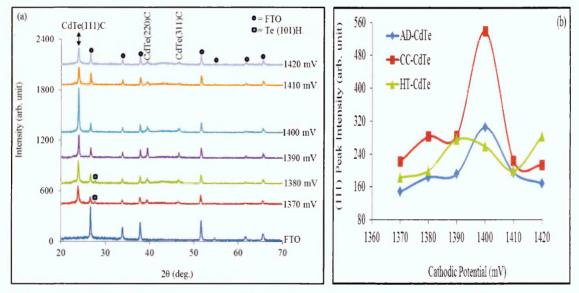

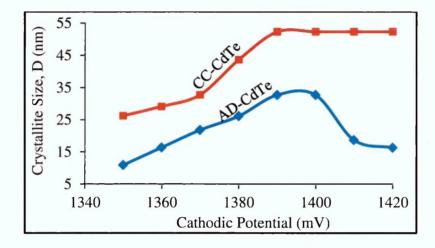

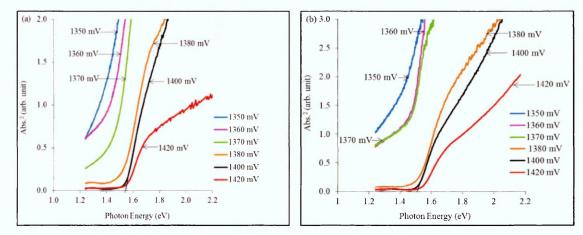

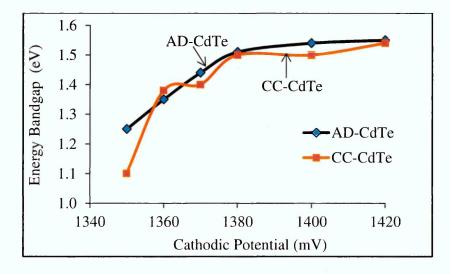

| Chaj | 8.1 Introduction 209 8.2 Electrolyte preparation for CdTe thin films deposition 209 8.3 Voltage optimisation and growth of CdTe thin films 210 8.3.1 Cyclic voltammetry 210 8.3.2 Structural analysis using XRD technique 212 8.3.3 Optical Absorption 215                                                                                                                                                                                 |

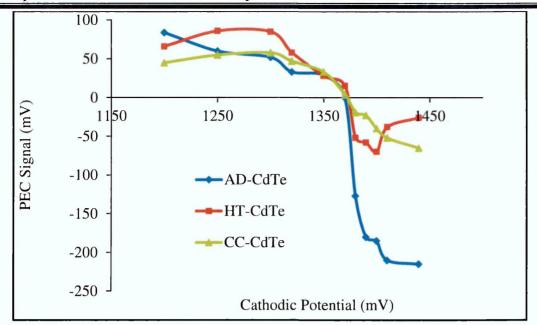

| Chaj | 8.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chaj | 8.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                           |

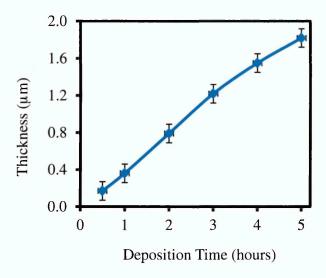

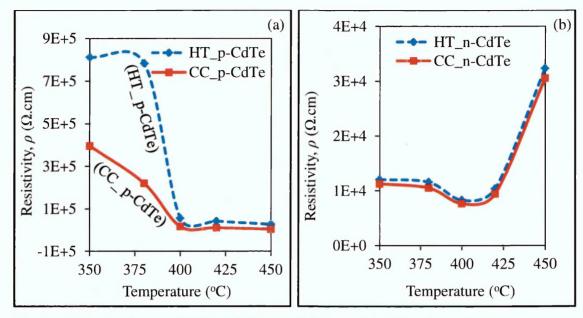

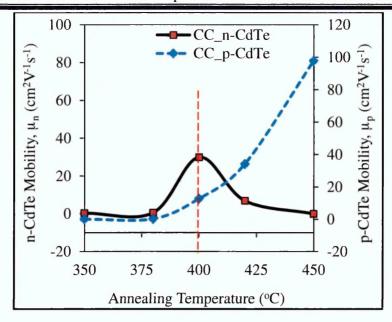

| Chaj | 8.1 Introduction 209 8.2 Electrolyte preparation for CdTe thin films deposition 209 8.3 Voltage optimisation and growth of CdTe thin films 210 8.3.1 Cyclic voltammetry 210 8.3.2 Structural analysis using XRD technique 212 8.3.3 Optical Absorption 215 8.3.4 Photoelectrochemical (PEC) cell measurement 217 8.3.5 Thickness Measurement 219 8.4 Effect of annealing temperatures on electronic properties of n- and p-CdTe layers 220 |

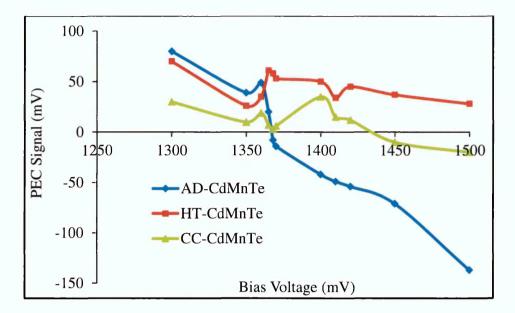

| Chaj | 8.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chaj | 8.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                           |

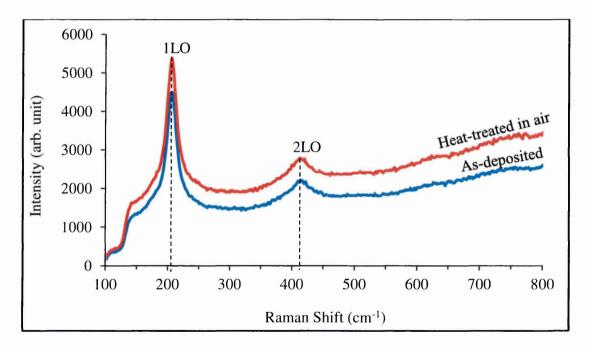

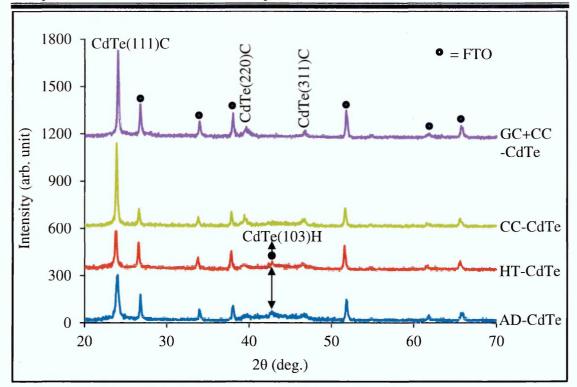

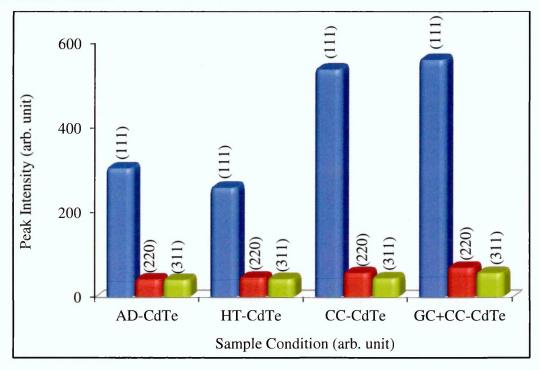

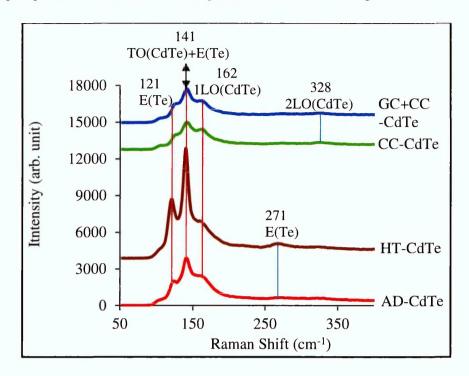

| 8.5.1.2 Raman spectroscopy study                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

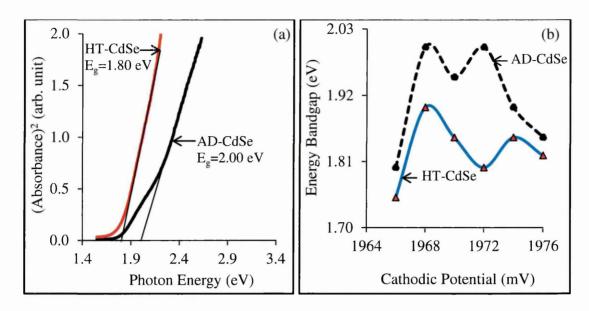

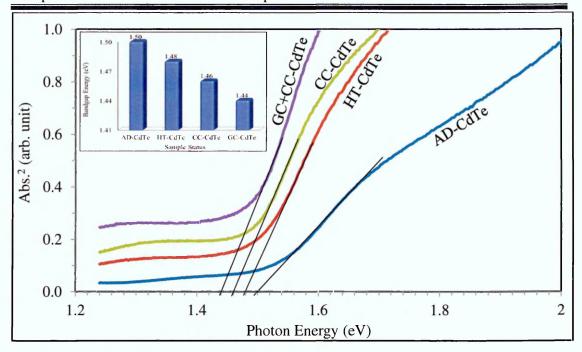

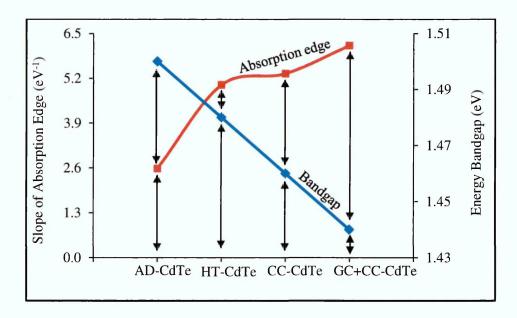

| 8.5.2 Effect of chemical treatments on CdTe optical properties 232                                                                                    |

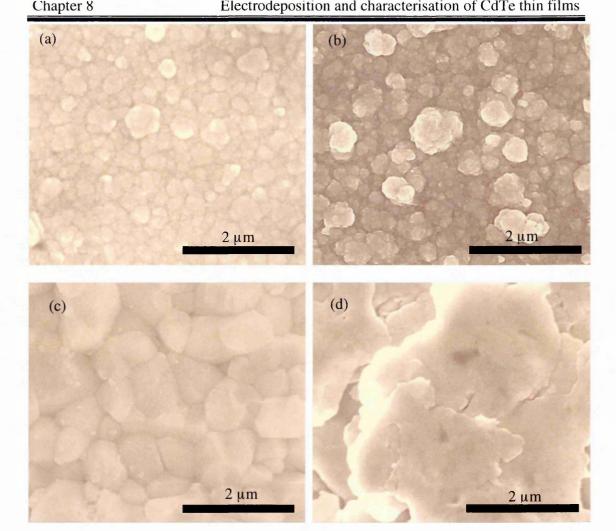

| 8.5.3 Effect on morphological properties                                                                                                              |

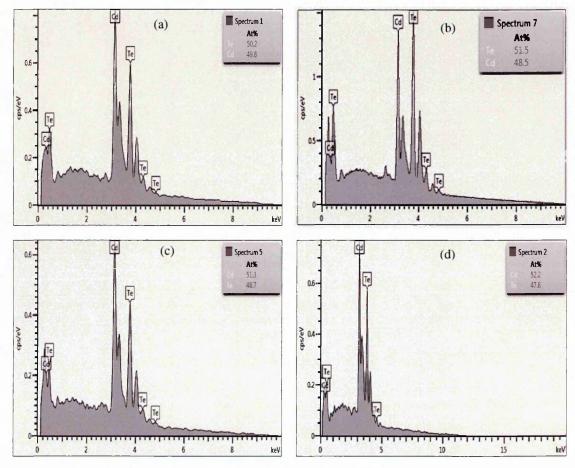

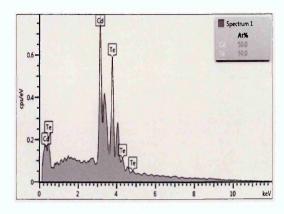

| 8.5.4 Effect on compositional properties                                                                                                              |

| 8.5.5 Effect on electrical properties                                                                                                                 |

| 8.6 Effect of pH variation of GaCl <sub>3</sub> +CdCl <sub>2</sub> solution for device application 242                                                |

| 8.6.1 Effect on PEC cell measurements                                                                                                                 |

| 8.6.2 Effect on morphological properties                                                                                                              |

| 8.7 Determination of Fermi level positions of electroplated AD- and CC-CdTe as observed from UPS measurement                                          |

| 8.8 Summary                                                                                                                                           |

| References                                                                                                                                            |

| Chapter 9 - Development of CdTe-based solar cells254                                                                                                  |

| 9.1 Introduction                                                                                                                                      |

| 9.2 Basic device processing steps                                                                                                                     |

| 9.3 Motivation behind GaCl <sub>3</sub> incorporation                                                                                                 |

| 9.4 Preparation of GaCl <sub>3</sub> and CdCl <sub>2</sub> solutions for surface treatment before annealing                                           |

| 9.5 What happens when the top surface of CdTe layers are treated with Ga 257                                                                          |

| 9.6 Fabrication of glass/FTO/n-CdS/n-CdTe/ device structures                                                                                          |

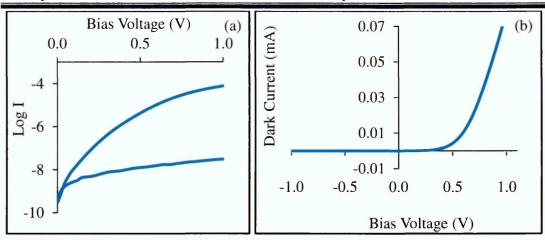

| 9.7 Assessment of glass/FTO/n-CdS/n-CdTe/Au solar cells                                                                                               |

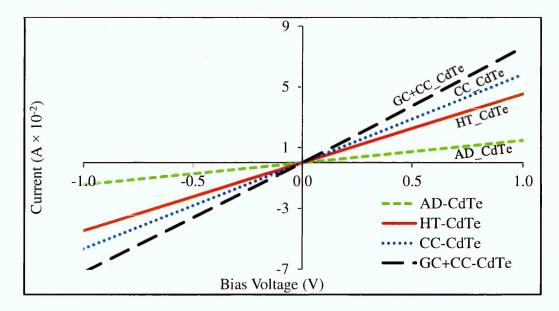

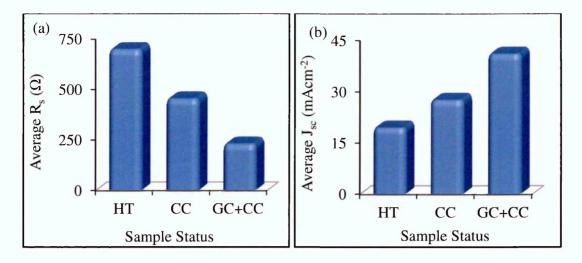

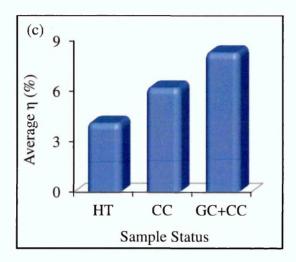

| 9.8 Investigating the effect of GaCl <sub>3</sub> inclusion into the usual CdCl <sub>2</sub> treatment on glass/FTO/n-CdS/n-CdTe/Au device structures |

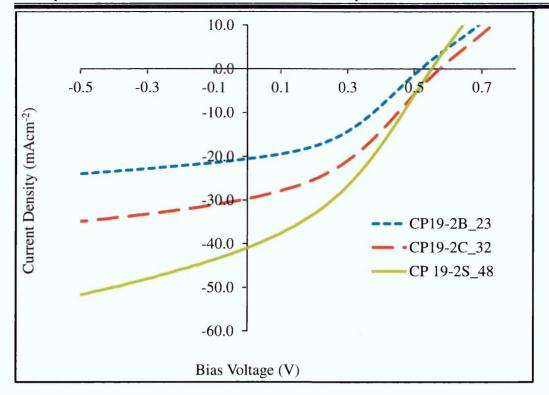

| 9.9 Effect of pH variation of GaCl <sub>3</sub> +CdCl <sub>2</sub> treatment solution on efficiency of glass/FTO/n-CdS/n-CdTe/Au solar cells          |

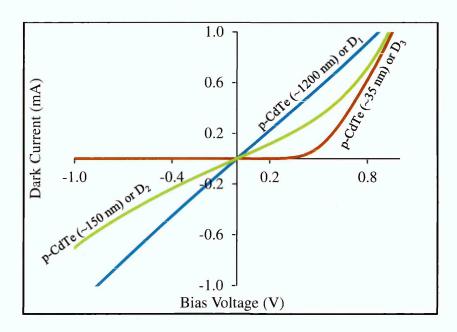

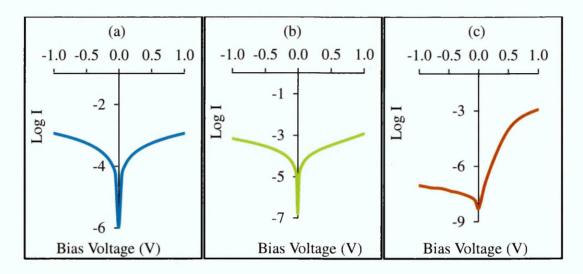

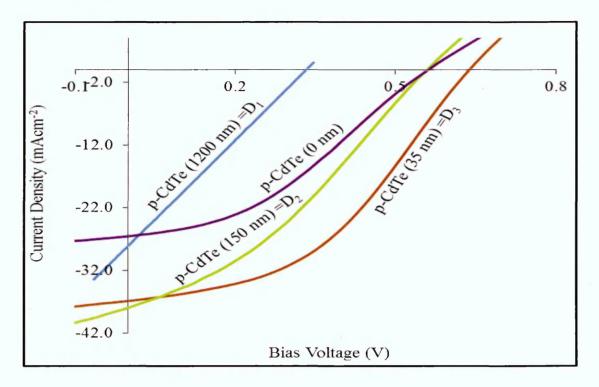

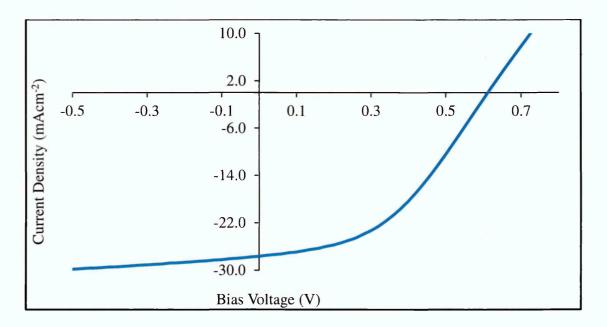

| 9.10 Characterisation of glass/FTO/n-CdS/n-CdTe/p-CdTe/Au solar cells 266                                                                             |

| 9.11 Comparative study of n-n and n-n-p device structures annealed at 450°C                                                                           |

| 9.12 Effect of variation in thickness of p-CdTe layer on glass/FTO/n-CdS/n-CdTe/p-CdTe/Au solar cells efficiency                                      |

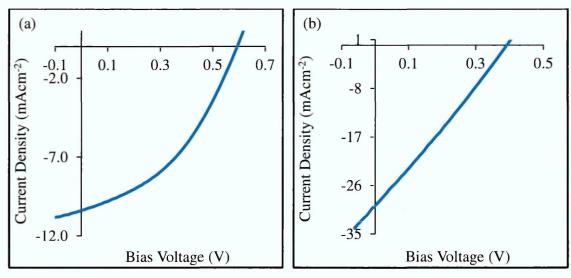

| 9.12.1 Current-voltage (I-V) measurement technique                                                                                                    |

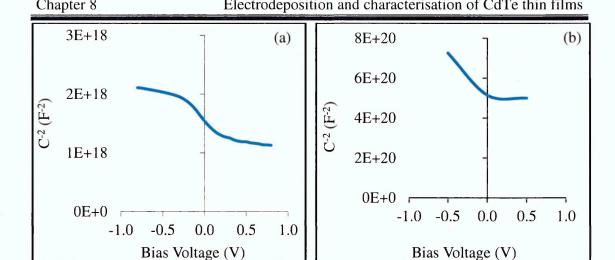

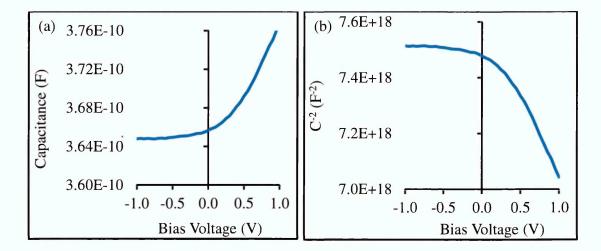

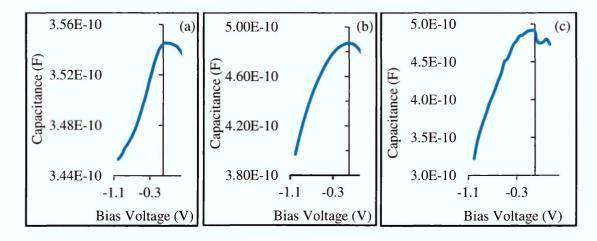

| 9.12.2 Capacitance-voltage (C-V) measurement technique                                                                                                |

| 9.13 Characterisation of n-n-p solar cell device structures with other p-type semiconductors                                                          |

| 9.14 Characterisation of n-n-n+Schottky barrier solar cell device structures 282                                                                      |

| 9.14.1 Characterisation of glass/FTO/n-ZnTe/n-CdS/n-CdTe/Au solar                                                     |                |

|-----------------------------------------------------------------------------------------------------------------------|----------------|

| cells                                                                                                                 | 34             |

| 9.14.2 Fabrication of glass/FTO/n-ZnS/n-CdS/n-CdTe/Au solar cells. 28                                                 | 36             |

| 9.14.2.1 Characterisation of glass/FTO/n-ZnS/n-CdS/n-CdTe/Au solar cells using current-voltage (I-V) technique 28     | 88             |

| 9.14.2.2 Discussion/reasons for observed high J <sub>sc</sub>                                                         | 91             |

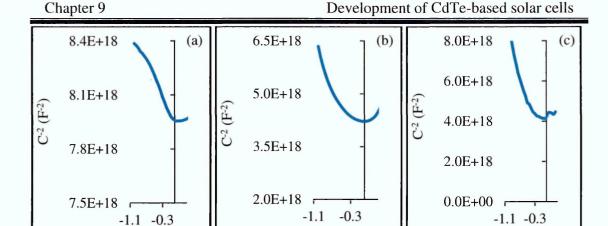

| 9.14.2.3 Characterisation of glass/FTO/n-ZnS/n-CdS/n-CdTe/Au solar cells using capacitance-voltage (C-V) technique 29 | 92             |

| 9.15 Summary                                                                                                          | 95             |

| References                                                                                                            | <del>)</del> 7 |

| Chapter 10 - Conclusions, challenges and suggestions for future work 30                                               | )1             |

| 10.1 Conclusions                                                                                                      | )1             |

| 10.2 Challenges encountered during the current investigations and proposed solution                                   | )2             |

| 10.3 Suggestions for future work                                                                                      | )4             |

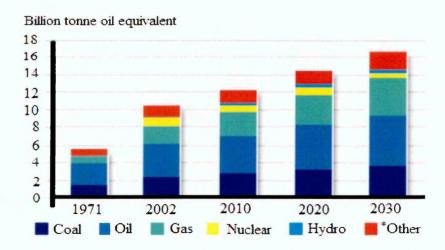

| Figure 1.1. Projected future demand for different energy sources. Note that                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

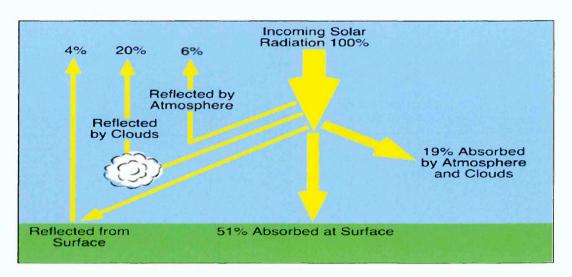

| Figure 1.2. Reflected and absorbed solar radiation [11]                                                                                                                                                                                                       |

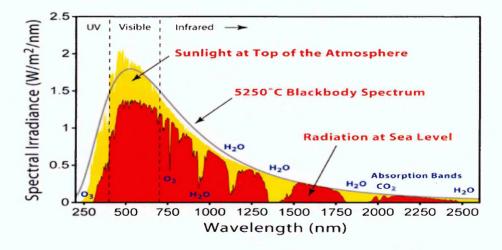

| Figure 1.3. The energy spread in the solar spectrum [12,13]4                                                                                                                                                                                                  |

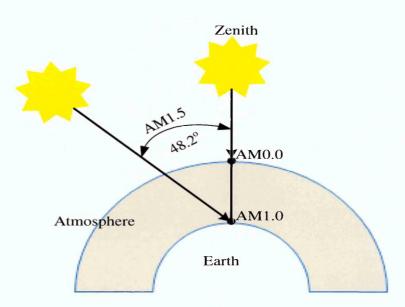

| Figure 1.4. Path lengths taken by the solar spectrum through the atmosphere5                                                                                                                                                                                  |

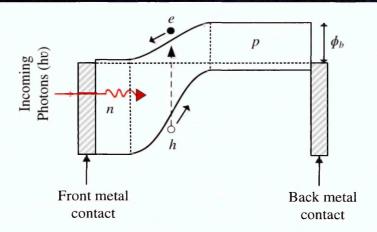

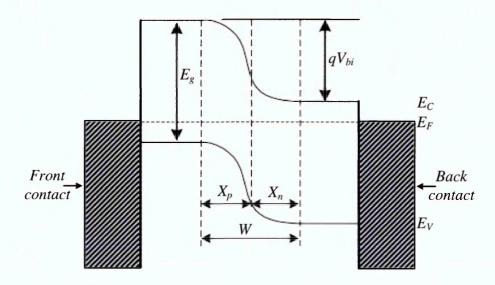

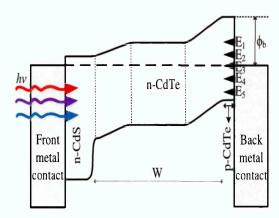

| Figure 1.5. Energy band diagram of a typical p-n junction solar cell based on n-CdS and p-CdTe                                                                                                                                                                |

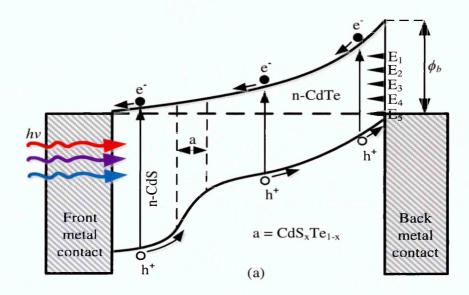

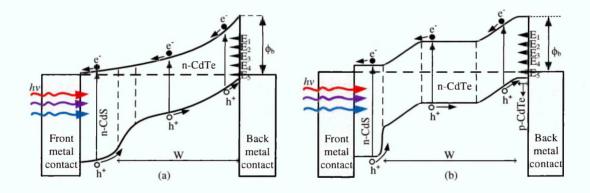

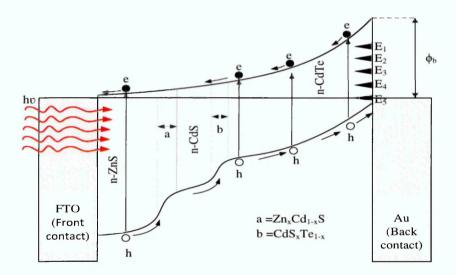

| Figure 1.6. Energy band diagram of the proposed n-CdS/n-CdTe $(n-n)$ heterojunction device structure with a large Schottky barrier at the metal back contact. Note that the defect levels responsible for Fermi-level pinning are shown as $E_1$ to $E_5$ .   |

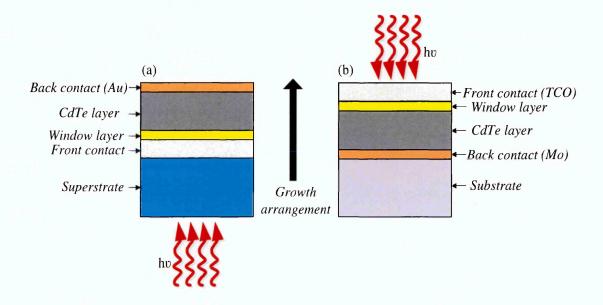

| Figure 1.7. Solar cell configurations used for CdTe thin film solar cells, (a) superstrate and (b) substrate configurations                                                                                                                                   |

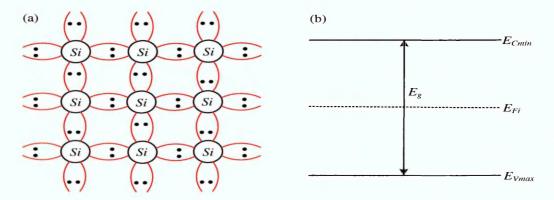

| Figure 2.1.Typical diagrams illustrating (a) covalent bond formation in intrinsic silicon crystal lattice and (b) energy band diagram of an intrinsic semiconductor material with emphasis on Fermi level position                                            |

| Figure 2.2. Typical energy band diagrams of an intrinsic semiconductor material illustrating the excitation of (a) one electron and (b) all electrons from valence band to conduction band after bombardment of the atoms with light 26                       |

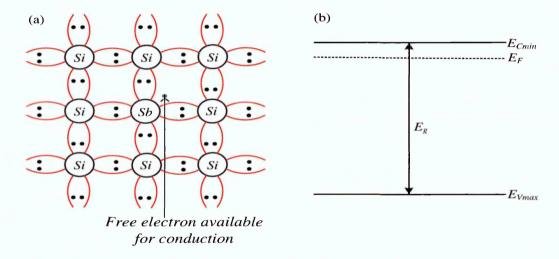

| Figure 2.3. Typical diagrams illustrating (a) covalent bond formation between silicon (Si) and antimony (Sb) atoms, and (b) energy band diagram of n-type semiconductor material with emphasis on Fermi level position                                        |

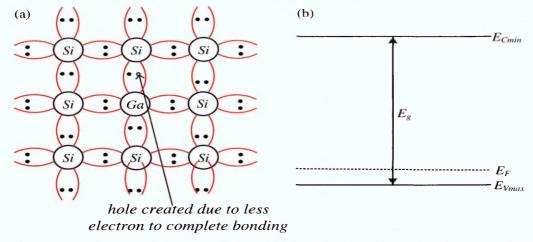

| Figure 2.4. Typical diagrams illustrating (a) covalent bond formation between silicon (Si) and gallium (Ga) atoms, and (b) energy band diagram of p-type semiconductor material with emphasis on Fermi level position                                         |

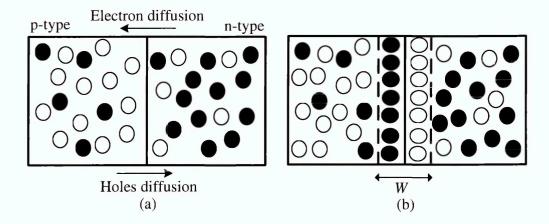

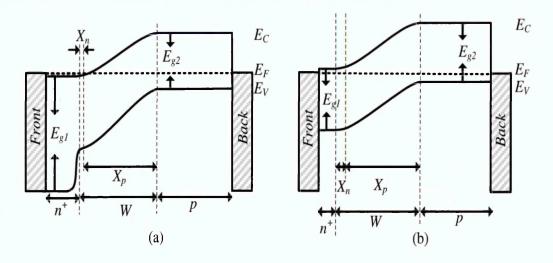

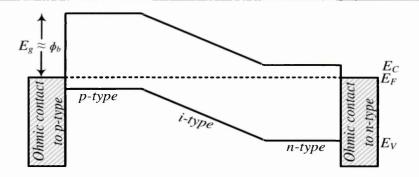

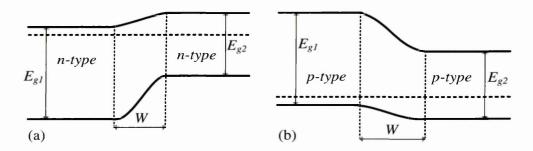

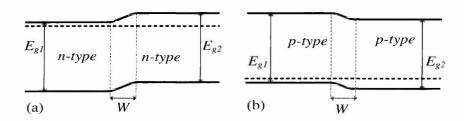

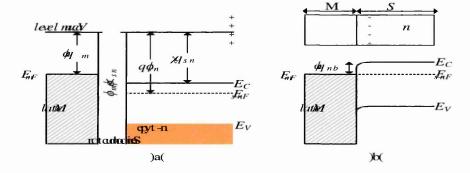

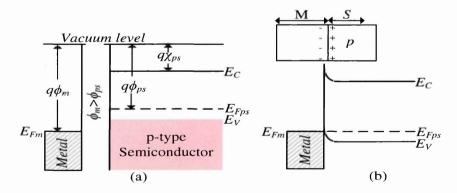

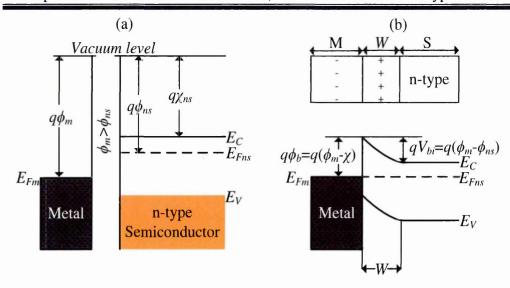

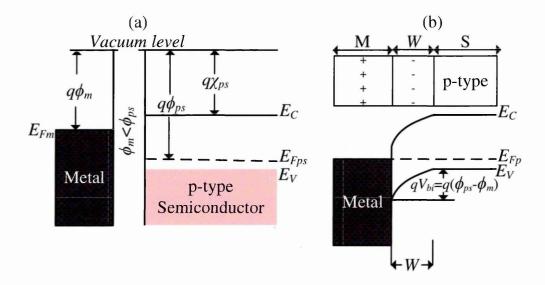

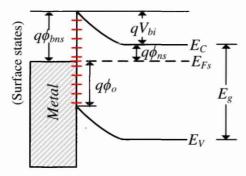

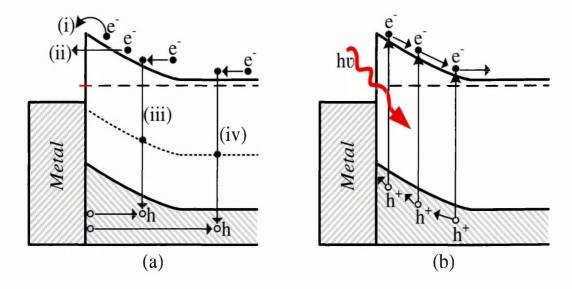

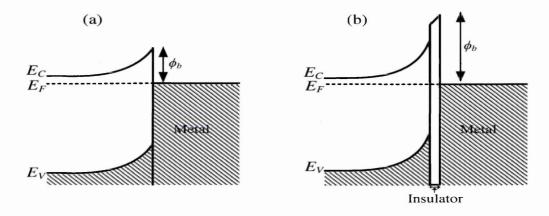

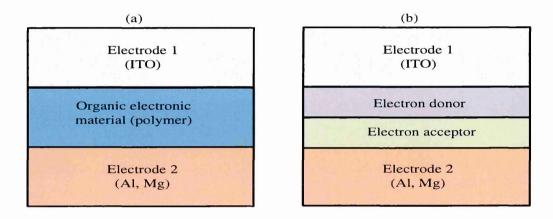

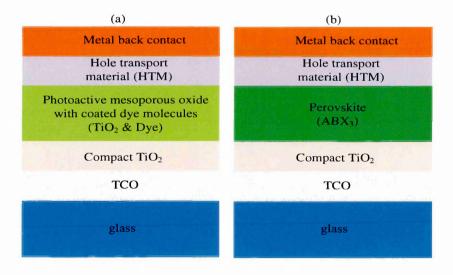

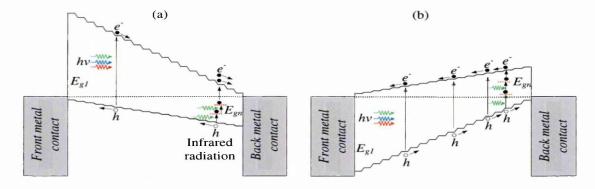

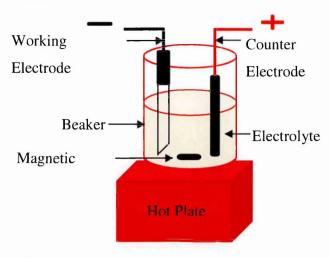

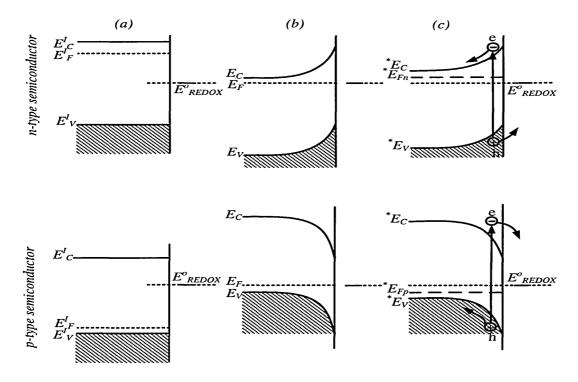

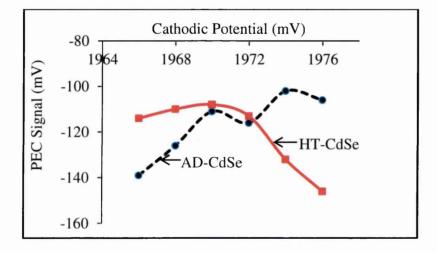

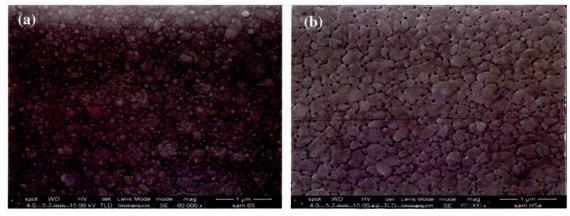

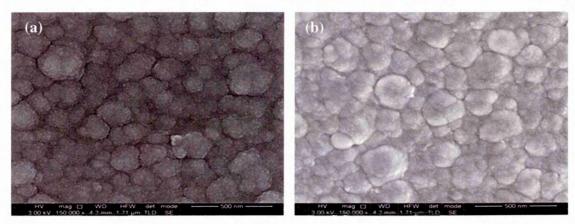

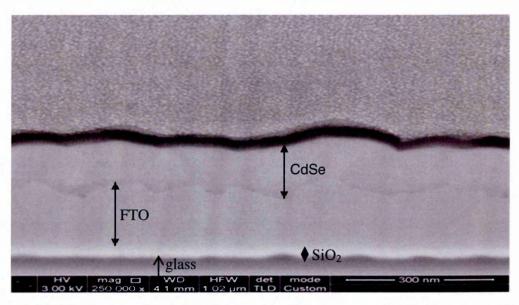

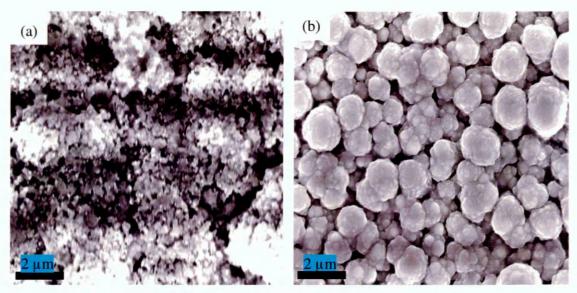

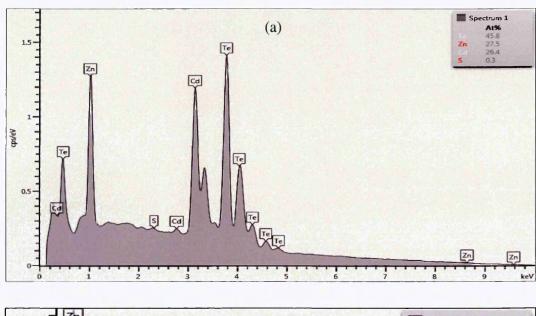

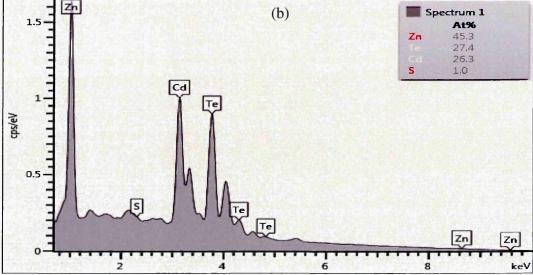

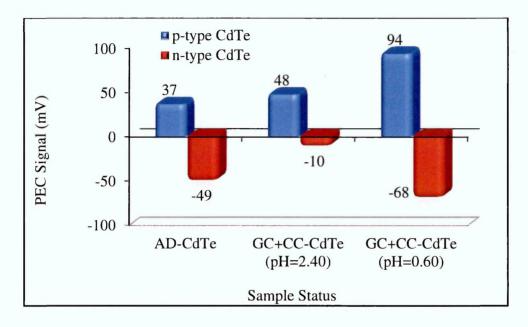

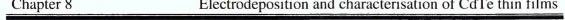

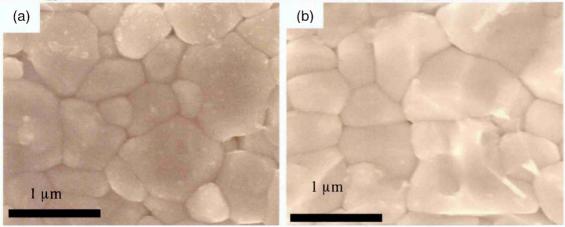

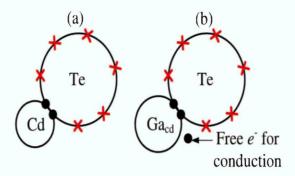

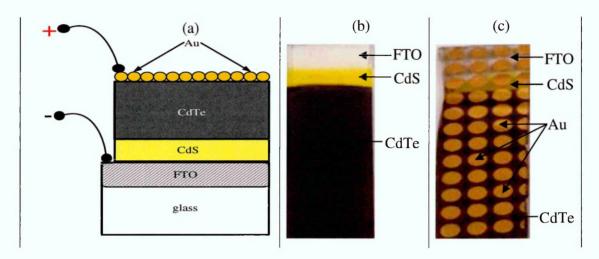

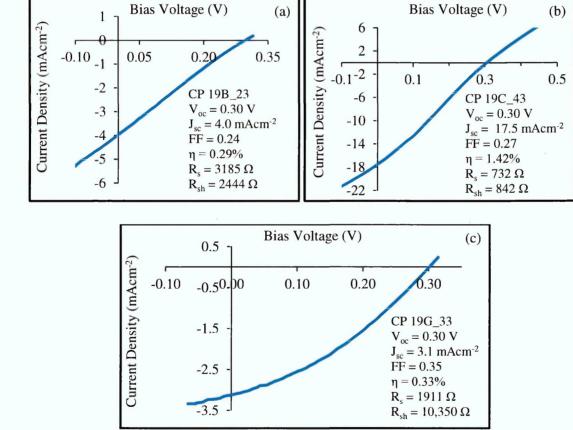

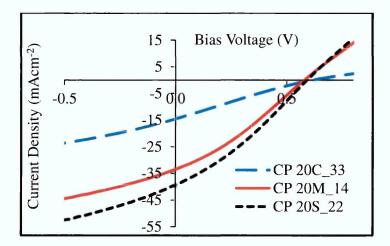

| Figure 2.5. Typical schematic diagrams illustrating (a) electrons and holes diffusion and (b) the formation of barrier which prevents further diffusion of holes and electrons. The region between the created barriers is the depletion region with width, W |