# Sheffield Hallam University

Electronic properties of defects in silicon and related materials.

MITROMARA, Niki.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/20068/

## A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/20068/ and <u>http://shura.shu.ac.uk/information.html</u> for further details about copyright and re-use permissions.

| Sheffield Halla | m University |

|-----------------|--------------|

| Learning area   | T Services   |

| Adsetts Centre  | City Campus  |

| Sheifield       | S1 1WB       |

ProQuest Number: 10697375

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10697375

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

# ELECTRONIC PROPERTIES OF DEFECTS IN SILICON AND RELATED MATERIALS

## NIKI MITROMARA

A thesis submitted in partial fulfilment of the requirements of Sheffield Hallam University for the degree of Doctor of Philosophy

October 2008

## **Declaration**

The work described in this thesis was carried out by the author in the Materials and Engineering Research Institute, Sheffield Hallam University. The author declares that this work has not been submitted for any other degree. The work is original except where acknowledged by reference.

The Author

#### Niki Mitromara

## **Acknowledgements**

I would like to express my sincere gratitude to my supervisor Professor Jan Evans-Freeman, for her constant help and guidance, her support throughout my PhD and for her understanding on my problems during writing up. Working with her was very instructive as well as a pleasant experience. I would also like to thank my second supervisor Dr. Karen Vernon-Parry for helpful discussions and assistance with experimental equipment. In addition, I am thankful to Dr. Mahmoud Gad for helping me understand the equipment and teaching me the software through the initial stages of my PhD. I would like to acknowledge the assistance of Mr. Mal McGowan at the University of Manchester, for helping with the fabrication of my devices and fruitful discussions. I would also like to thank the administration staff of the Materials and Engineering Research Institute at Sheffield Hallam University for their friendliness and support especially throughout the PhD. Finally I would like to thank my family for their constant love, support and encouragement throughout the duration of my studies. Without their support completion of this work would not have been possible. To the four people I consider family. Your presence in my life is a blessing.

### **Abstract**

Efforts in the current semiconductor industry are focused on the production of smaller, more efficient and inexpensive devices of higher packing density. As silicon is the dominant semiconductor implemented for the fabrication of the majority of semiconductor devices, perpetual research has focused on the improvement of its properties and the realisation of the most efficient structures. This thesis presents the electrical characterisation of two different diode structures that are important for the present and future generations of electronic devices.

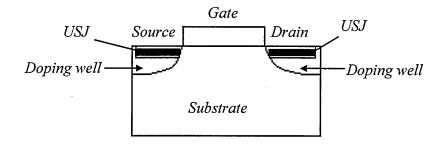

The first part of the thesis is focused on the electrical characterisation of Ultra-Shallow Junction (*USJs*) Si diodes. Both  $p^+n$  and  $n^+p$  USJ structures that contained different implants were examined. These were very highly doped and intended to simulate the situation where a doping well is formed after heavy doping in Si for the fabrication of transistors currently used in Complementary-Metal-Oxide-Semiconductor (*CMOS*) technology. The implanted USJ diodes were provided by NXP, Belgium and contact deposition was performed before their electrical characterisation as part of this project. Subsequently the  $p^+n$  and  $n^+p$  USJ diodes were characterised by the use of Capacitance-Voltage (CV), Current-Voltage (IV), Deep Level Transient Spectroscopy (DLTS) and high resolution Laplace DLTS (LDLTS). DLTS and LDLTS are very powerful spectroscopic techniques for the profiling of defects in the bandgap of a semiconductor as well as for the identification of the electrical signatures of these defects. Transient-Enhanced Diffusion (TED) related defects were detected in these diodes as the presence of mainly carbon-related interstitial complexes was observed. In addition, certain vacancy or vacancy-dopant related levels were also discerned.

The second part of this thesis presents the electrical characterisation from Schottky pdiamond/p-Si and p-diamond/n-Si p-n diodes. These diodes were readily provided, grown by the Chemical Vapour Deposition (CVD) technique, for the electrical characterisation that was performed as part of this project. The purpose of characterising both Schottky and p-n diamond on Si diodes was to detect defects near the surface of the films and near the interface with Si and hence provide a comparison between defects present at the beginning and end of growth. More defects were found near the interface with Si and the majority of observed defects were related to extended defects while the presence of grain boundaries in polycrystalline diamond was discussed.

v

## **Contents**

| Chapter    | 1: Introduction       | 1 |

|------------|-----------------------|---|

| 1.1        | Overview              | 1 |

| 1.2        | Aims of the project   | 3 |

| 1.3        | Outline of the thesis | 3 |

| References |                       | 5 |

| Chapter   | 2: Defects in Silicon             | 6  |

|-----------|-----------------------------------|----|

| 2.1       | Introduction                      | 6  |

| 2.2       | Energy levels                     | 7  |

| 2.3       | Crystal Defects                   | 9  |

| 2.4       | Irradiation-related defects in Si | 14 |

| 2.4.1     | Defects in p-type irradiated Si   | 14 |

| 2.4.2     | Defects in n-type irradiated Si   | 16 |

| 2.5       | Ion-implantation defects          | 18 |

| 2.6       | Transient Enhanced Diffusion      | 21 |

| 2.7       | Ultra-Shallow Junctions           | 23 |

| 2.8       | Conclusion                        | 25 |

| Reference | es                                | 26 |

| Chapter | 3: Diamond properties and defects | 31 |

|---------|-----------------------------------|----|

| 3.1     | Introduction                      | 31 |

| 3.2     | Need for wide bandgap materials   | 32 |

| 3.2.1   | High temperature operation        | 33 |

| 3.2.2   | High electric breakdown field     | 36 |

| 3.2.3   | High saturation drift velocity    | 37 |

| 3.2.4   | High thermal conductivity         | 38 |

| 3.3     | Wide bandgap semiconductors       | 38 |

| 3.3.1   | Silicon carbide                   | 39 |

| 3.3.2   | Gallium Nitride                   | 42 |

| 3.4     | Diamond                           | 43 |

| 3.4.1   | Diamond origin and structure      | 44 |

| 3.4.2   | Natural diamond classification    | 44 |

| 3.4.3   | Synthetic diamond growth          | 45 |

| 3.4.4    | Diamond properties | 47 |

|----------|--------------------|----|

| 3.4.5    | Defects in diamond | 57 |

| 3.4.5.1  | Grain Boundaries   | 57 |

| 3.4.5.1  | Other defects      | 58 |

| 3.5      | Conclusion         | 59 |

| Referenc | References         |    |

|          |                    |    |

| Chapter    | r 4: Experimental techniques              | 64 |

|------------|-------------------------------------------|----|

| 4.1        | Introduction                              | 64 |

| 4.2        | The p-n diode                             | 64 |

| 4.3        | Schottky barrier diode                    | 70 |

| 4.4        | Tunnelling in diodes                      | 76 |

| 4.5        | Deep Level Transient Spectroscopy         | 76 |

| 4.5.1      | DLTS description and setup                | 77 |

| 4.5.2      | Trap parameters                           | 82 |

| 4.6        | Laplace Deep Level Transient Spectroscopy | 85 |

| 4.7        | Conclusion                                | 86 |

| References |                                           | 87 |

##

| 5.1        | Introduction                           | 89 |

|------------|----------------------------------------|----|

| 5.2        | Specifications of USJ diodes           | 89 |

| 5.3        | Ohmic contacts to the USJ diodes       | 93 |

| 5.4        | Specifications of diamond diodes on Si | 95 |

| 5.5        | Fabrication of diamond-silicon diodes  | 96 |

| 5.6        | Experimental set-up                    | 97 |

| 5.7        | Conclusion                             | 98 |

| References |                                        | 99 |

| Introduction     | 100                                      |

|------------------|------------------------------------------|

| Control diode S2 | 101                                      |

| Diode S3         | 104                                      |

| Diode S4         | 121                                      |

| Diode S5         | 136                                      |

|                  | Control diode S2<br>Diode S3<br>Diode S4 |

| 6.6        | Diode S6   | 144 |

|------------|------------|-----|

| 6.7        | Conclusion | 154 |

| References |            | 155 |

# Chapter 7: Experimental results from n<sup>+</sup>p Ultra-shallow junctions1567.1Introduction156

| 7.2        | Control diode S9 | 156 |

|------------|------------------|-----|

| 7.3        | Diode S8         | 162 |

| 7.4        | Diode S7         | 172 |

| 7.5        | Conclusion       | 186 |

| References |                  | 188 |

| Chapter    | 8: Deep Level Transient Spectroscopy of p-type diamond on silicon | 189 |

|------------|-------------------------------------------------------------------|-----|

| 8.1        | Introduction                                                      | 189 |

| 8.2        | Diamond on p-type silicon                                         | 190 |

| 8.3        | Diamond on n-type silicon                                         | 212 |

| 8.4        | Discussion and comparison                                         | 236 |

| 8.5        | Conclusion                                                        | 237 |

| References |                                                                   | 238 |

| Chapter | 9: Conclusions and future work                 | 239 |

|---------|------------------------------------------------|-----|

| 9.1     | Conclusions from Ultra-shallow junction diodes | 239 |

| 9.2     | Conclusions from diamond on Si diodes          | 240 |

| 9.3     | Future Work                                    | 241 |

.

•

## List of publications

#### Journal publications – accepted for publication

- N. Mitromara, J.H. Evans-Freeman and R. Duffy, "Laplace Deep Level Transient Spectroscopy of ultra shallow implanted junctions in Si", accepted for publication in IEEE Xplore after presentation at the IUMRS-ICEM 2008 International Conference on Electronic Materials, Sydney, Australia.

- 2) Karen D. Vernon-Parry, Jan H. Evans-Freeman, Niki Mitromara, and Paul W. May, "High Resolution Deep Level Transient Spectroscopy of p-n diodes formed from p-type polycrystalline diamond on n-type silicon", accepted for publication in IEEE Xplore after presentation at the IUMRS-ICEM 2008 International Conference on Electronic Materials, Sydney, Australia.

#### Journal Publications – Published

- N. Mitromara, J.H. Evans-Freeman, C. Gädtke, P.W. May, "High resolution Laplace deep level transient spectroscopy of p-type polycrystalline diamond", phys. stat. sol. (a) 205 (2008) 2184-9.

- N. Mitromara, J.H. Evans-Freeman, and R. Duffy, "Deep Level Transient Spectroscopy of ultra shallow junctions in Si formed by implantation", Solid state phenomena, 131-33, (2008) 497-502.

- J.H. Evans-Freeman, D. Emiroglu, M.A. Gad, N. Mitromara and K.D. Vernon-Parry, "Deep electronic states in ion-implanted Si", Journal of materials science, 41, 3, (2006) 1007-1012

## **Chapter 1: Introduction**

#### **1.1 Overview**

Semiconductors are the main driving force behind the rapid and well established success of the electronics industry. Modern electronic devices are the outcome of continuous innovation and research and constitute one of the most profitable markets presently. The properties of many semiconductors have been explored since the beginning of the last century, such as germanium (*Ge*) which however was found to have leakage and heating problems. Since the establishment of silicon (*Si*) in the 1930s as the material with the most favourable properties, the semiconductor industry advanced with incredibly fast rates, only to be further increased by the introduction of the Metal-Oxide-Semiconductor-Field-Effect-Transistor (*MOSFET*) in 1960 [1]. Continuous increase in integration density driven by Moore's Law, entails perpetual efforts towards reduction in semiconductor device dimensions and provides great challenges. These lie in the increase of the performance and capabilities of the devices, while significantly decreasing their cost and energy consumption.

Almost fifty years later, Si is still the dominant semiconductor material used in electronic devices. It is however widely understood that its physical limits in the increasingly sophisticated Integrated Circuits (*ICs*) are soon to be reached. The evergrowing requirement for downscaling of device dimensions gives rise to complicated physical phenomena. The behaviour of electrons deviates from the classical particle form when only a few atomic layers of the semiconductor are necessary for the fabrication of ultra-thin structures and quantum analysis is then required to control the operation of the device. More importantly, increased gate leakage current, dopant diffusion and carrier and lifetime degradation are increasingly significant obstacles in the functionality of MOSFETs.

As scaling increases, the presence of defects in the semiconductor can be detrimental to the device performance and a vast amount of research has been performed to characterise, identify, and eliminate them or successfully control their behaviour. Moreover, a wide range of experimental techniques have been developed to ensure

adequate information of the properties of these defects can be obtained and is subsequently used in order to produce beneficial device characteristics. In addition to the study of defects, investigation of novel semiconducting materials has increased during the last few decades in order to provide an alternative to the problems the Si semiconductor industry is facing. These materials have to either have sufficiently good properties to replace Si or must be compatible with the modern Complementary-Metal-Oxide-Semiconductor (*CMOS*) technology which is based on Si. Such research has recently focused on wide bandgap semiconductors as they possess exceptional physical and electrical properties for either light emission or power devices. High carrier mobility, high power capability and operation under harsh environments, such as high temperature, make these materials very promising candidates for future generations of electronics. The implementation of these materials alone, is however impeded by the years of experience against the well characterised properties of Si. In addition the inability at present, to produce very high quality or large area of single crystals of most these semiconductors, suggests that more research is required.

In view of achieving reduced-size microelectronic devices, investigation of ultrashallow Si structures and thin film diamond based devices have been examined in this project. In order to achieve smaller devices, very highly doped Si has been provided by NXP in Belgium, resulting in Ultra-Shallow Junctions (*USJs*). The use of such structures is imposed by the requirements of present and future generation of semiconducting devices though many challenges lie in the complicated nature of such materials. Successful characterisation of the defects and handling of the properties of USJs may lead to the improvement of these structures which are already being used by the current Si CMOS technology. Defect characterisation was performed using one of the most suitable techniques for this purpose, namely Deep Level Transient Spectroscopy (*DLTS*).

The same capacitance transient based technique, developed in 1974 [2], was also implemented for the profiling of the thin diamond films. The latter were synthesized by Chemical Vapour Deposition (CVD), a method which has been studied for a few decades but has only produced fruitful results in diamond recently [3, 4]. The challenges involved with the characterisation of devices based on diamond emanate

from the polycrystalline nature of most of these films and the large bandgap which requires high temperature for the investigation of possible defects.

#### 1.2 Aims of the project

This project is based on Si ultra-shallow junction diodes and synthetic thin diamond films grown on Si substrates. Therefore two different semiconductor technologies had to be investigated. The main aims of the project include:

- 1. Studying the nature and properties of defects in Si.

- 2. Studying the properties of wide bandgap semiconductors and in particular diamond for the fabrication of diamond diodes on Si substrates.

- 3. Electrical characterisation of p<sup>+</sup>n and n<sup>+</sup>p ultra-shallow junctions using DLTS and high-resolution Laplace DLTS (*LDLTS*).

- 4. Electrical characterisation of p-type diamond on p-type Si Schottky diodes using DLTS and LDLTS.

- 5. Electrical characterisation of p-type diamond on n-type Si p-n diodes by the same techniques in order to provide and in-depth analysis of the CVD grown diamond film.

- 6. Drawing conclusions about USJs and diamond diodes that will enhance scientific knowledge and assist in the future study and implementation of such structures.

### **1.3 Outline of the thesis**

Chapter 2 provides an overview of defects present in Si. The role of impurities and defects such as point defects, extended defects and dislocations is examined and the effect they produce on Si crystals and Si devices. Finally current technological problems such as Transient Enhanced Diffusion of Boron are addressed and a literature research of ultra-shallow junctions is provided.

Chapter 3 is an introduction to wide bandgap materials. Their properties, originating from the large bandgap, are described as well as the reasons for their possible ability to replace Si in devices. Furthermore, research is focused on diamond as the material of choice in this project, its origin and growth techniques and the properties of defects commonly found.

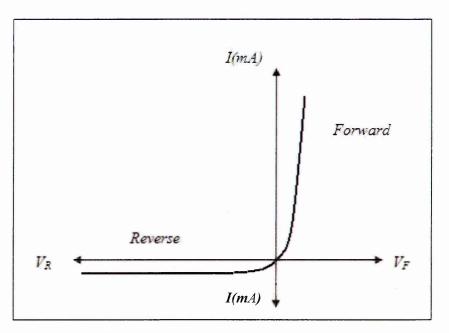

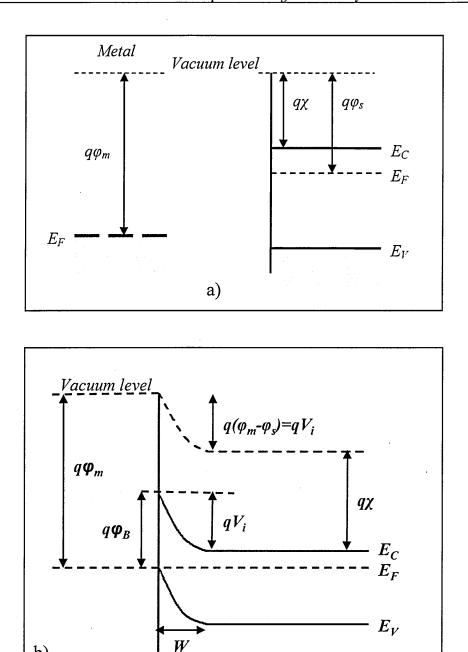

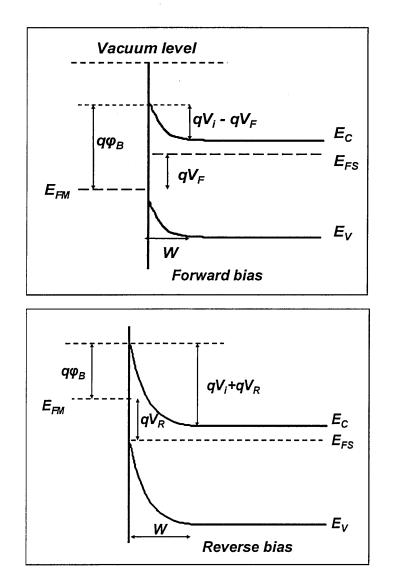

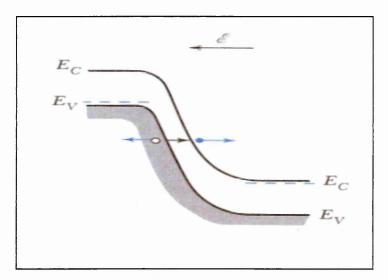

Chapter 4 describes the diode structure and operation focusing on p-n and Schottky diodes. Subsequently the experimental techniques used for the electrical characterisation of all the diodes in this project are described. These include Capacitance-Voltage (CV), Current–Voltage (IV), DLTS and LDLTS measurements.

Chapter 5 presents the fabrication and processing details of the p-n and Schottky diodes made for this project, both for the USJ and diamond structures. In addition, the technical details of the system used and the specification of the diodes are given.

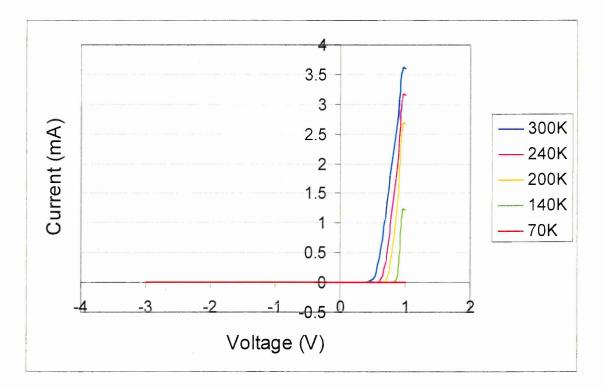

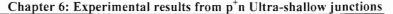

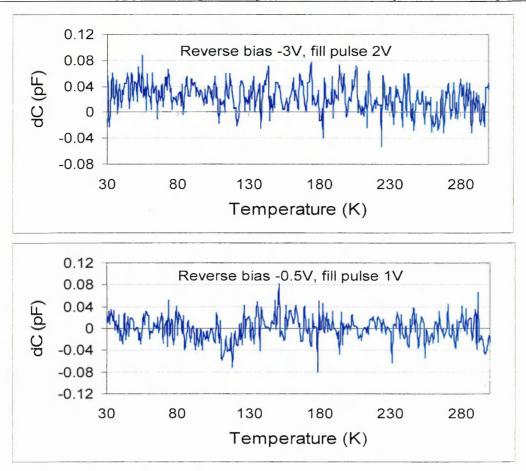

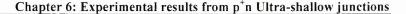

Chapter 6 shows the results of the electrical characterisation of the  $p^+n$  USJs on Si using CV, IV, DLTS and LDLTS.

Chapter 7 illustrates the results of the electrical characterisation of  $n^+p$  USJs using CV, IV, DLTS and LDLTS.

Chapter 8 demonstrates the results obtained from the characterisation of defects in the Schottky and p-n diode structures of diamond films on Si.

Chapter 9 summarizes the results and provides conclusions about the two very different semiconducting diodes investigated in this project. Conclusions are drawn about the defects present in Si USJs and in the diamond films deposited on Si. Finally future work based on these results is suggested.

## References

[1] M. J. Kelly, Low-Dimensional Semiconductors, Materials, Physics, Technology, Devices (Clarendon Press Oxford, 1995).

[2] D. V. Lang, Journal of Applied Physics 45 (1974) 3023.

[3] S. Matsumoto, Y. Sato, M. Kamo and N. Setaka, Japanese Journal of Applied Physics 21 Part 2 (1982) 183.

[4] P. W. May, Phil. Trans. R. Soc. Lond. A 358 (2000) 473.

## **Chapter 2: Defects in Silicon**

#### **2.1 Introduction**

Silicon is currently the most widely used semiconductor in the electronics industry and has been extensively examined for decades. This is because it is found in abundance in the earth's crust and very high purity silicon is now being produced. Silicon has a relatively small bandgap of ~1.14eV at room temperature which is suitable for controlling its semiconducting properties. The presence of impurities introduced on purpose or inadvertently, also affects the physical and electrical properties of silicon. Depending on the nature of these impurities, deep or shallow levels within the bandgap of silicon are formed. These often function as "stepping stones" for electrons to be promoted from the valence to the conduction band and hence contribute to conduction. As shallow impurities in Si are usually fully ionised, the concentration of carriers, when impurities are present, is different to that of intrinsic silicon. Impurities are therefore often used as a method to manipulate the conductivity of silicon devices. In addition, other defects such as point or extended defects or dislocations are commonly present after certain treatments. These can trap free carriers and hence have an overall effect on conduction.

Defects have usually a detrimental effect on the device properties, such as current leakage, which can lead to device degradation. In order to control the characteristics of Si devices, it is essential therefore either to prevent defect formation or to possess the ability to govern their behaviour. The purpose of this chapter therefore is to provide a detailed review of the research that has been performed on the study of defects in Si. In particular, the effects of irradiation and implantation are examined as these are the most commonly used methods for introducing foreign atoms into the Si lattice. Finally the effect of heavy implantation doses for the formation of ultra-shallow junctions is considered as it is a recent area of interest. The need for shallow junctions arises from the continuous effort to reduce the size of electronic devices, while maintaining control over the device properties and hence is an integral part of the modern semiconductor industry.

#### 2.2 Energy levels

At temperatures above absolute zero, some electrons in most semiconductors and in particular in Si, can acquire enough energy to cross the energy barrier from the valence to the conduction band. As the temperature rises the number of electrons promoted to the conduction band increases and consequently the number of holes left in the valence band increases accordingly. Apart from this thermal generation of electronhole pairs (e-h) other processes, such as optical and electrical excitation, can be used to create excess carriers and hence to increase the conductivity of the material. In thermal equilibrium however, the rate of thermal generation of e-h pairs is balanced by their recombination rate. This ensures that there is no excess population of electrons or holes and the overall conduction of the material is stable.

Recombination takes place by the electron dropping either directly back to the valence band, or to a deep level in the bandgap where it subsequently captures a hole from the valence band in order to complete the e-h annihilation process [1]. The energy released by either the direct or indirect recombination via energy levels can be dissipated in three ways. The radiative process entails the emission of a photon during recombination. The non-radiative process involves either emission of a phonon, where the energy is dissipated in the crystal lattice, or Auger recombination where the energy is imparted to a third mobile carrier (electron or hole). At a recombination centre, the probabilities of electron and hole capture are virtually equal in order to result in the elimination of the eh pair. Therefore their behaviour is more predictable and can be more easily controlled, which is vital for semiconductor devices. Efficient recombination centres often arise from metal impurities.

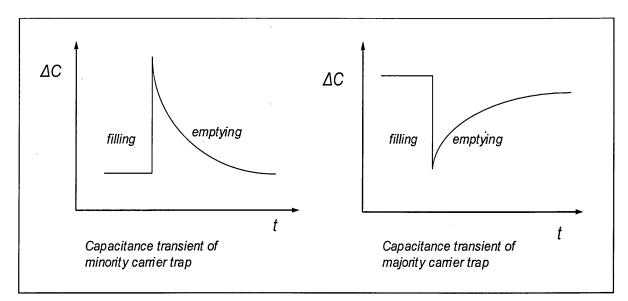

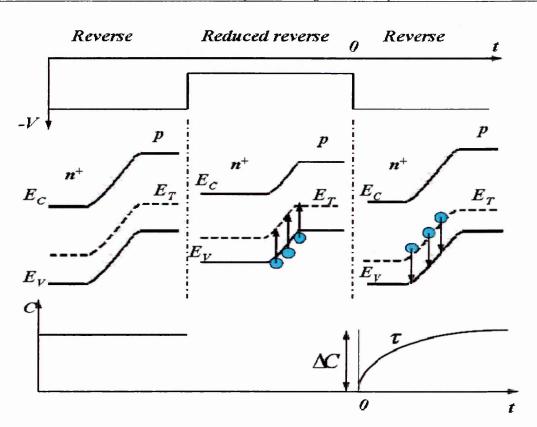

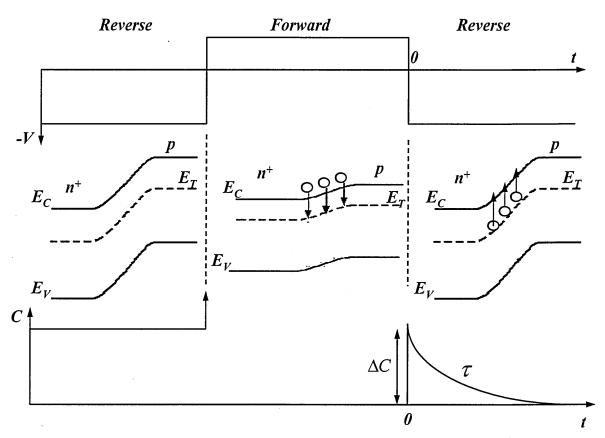

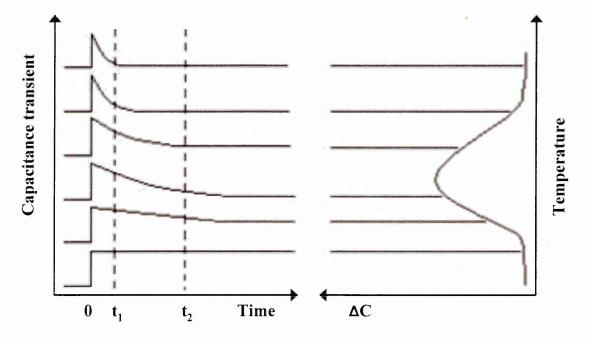

A deep level can act as a carrier trap or a recombination centre depending on its position in the bandgap and its emission or capture rate. Electron or hole traps have a high probability of capturing their respective carriers and releasing them after some time and under certain conditions. Therefore for instance at an electron trap the capture rate of an electron is much more dominant than the capture rate of a hole. Electron traps are therefore usually located closer to the conduction band, where electron capture and release can be more efficient. Similarly hole traps are usually closer to the valence band. In addition, electron traps are majority carrier traps in an n-type semiconductor

while hole traps are minority carrier traps. In the same way, in a p-type semiconductor hole traps are majority traps and electron traps are minority traps. Deep levels that behave as carrier traps have often a detrimental effect on semiconductor device characteristics. This is due to the fact that they alter the conductivity properties of the semiconductor by capturing free carriers and thus reducing the concentration available for conduction. The opposite effect of increased carrier density is experienced when carriers are released from traps and consequently conduction is enhanced. The major challenge associated with carrier traps in the bandgap of a semiconductor lies in effectively controlling the carrier capture and release, as well as predicting the trap's behaviour under specific conditions.

Shallow levels may also be present in the bandgap of a semiconductor and as the term implies, they are located closer to either the conduction or valence band than deep levels. In Si they usually originate by incorporation of atoms from the neighbouring groups III and V of the periodic table when these substitute Si atoms in the crystal lattice. Group V atoms have one electron in their outer shell that is not bound in a covalent bond and after replacing a Si atom they become donors as they can contribute this electron for conduction. Similarly group III atoms are acceptors in Si since they introduce holes and cause p-type conductivity. Donors are positive when ionized since they are missing their extra electron and acceptors have a negative charge when ionized as they have gained an electron. Shallow donor or acceptor levels in Si saturate the conductivity above 150K as they are then fully ionized.

Very commonly in Si, deep level defects are introduced by impurities belonging to groups of the periodic table other than III and V. However, intrinsic deep levels such as vacancies and interstitials are almost definitely present after certain processes used for semiconductor device fabrication and doping. High-energy particle irradiation and ion-implantation cause a wide range of lattice defects that introduce deep levels and quite frequently extended defects in the bandgap. Other techniques such as diffusion and oxidation can also increase the concentration of recombination centres. These affect many of the properties of the semiconductor and govern conduction, as will be seen in the following sections. Nonetheless they are essential for the doping or optimization of

the characteristics of semiconductors and much research has been performed to properly analyse the defects they produce.

#### **2.3 Crystal Defects**

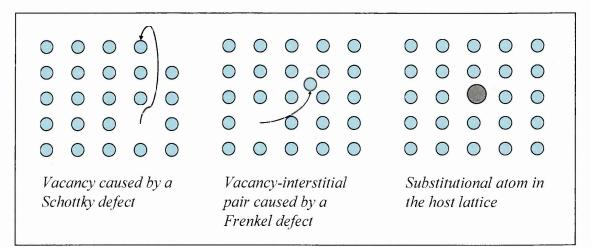

Ideally the atoms in a semiconductor occupy specific lattice sites and are arranged in a periodic manner. However in real crystals, the presence of lattice defects or the thermal vibration of atoms can cause deviation from periodicity. Such imperfections include point or extended defects and dislocations. As the nature of these defects becomes more complicated, it is harder to control the properties of the semiconductor. There are three basic point defects that are currently important to investigate, namely vacancies, interstitials and substitutional impurities. A vacancy, as the word implies, appears when an atom moves away from its regular site. Even though vacancies are due to lack of an atom, they can carry electronic charge in the same manner that a hole is positively charged because it is the lack of an electron. Interstitials are atoms that sit on an interstitial site in the crystal and can be either from the same element as the crystal (self-interstitials) or from a different species. Substitutional impurities are atoms of a different species that substitute atoms of the host element in the crystal lattice and bond with them in a regular fashion, usually introducing new states in the bandgap. When an atom leaves its regular site and migrates to the surface leaving a vacancy behind, it is called a Schottky defect, while if an atom moves away from its site to occupy an interstitial site creating a vacancy-interstitial pair, it is then called Frenkel defect [1, 2]. An illustration of these defects is shown in Fig. 2.1

Figure 2.1: Schottky, Frenkel and substitutional defect in a semiconductor lattice

In Si in particular, these defects can be present during growth and their concentration is relatively small. However, if implanted, the most common way of introducing them on a larger scale is by doping. Doping is very important as it allows blending of the properties of two elements or more and hence can enhance the characteristics of the semiconductor. Most importantly, it is necessary for the formation of p-type and n-type semiconductors and hence for the fabrication of most semiconductor devices. However, the doping atoms inevitably cause displacement of the host atoms and introduce new energy states in the bandgap. In addition, as dopants are forced into the crystal, they increase the concentration of vacancies, interstitials and substitutional atoms. The atoms of heavier impurities more frequently occupy substitutional sites, while lighter atoms can most commonly be found at interstitial sites [1]. Although point defects appear to be the simplest form of crystal imperfection, they can often be found in larger aggregates. They can therefore form clusters of defects which have a much more complicating nature and are harder to examine or eliminate.

Dislocations are line defects that form when stress higher than the elastic limit of the crystal is applied. In this case, part of the crystal can slip relative to another part of the crystal forming dislocations. When the slip occurs in the direction of the applied stress, screw dislocations can be formed. However, if the atomic plane where the slip takes place is at right angles to the direction of the applied stress, then edge dislocations are created [1]. Moreover, the high impurity content formed by implantation damage may result in dislocation loops. Dislocations exhibit a dynamic behavior, as they can interact with other dislocations, they can change with the application of further applied stress or heating treatment and they can also dissociate into partial dislocations. Therefore they affect the electrical properties of the semiconductor by introducing electronic states in the bandgap in relation with other impurities or near the dislocation core. These are caused by dangling bonds that are created when dislocations form or dissociate. In addition, excess strain is imposed on the lattice due to an electric field around the dislocations [3]. Hence dislocations have an impact on the carrier lifetime, density and mobility in a semiconductor.

Another type of defect is a stacking fault, which is associated with the way the atoms bond in the crystal lattice. A stacking fault is generated when the sequence, with which

the atoms are bonded in the lattice of the semiconductor, is altered. Higher complexity defects such as twinnings and inclusions are called gross defects as they can involve several atomic planes. A twinning is identified as one part of a crystal forming a mirror image of another adjacent part, while the two parts remain in contact at the bounding surface. Twinning usually encompasses a high concentration of dislocations and can be formed due to mechanical shear. During growth, small particles of metals or dielectrics, called inclusions, can be absorbed into the crystal. Inclusions often interact with dislocation sites by forming precipitates. Inclusions have been observed at substitutional sites in Si after ion implantation of heavy metallic atoms, after spontaneous precipitation of the metal impurity located at the peak of the implant [4]. Twinning and inclusions during Si growth can be more easily prevented, as the conditions for their formation can be controlled and mechanical shear or metal impurities can be avoided. However, dislocations and stacking faults may occur even under normal growth conditions and can be generated in particular by the required doping process. Ionimplantation damage may not only create dislocations and stacking faults, but may also lead to even more stable extended defects after their interaction with point defects or after annealing.

Dislocations, as well as their interaction with point defects, have been extensively examined in silicon. In addition, Si deformation has been shown to produce point defects apart from dislocations, while the activation energy of the resulting defects depends on the initial strain applied and the doping of the material [5]. However, the majority of point defects generated during the applied strain can be annealed-out at high temperatures (~900°C), which enables a more precise study of the dislocations. Low temperature annealing of Si under stress appears to straighten the dislocation networks, though high temperature annealing after deformation decreases their density. The importance of controlling the deformation strain and temperature is emphasized by the fact that high deformation levels lead to more dangling bonds [3]. This may lead to acceptor states in n-type Si which in turn can cause Fermi level pinning below the mid-bandgap [5].

Various techniques have been implemented for the investigation of the nature, properties and electrical activity of dislocations, as well as to study their dissociation

and interaction with other defects. Transmission Electron Microscopy (*TEM*), Scanning Electron Microscopy (*SEM*) and Hall effect measurements can provide information on the dislocation density, structure and number of carriers captured on dislocation levels respectively [6, 7]. Electron-Paramagnetic Resonance (*EPR*) has been extensively applied to plastically deformed Si in order to examine the paramagnetic centres (*D*-*centres*) that are created during deformation. EPR results have been combined with Deep Level Transient Spectroscopy (*DLTS*) and the Electron Beam Induced Current (*EBIC*) mode of SEM in order to determine the electrical activity from dislocations and their capture and emission characteristics [6-9].

The D-centres that have been observed at the core of dislocations after deformation, have been shown by EPR to be associated with dislocation dangling bonds [7]. This result can be expected, since dislocations stem from broken crystal bonds along a lattice plane, but it also demonstrates that D-centres are localized in dislocation cores or in their vicinity. Of course the obtained EPR signal from such plastically deformed material may be due to the dangling bonds near or inside dislocations or may be due to clusters of point defects situated elsewhere in the crystal [8]. Therefore techniques such as DLTS that investigate the capture kinetic processes from defects are necessary to resolve the nature of these defects. Due to the fact that defects at a dislocation core are in very close proximity, carrier capture can be described as preferential. Hence the initial capture process may appear point-defect like, but only certain defects are filled that perhaps are located at more electrostatically favorable positions at the dislocation. Following this initial capture, a strong repulsive Coulomb potential will develop around the dislocations, which will gradually prohibit further carrier capture [7]. As this electrostatic potential varies continuously with time during carrier capture or emission, the resulting transient process will deviate from a typical exponential. In fact this nonexponential capture has been observed to have logarithmic time dependence as the number of filled deep levels is proportional to the logarithm of the filling time [8]. DLTS can still be used in such cases since relevant models have been developed for logarithmic transients from defects in heterostructures or alloys that can also be implemented in Si [8, 10, 11]. The electric field that arises in the depletion region of the semiconductor during DLTS measurements, can have the effect of slightly lowering the

height of the potential barrier around the dislocations, thus improving carrier capture or emission, or it can induce tunneling [7, 12].

As already mentioned, the density of dislocations in Si decreases after annealing because they dissociate into partial dislocations [5]. The EPR signal and DLTS spectra associated with D-centres appear reduced after annealing, which leads to the conclusion that reconstruction of dangling bonds at the dislocation core or around the dislocation has taken place [7]. DLTS spectra reveal that deep levels originating from point defects or point defect clusters usually disappear after high temperature annealing, if the defects are not located inside or close to dislocation sites. A similar reduction in the DLTS spectrum has been observed after annealing of deformed Si containing metallic impurities [9]. Metallic impurities are known to segregate or precipitate at dislocations giving rise to deep levels that severely affect the minority carrier lifetime [9, 13]. Impurities such as Fe, Ni, Cu and Au tend to form bonds with common Si dopants (e.g. B) and cause a decrease in the carrier lifetime when these bonds are broken. It has been observed that impurities at a dislocation core may have different electronic properties than in the ideal Si lattice. In particular, research on Ni contamination of Si containing dislocations has revealed that Ni creates energy states in a broad band instead of giving rise to a single energy level [9]. Finally, under the influence of an electric field introduced by techniques such as DLTS, redistribution of metallic impurity atoms along dislocations has been detected.

Despite the fact that defects caused by dislocations are very difficult to characterize, their interaction with point defects may also lead to electrically active levels. At dislocation cores there is much higher defect diffusivity than at other parts of the crystal and vacancies tend to migrate there. Glide dislocations dissociate into Shockley partials which are separated by stacking fault ribbons [6, 14]. Stacking fault ribbons however, have been reported to also participate in the vacancy migration mechanism [15]. Moreover as their size is larger than that of dislocations, any electrical activity from stacking fault ribbons would dominate the electrical behaviour of the semiconductor. As determined from EBIC analysis, stacking fault ribbons do not exhibit any significant electrical activity at room temperature even though their identification becomes difficult due to their low energy [6]. However, it is found that at stacking faults, the formation

energy of vacancies and self-interstitials, such as the [110]-split interstitial in Si, is lower than in the bulk [14]. This usually stems from the fact that at the stacking fault the point defect lies in a more relaxed structure than in the regular crystal lattice. A direct consequence of the lower formation energy of these defects at a stacking fault, is that after irradiation the latter could act as a sink for point defects. Hence after irradiation, the concentration of defects at stacking faults might be higher compared to that at dislocation cores [14]. The most important defects caused by the main doping technique in Si, namely ion-implantation will be examined in the following sections. Finally, high energy irradiation, such as that which occurs in particle detectors, will initially be considered.

#### 2.4 Irradiation-related defects in Si

During irradiation of Si high energy particles, such as electrons, protons or neutrons are directed onto the semiconductor, collide with the host atoms and create an excess of Frenkel defects. These vacancies and interstitials are mobile at room temperature and thus migrate to different parts of the crystal. No excess ions are introduced through irradiation and the majority of the produced vacancy-interstitial pairs recombine in the bulk or at the surface. However, vacancies or interstitials that have avoided recombination either aggregate forming clusters or interact with impurities already existing in the crystal such as the commonly found C or O, P or B, depending on the conductivity of Si. Some of the resulting defects are stable and immobile at room temperature and tend to anneal out just above room temperature often leading to the formation of higher order defects or even extended defects. Nonetheless, irradiation is a useful excess carrier lifetime control technique which has been extensively used in industry since it can be applied after device fabrication. Although, recombination centres formed by irradiation are useful for controlling the device properties, they have been shown to anneal out, not only at high temperatures, but also with time [1].

#### **2.4.1 Defects in p-type irradiated Si**

A multitude of defects have been detected using a wide range of techniques in irradiated Si. The main defects induced by electron (*e*) irradiation in p-type Si include the divacancy signal, the carbon-oxygen-vacancy (*COVV*) level, sometimes referred to as the K-centre and the carbon substitutional-carbon interstitial pair ( $C_s$ - $C_i$ ). These

defects are not always present depending on the resistivity of Si used, the irradiation temperature and dose and the annealing treatment. Studies of carrier lifetime after electron bombardment of p-type Si, have revealed a level at ~0.21eV above the valence band, ascribed to the positive charge state of the divacancy, common to low resistivity, oxygen and carbon lean crystals [16]. Recombination in high resistivity e-irradiated crystals has been shown to be dominated by a level at 0.27eV attributed to the K-centre [17]. However, the position of this centre in the bandgap of p-type Si is usually measured at 0.35-0.38eV by other studies, thus differing in value, as Electron Paramagnetic Resonance (*EPR*), Deep Level Transient Spectroscopy (*DLTS*) and Thermally Stimulated Capacitance (*TSCAP*) techniques have shown [16, 18-20]. Under high-injection conditions the K-centre is positively charged and remains at this charge state for some time after the bias is turned off, resulting in an increase in the effective doping concentration [18, 21].

EPR and DLTS studies have shown a correlation between the K-centre and the Cs-Ci pair in p-type electron irradiated Si. The latter defect is formed when a mobile Si interstitial is trapped by a substitutional carbon, resulting in an interstitial carbon after annealing just above room temperature which is subsequently trapped by another substitutional carbon. Upon further annealing, DLTS revealed that the Cs-Ci peak at ~0.27eV above the valence band reduces while at the same time the K-centre peak at 0.39eV increases [22]. Hence it was proposed that annealing causes the breaking of the  $C_s$ - $C_i$  pair after which the carbon-interstitial enhances the concentration of the K-centre. Similarly, in p-type proton  $(H^{\dagger})$  irradiated Si, DLTS measurements revealed a carbonoxygen interstitial complex  $(C_iO_i)$  with activation energy at 0.35eV above the valence band. This level is present at low concentrations immediately after the H<sup>+</sup> bombardment, although its concentration increases with time [23]. The concentration of the Cs-Ci pair at 0.27eV however, reduces accordingly, indicating that the Ci is responsible for the growth of the C<sub>i</sub>O<sub>i</sub> complex in what appears to be an almost linear Hence the carbon interstitial is responsible for increasing the transformation. concentration of the K-centre in p-type electron irradiated Si, while in proton irradiated p-type Si it has the same effect on the carbon-oxygen interstitial complex.

In hydrogenated p-type e-irradiated Si another level has been detected with activation energy 0.28eV above the valence band [24]. This level only arises after annealing and is suggested to result from the hydrogenation of the K-centre and hence is due to a hydrogen-related complex, most likely attributed to the donor state of VOH. Electron traps have also been detected in p-type e-irradiated Si after annealing at 0.27eV below the conduction band, ascribed to an interstitial defect of oxygen and boron [19].

#### 2.4.2 Defects in n-type irradiated Si

The identification of defects in n-type irradiated Si is much better documented due to the extensive research that has been performed. The main defects introduced both by electron and proton irradiation in n-type Si are the vacancy-oxygen (VO or A*centre*), the doubly negative charge state of the divacancy  $(V_2^{-})$  and the singly negative charge state of the divacancy  $(V_2)$  [25-28]. The A-centre is formed when migrating monovacancies, which are mobile at room temperature, get captured by interstitial oxygen atoms  $(O_i)$  and its activation energy has been determined by a vast amount of studies at ~0.18eV below the conduction band [29-32]. The A-centre has a large capture cross-section  $(9*10^{-15} \text{ cm}^2)$  and can often be used as a monitor of the concentration of vacancies since  $O_i$  is usually the main impurity in Si [30]. The same studies yielded an activation energy of 0.23eV for the double negative charge state of the divacancy and 0.41eV for the singly negative charge state. It was found that the surface of irradiated n-type Si acts as a sink for vacancies, while their concentration increases with depth up to a saturation value and then remains constant for larger depths [25]. In addition, it was observed that the production rate of divacancies decreases at Furthermore, studies of vacancy related defect high electron irradiation doses. production yielded a decreasing tendency with increasing proton irradiation flux [26].

Interaction of vacancies with dopants usually yields a vacancy-dopant centre. In particular in n-type e-irradiated Si the phosphorus-vacancy centre (VP or *E-centre*) is very commonly found and has been detected at ~0.45eV below the conduction band. The fact that it is located very close to the single negative divacancy level (0.41eV) means that it is difficult to resolve through typical electrical studies. However, the implementation of high resolution techniques, such as Laplace DLTS (*LDLTS*) and the

fact that the dissociation energy of the E-centre (at ~180°C) is lower than that of the divacancy have allowed the separation of these two levels [27, 29]. In n-type e-irradiated Si of high carbon content an additional defect is usually resolved overlapping with the A-centre that originates from a carbon substitutional-carbon interstitial pair and has an activation energy ~0.16eV below the conduction band [20, 27]. In addition, after annealing intended to dissociate the E-centre, the C<sub>s</sub>-C<sub>i</sub> complex also reduces in concentration in e-irradiated n-Si, while the formation of a new C<sub>s</sub>-C<sub>s</sub> level at 0.21eV below the conduction band is revealed [33]. High annealing temperatures above 350°C in n- and p-type Si can result in thermal double-donors being formed. These have an effect on the doping concentration as they are usually very shallow levels and can therefore exchange carriers very easily with the conduction or valence band [18].

In the case of proton-irradiated n-type Si, apart from the typical vacancy-related defects other hydrogen-related levels have been detected [26, 34]. These are located at 0.32eV and 0.45eV below the conduction band. The former level exhibits similar annealing behaviour to the well-characterised VO centre and appears in samples with high oxygen content. Therefore it was attributed to a VOH complex. The same conclusion, concerning the level at 0.32eV was reached by hydrogenation of e-irradiated n-type Si [24, 35-37]. Hydrogenation has the effect of passivating the VO centre and hence reducing its concentration while introducing a level deeper in the top half of the Si bandgap. The VOH complex has an emission rate that is lower than that of the A-centre as was determined by LDLTS analysis [36].

The second hydrogen-related level at 0.45eV is located near the singly negative divacancy level and the E-centre but has been successfully resolved and attributed to a V<sub>2</sub>H complex [34, 36]. It exhibits similar annealing behaviour to the divacancy in particular in oxygen lean samples and does not appear after helium irradiation which indicates that it contains hydrogen. EPR and LDLTS studies have revealed a VH complex almost with the same activation energy as the V<sub>2</sub>H complex and close to the E-centre. Finally, higher order vacancy-hydrogen complexes (VH<sub>2</sub>, VH<sub>3</sub>, VH<sub>4</sub>) have been identified using Fourier Transform Infra-red spectroscopy (FTIR) in proton or deuterium irradiated n-type Si [38].

Neutron irradiation has also been applied to Si detectors exhibiting typical vacancyrelated defects such as the A-centre and the different divacancy charge state defects [39]. A much deeper level at ~0.54eV below the conduction band, which was attributed to a different charge state of the double vacancy was detected, as well as two deep levels closer to the valence band. As will be examined in the following section, high energy particle-irradiation may introduce crystallographic defects, which may lead to the presence of extended defects.

#### **2.5 Ion-implantation defects**

Ion-implantation is the bombardment with different ion species intended to produce Si with certain properties. It is the most widely used technique at present for the doping of Si and hence for controlling its conductivity and for the formation of semiconductor devices, although less aggressive plasma doping is being developed by equipment manufacturers. A very broad range of dopants has been employed including the main dopant impurities B, P, As, C and Sb. Others such as Si, Ge, Sn, and Er are used for pre-amorphizing implants, light emitters or to increase radiation hardness in detectors. Very frequently throughout the literature, ion implanted Si is compared with e- or proton irradiated Si in order to distinguish between the main defects and impurity related defects. However, the significant difference between irradiation with electrons (or protons) and ions, is that in the latter case the ion stays in the sample creating a further defect. Once again in ion-implanted Si, due to the bombardment with foreign species, vacancies and interstitials are created by the collisions that are very mobile at room temperature and may therefore form other defects. In addition, subsequent annealing is necessary for the activation of the dopants and often results in more stable or higher order defects. The very frequently observed phenomenon of Transient Enhanced Diffusion (TED) of B or other dopants, involves diffusion of the dopant species away from the implanted region very rapidly. This results in a very broad profile and is the origin of formation of complicated extended defects. In modern semiconductor technology where very well contained dopant profiles are required offering the possibility of reducing the device dimensions, TED of dopants is undesirable and will be examined in the following section in detail.

Typically the same vacancy-related defect levels are created in ion-implanted and irradiated Si, although vacancy clusters may also arise. The VO centre and the different charge states of the divacancy are usually present, as well as the vacancy-dopant (E centre) level located very close to the singly negative divacancy. In n-type B implanted Si, the substitutional carbon-interstitial carbon complex is also detected overlapping with the A centre [30]. Another level arises at 0.35eV below the conduction band which is usually detected as a long tail extending at lower temperatures next to the singly negative divacancy defect in a DLTS spectrum. This level has been reported in B, C or Si doped n-type Si and is being associated with a low order defect containing carbon [31, 32, 40, 41]. The concentration of this level with depth revealed that it has a broader profile extending towards the surface than the singly negative divacancy level, indicating that it is not due to migrating vacancies but less mobile species such as carbon which may form carbon interstitials and hence interact with impurities. Due to the fact that it appears to anneal out at low temperatures (150°C), it is more likely that it is not due to a complex of carbon involving divacancies [32]. However, this level is not present after implantation with heavier dopants such as Sn [40].

Vacancy-related defects caused by ion-implantation of different mass atoms have shown that the implantation temperature has an effect on the production rate of the vacancies. In particular, as the implantation temperature increases the concentration of defects involving vacancies increases [40]. Moreover the concentration of vacancy-related defects increases with dose rate for light dopants. For higher mass dopants, a threshold dose rate was observed after which the production rate of vacancies decreased with increasing dose rate. This is ascribed to the fact that the interstitials originating from heavier dopants require more time to diffuse due to the long collision cascades and can therefore recombine with vacancies faster [41].

Detailed research has been performed in detecting clusters of defects arising from ionimplantation before annealing in an effort to predict stable complex levels caused by annealing. Dopants of increasing ion mass (Si, Ge, Er) revealed high concentration of defects located at ~0.4eV below the conduction band which was shown to originate from a complex of defects rather than a point defect [27, 42, 43]. Analysis of these levels with high resolution LDLTS and capture cross-section measurements while

varying the fill pulse length, demonstrated exponential capture with time, indicating a complex of defects or an extended defect that was not removed by annealing. Earlier work on Er implanted Si had shown a multitude of donor states whose luminescence was shown to increase after annealing [44]. A multitude of interstitial clusters was also observed both in n- and p-type Si after high temperature annealing [45].

A different study on metal impurities and the distinction between two very close spaced levels was achieved by LDLTS measurements of Au in n-type Si [46]. This work did not involve ion-implantation but diffusion of Au and subsequent hydrogenation of the surface. However, it is mentioned here to discuss defect levels arising from the incorporation of Au and to demonstrate the high resolution capability of LDLTS. One of the four charge states of the Au-H complex in n-type Si, namely the G4 complex, is believed to have a very similar electrical signature as the Au acceptor level estimated between 0.55-0.56eV below the conduction band. LDLTS allowed the accurate spatial identification of the G4 complex and the gold acceptor at ~0.54eV and ~0.56eV respectively below the conduction band [46, 47].

In p-type Si implanted with a high dose of C a defect level not involving vacancies was detected at 0.41eV above the valence band possessing a large capture cross section [48]. Upon annealing, the initial level that exhibited interstitial behaviour was seen to cluster with oxygen interstitials forming the C<sub>i</sub>O<sub>i</sub> interstitial complex at ~0.38eV above the valence band. Complex behaviour was observed after DLTS measurements for the formation and evolution of this level [48, 49]. Exponential capture with time was detected and a large capture cross-section after high temperature annealing at 450°C indicating the stability of this level at high temperature. Implanted p-type Si has been shown to yield complex levels related to the background B doping. In particular, at 0.26eV above the valence band a boron interstitial–carbon substitutional complex ( $B_iC_s$ ) has been revealed. Another deeper level at 0.45eV above the valence band can also be detected and is attributed to an interstitial complex that embodies B [28]. These levels arise when the B content is significantly larger than the carbon concentration. In this case interstitial B will be formed rather than interstitial carbon which promotes the formation of B–related levels.

Low dose implantation of p-type Si with different atoms, including H, B, Si and Ge, indicated that the defects produced are not related to the dopant impurity, contrary to n-type Si implanted with H where the VOH and V<sub>2</sub>H complexes are formed [50]. Apart from the positive charge state of the divacancy and the  $C_iO_i$  interstitial complex that are well characterised, another deep donor level is present at 0.52eV above the valence band, possibly due to a metallic impurity incorporated during growth, such as Cu. The resulting level may be due to an interaction between the carbon-oxygen interstitial and the metal impurity. At increased implantation doses however, the concentration of the seemingly point defect-like levels increases to a point that higher order complexes are formed [49, 50].

High resolution studies of the vacancy-dopant level arising around 0.44eV below the conduction band for different dopants (P, As, Sb), were successful in separating these levels from the divacancy as well as differentiating amongst these, when a combination of dopants were implanted in the same sample [51]. This clearly demonstrated the efficiency of the LDLTS technique although it was noticed that the presence of many implants in the same sample, have the effect of altering the electrical signature of the E-centres compared to single or double implants. Finally a breakthrough study involving a combination of DLTS and Minority-carrier transient spectroscopy (*MCTS*), revealed the presence of a donor level in the bandgap of Si attributed to the phosphorus-vacancy level [52]. This donor level is located at 0.27eV above the valence band and its detection was possible due to the injection of both minority and majority carriers achieved optically through MCTS. The presence of this level will affect the modelling of dopant diffusion in Si which is known to be associated with the E-centre.

#### 2.6 Transient Enhanced Diffusion

It has been observed that ion-implantation results in the formation of a vacancyrich region extending from the surface of the implanted Si to the peak of the implant and a subsequent interstitial-rich region until the end-of range of the implant [28, 30]. Moreover studies have shown that the dopant concentration arising from ionimplantation is not always contained in the original implanted region, but dopants such as B tend to diffuse deeper into the substrate. An anomalous transient diffusion is particularly observed after high temperature, short-time anneals which leads to

broadened B profiles [53]. This phenomenon comes in contrast to the well-controlled, steep dopant profiles that are required for shallow-junction fabrication required by the downscaling of semiconductor devices. For B doping in particular, it is known that after implantation, substitutional B atoms are introduced in the host lattice which then tend to diffuse away from the implanted region. This is achieved because the B atoms are known to couple with interstitial Si atoms, which were generated during implantation. Hence, the now mobile, B interstitial complexes cause dopant diffusion [54].

Unlike irradiation with high energy particles which eventually does not introduce any foreign atoms in the host lattice, ion implantation causes an increase in the concentration of charged ions, mobile or immobile, at the particular implantation temperature. These interact with the created vacancies and interstitials often causing their annihilation while a residual interstitial population is usually observed in the aftermath, even following sufficient annealing upon which most vacancy-related defects have dissociated. Moreover, rapid thermal annealing (RTA) is known to cause the initial clusters of defects that were created during implantation to agglomerate into larger clusters [53]. Dissociation of these clusters results in the release of trapped interstitials increasing their concentration. Since point defects such as interstitials, are highly mobile they tend to enhance transient dopant diffusion. An additional trapping of host interstitials is caused by extended defects when they are present after high temperature annealing. A variety of techniques, such as TEM, Secondary Ion Mass Spectrometry (SIMS), DLTS and photoluminescence (PL) have been implemented for the observation of Transient Enhanced Diffusion (TED) in Si and for the identification of its origin [49, 55-58].

High resolution images have shown that large extended defects can exist in the region of the implant where transient diffusion is taking place. These were identified as rod-like or {311} defects, although after higher energy implants or higher temperature anneals even dislocation loops may be distinguished [58]. These {311} defects are formed through precipitates of interstitials and are known to unfault into dislocation loops after very high temperature annealing [59]. The {311} defects trap Si interstitials that have diffused into the bulk after the initial dissolution of point defect clusters that were

formed during implantation. During annealing these defects undergo Ostwald ripening which involves constant capture and emission of interstitials leading to a saturated concentration and subsequent re-emission of interstitials. The concentration of {311} defects eventually reduces during annealing while their size has been observed to increase [58]. As these interstitials diffuse away into the bulk or towards the surface they couple with dopants thus generating mobile dopant interstitials, which then diffuse away causing enhanced diffusion [54]. Less dopant diffusion has been observed for high carbon containing Si, as interstitials pair with carbon instead, resulting in fewer mobile interstitial-dopant pairs.

A number of interstitial clusters of defects have been observed after implantation and annealing of p-type and n-type Si [45]. When the implantation dose increases, a higher interstitial population is available resulting in the formation of more thermally stable clusters. The same result is also reached when lower impurity concentration is ensured as fewer interstitials are trapped by impurities. A wide range of studies have been performed in order to produce reduced TED in B doped Si. Recently  $F^+$  implantation has been shown to eliminate TED and even reduce B thermal diffusion. Dislocation loops in the interstitial region of the fluorine implant are presumed to trap interstitials and hence reduce TED. Similarly small vacancy-fluorine clusters are suggested to contribute to the suppression of B thermal diffusion [60-62].

#### **2.7 Ultra-Shallow Junctions**

The general trend of reducing the size of integrated circuits (ICs) requires a reduction in the size of devices and as a direct consequence the semiconductor device dimensions also have to shrink. This also increases the device packing density and frequency response and the current drive. The latter inversely depends on the channel length (L) of Metal-Oxide-Semiconductor-Field-Effect-Transistors (MOSFETs). As the electric field throughout the device should be maintained constant, reducing L, causes a roll-off of the threshold voltage which can be diminished if the junction depth is also decreased. This is the main drive behind the constant need for achieving shallower junctions. In the simple diode configuration, this also means a reduced depletion region width which can be accomplished if high doping concentration is implemented. However, careful adjustment of the doping conditions is necessary in order to control

the depth of the junction and methods for eliminating TED are of high technological importance.

Different methods have been devised for the formation of ultra-shallow junctions (USJs). Plasma immersion, where the substrate to be doped is immersed in plasma containing the dopant species before high voltage is momentarily applied, is one of the techniques investigated. It is a quick and inexpensive method requiring only low implantation energy and has been applied using a AsH<sub>3</sub> plasma source. Due to the use of arsenic, a steep concentration-depth profile was achieved near the  $\sim 90$ nm wide n<sup>+</sup>p junction with the substrate and a two-step anneal ensured dopant activation [63]. Electrical characterisation was performed using current-voltage measurements and it was concluded that low implantation energy (<10keV) and long anneal times (>60s) may result in junctions containing less trap centres [63]. 50nm-wide p<sup>+</sup>n USJs were realised by decaborane ion implantation and demonstrated promising results by exhibiting low TED and thermal diffusion of B [64]. Low energy (5-15keV) As ion implantation was performed for the formation of  $n^+p$  USJs followed by high temperature (650-950°C) annealing and TEM was used for the analysis of extended defects at the implantation end-of range. Dislocation loops were detected, with increased density for higher temperature anneals, which also dissolved at higher temperatures for higher energy implants. Lower energy implants resulted in shallower dopant concentration profiles which also exhibited less As-TED with however higher sheet resistance [65].

Point defect engineering has been used by high energy Si co-implantation to inject vacancies in ion-implanted Si which eventually annihilate part of the interstitial population and result in reduced TED and sharper junctions [66]. A different study examined the effects of B implantation into preamorphised Si followed by solid-phase epitaxial growth (*SPEG*) which showed that self-interstitial emission from the implanted layer occurring during SPEG controls dopant-interstitial clustering [67]. Finally ultralow energy ion-implantation, in the order of 500eV-1keV, has been investigated for the formation of shallow junctions where low sheet resistance values were achieved [68]. The challenge in such a low energy regime is developing appropriate annealing schedules yielding high dopant activation.

## **2.8** Conclusion

This chapter initially discussed the main properties of deep and shallow levels as well as recombination centres in Si. Doping and impurity incorporation were considered next, as well as the generation and identification of point defects. A wide range of crystallographic and impurity-induced extended defects, such as dislocations, stacking faults and inclusions were presented. These are often found after the intensive processing and doping methods required by the current semiconductor device fabrication. The defects generated by irradiation and implantation were investigated extensively and phenomena such as transient-enhanced diffusion of dopants were considered. These have a serious effect on the device performance, ability to control dopant activation, and eventually the size of the devices required to provide high efficiency structures. Finally, the requirements for ultra-shallow junction-based devices were given and methods that have lead to successful implementation of such structures were detailed, while certain challenges associated with such efforts were outlined.

## References

[1] M. S. Tyagi, Introduction to semiconductor materials and devices (John Wiley & Sons, Inc, Kanpur, India, 1991).

[2] S. M. Sze, Semiconductor Devices Physics and Technology, 2nd Edition (John Wiley and Sons, Inc., 2002).

[3] J. Weber, Solid State Phenomena 37-38 (1994) 13.

[4] V. S. Touboltsev, E. Johnson, U. Dahnen, A. Johansen, L. Sarhlot and S. Q.Xiao, Materials Science Forum 269-272 (1998) 345.

[5] L. C. Kimerling and J. R. Patel, Applied Physics Letters 34 (1979) 73.

[6] A. Ourmazd, P. R. Wilshaw and G. R. Booker, Physica B 116 (1983) 600.

[7] V. V. Kveder, Y. A. Osipyan, W. Schröter and G. Zoth, physica status solidi (a) 72 (1982) 701.

[8] P. Omling, E. R. Weber, L. Montelius, H. Alexander and J. Michel, Physical Review B 32 (1985) 6571.

[9] V. Kveder, W. Schröter, M. Seibt and A. Sattler, Solid State Phenomena 82-84 (2002) 361.

[10] P. Omling, L. Samuelson and H. G. Grimmeiss, Journal of Applied Physics 54 (1983) 5117.

[11] P. N. Grillot, S. A. Ringel, E. A. Fitzgerald, G. P. Watson and Y. H. Xie, Journal of Applied Physics 77 (1995) 3248.

[12] J. Frenkel, Physical Review 54 (1938) 647.

[13] T. S. Fell, P. R. Wilshaw and M. D. D. Coteau, Physica Status Solidi (a) 138 (1993) 695.

[14] A. Antonelli, J. F. Justo and A. Fazzio, Physical Review B 60 (1999) 4711.

[15] J. Huang, M. Meyer and V. Pontikis, Physical Review Letters 63 (1989) 628.

[16] J. W. Walker and C. T. Sah, Physica Status Solidi (a) 11 (1972) 513.

[17] D. Bielle-Daspet, Solid-State Electronics 16 (1973) 1103.

[18] R. Siemieniec, F.-J. Niedernostheide, H.-J. Schulze, W. Südkamp, U. Kellner-Werdehausen and J. Lutz, Journal of Electrochemical Society 153 (2006) 108.

[19] P. M. Mooney, L. J. Cheng, M. Süli, J. D. Gerson and J. W. Corbett, Physical Review B 15 (1977) 3836.

[20] A. R. Peaker, J. H. Evans-Freeman, L. Dobaczewski, V. Markevich, O. Andersen, L. Rubaldo, P. Y. Y. Kan, I. D. Hawkins, K. Gościński and K. B. Nielsen, Invited Review Electrochemical Society Meeting DECON (September 2001).

[21] R. Siemieniec, H.-J. Schulze, F.-J. Niedernostheide, W. Sudkamp and J. Lutz, Microelectronics Journal 37 (2006) 204.

[22] Y. H. Lee, L. J. Cheng, J. D. Gerson, P. M. Mooney and J. W. Corbett, Solid State Communications 21 (1977) 109.

[23] J. Lalita, N. Keskitalo, A. Hallen, C. Jagadish and B. G. Svensson, Nuclear Instruments and Methods in Physics Research B 120 (1996) 27.

[24] O. Feklisova, N. Yarykin, E. Yakimov and J. Weber, Physica B 273 (1999) 235.

[25] B. G. Svensson and M. Willander, Journal of Applied Physics 62 (1987) 2758.

[26] A. Hallén, D. Fenyö, B. U. R. Sundqvist, R. E. Johnson and B. G. Svensson, Journal of Applied Physics 70 (1991) 3025.

[27] N. Abdelgader and J. H. Evans-Freeman, Journal of Applied Physics 93 (2003)5118.

[28] S. Libertino, J. L. Benton, D. C. Jacobson, D. J. Eaglesham, J. M. Poate, S. Coffa, P. Kringhøj, P. G. Fuochi and M. Lavalle, Applied Physics Letters 71 (1997) 389.

[29] A. R. Peaker, J. H. Evans-Freeman, P. Y. Y. Kan, I. D. Hawkins, J. Terry, C. Jeynes and L. Rubaldo, Materials Science and Engineering B 71 (2000) 143.

[30] P. Pellegrino, P. Lévêque, J. Wong-Leung, C. Jagadish and B. G. Svensson, Applied Physics Letters 78 (2001) 3442.

[31] B. G. Svensson, C. Jagadish and J. S. Williams, Nuclear Instruments and Methods in Physics Research B 80/81 (1993) 583.

[32] C. Jagadish, B. G. Svensson and N. Hauser, Semiconductor Science and Technology 8 (1993) 481.

[33] V. P. Markevich, O. Andersen, I. F. Medvedeva, J. H. Evans-Freeman, I. D. Hawkins, L. I. Murin, L. Dobaczewski and A. R. Peaker, Physica B 308-310 (2001) 513.

[34] P. Lévêque, P. Pellegrino, A. Hallén, B. G. Svensson and V. Privitera, Nuclear Instruments and Methods in Physics Research B 174 (2001) 297.

[35] K. B. Nielsen, L. Dobaczewski, K. Goscinski, R. Bendesen, O. Andersen and B.B. Nielsen, Physica B 273-274 (1999) 167.

[36] A. R. Peaker, J. H. Evans-Freeman, P. Y. Y. Kan, L. Rubaldo, I. D. Hawkins, K.D. Vernon-Parry and L. Dobaczewski, Physica B 273-274 (1999) 243.

[37] P. Y. Y. Kan, K. F. A. El-Rahman, N. Abdelgader, J. H. Evans-Freeman and A.R. Peaker, Materials Science and Engineering B 81 (2001) 77.

[38] B. B. Nielsen, L. Hoffmann and M. Budde, Materials Science and Engineering B 36 (1996) 259.

[39] M. Bosetti, N. Croitoru, C. Furetta, C. Leroy, S. Pensotti, P. G. Rancoita, M. Rattaggi, M. Redaelli, M. Rizzatti and A. Seidman, Nuclear Instruments and Methods in Physics Research A 361 (1995) 461.

[40] B. G. Svensson, C. Jagadish, A. Hallén and J. Lalita, Nuclear Instruments and Methods in Physics Research B 106 (1995) 183.

[41] B. G. Svensson, C. Jagadish, A. Hallén and J. Lalita, Physical Review B 55 (1997) 10498.

[42] J. H. Evans-Freeman, N. Abdelgader, P. Y. Y. Kan and A. R. Peaker, Nuclear Instruments and Methods in Physics Research B 186 (2002) 41.

[43] M. A. Gad and J. H. Evans-Freeman, Nuclear Instruments and Methods in Physics Research B 253 (2006) 85.

[44] J. L. Benton, J. Michel, L. C. Kimerling, D. C. Jacobson, Y.-H. Xie, D. J. Eaglesham, E. A. Fitzgerald and J. M. Poate, Journal of Applied Physics 70 (1991) 2667.

[45] J. L. Benton, K. Halliburton, S. Libertino, D. J. Eaglesham and S.Coffa, Journal of Applied Physics 84 (1998) 4749.

[46] P. Deixler, J. Terry, I. D. Hawkins, J. H. Evans-Freeman, A. R. Peaker, L. Rubaldo, D. K. Maude, J.-C. Portal, L. Dobaczewski, K. B. Nielsen, A. N. Larsen and A. Mesli, Applied Physics Letters 73 (1998) 3126.

[47] L. Dobaczewski, A. R. Peaker and K. B. Nielsen, Journal of Applied Physics 96 (2004) 4689.

[48] I. Kovačević, V. Borjanović and B. Pivac, Vacuum 71 (2003) 129.

[49] S. Libertino, S. Coffa and J. L. Benton, Physical Review B 63 (2001) 195206.

[50] S. Fatima, B. G. Svensson and C. Jagadish, IEEE (1997) 154.

[51] F. D. Auret, A. R. Peaker, V. P. Markevich, L. Dobaczewski and R. M. Gwilliam, Physica B 376-377 (2006) 73.

[52] A. N. Larsen, A. Mesli, K. B. Nielsen, H. K. Nielsen, L. Dobaczewski, J. Adey,R. Jones, D. W. Palmer, P. R. Briddon and S. Oberg, Physical Review Letters 97 (2006) 106402.

[53] A. E. Michel, Nuclear Instruments and Methods in Physics Research B 37/38 (1989) 379.

[54] P. A. Stolk, H.-J. Gossmann, D. J. Eaglesham, D. C. Jacobson, C. S. Rafferty, G.

H. Gilmer, M. Jaraíz, J. M. Poate, H. S. Luftman and T. E. Haynes, Journal of Applied Physics 81 (1997) 6031.

[55] S. M. Davidson and G. R. Booker, Radiation Effects and Defects in Solids 6 (1970) 33.

[56] N. E. B. Cowern, K. T. F. Janssen and H. F. F. Jos, Journal of Applied Physics 68 (1990) 6191.

[57] J. Kim, J. W. Wilkins, F. S. Khan and A. Canning, Physical Review B 55 (1997)16186.

[58] D. J. Eaglesham, P. A. Stolk, H.-J. Gossmann and J. M. Poate, Applied Physics Letters 65 (1994) 2305.

[59] I. G. Salisbury and M. H. Loretto, Philos. Mag. A 39 (1979) 317.

[60] H. A. W. E. Mubarek and P. Ashburn, Applied Physics Letters 83 (2003) 4134.

[61] H. A. W. E. Mubarek, Y. Wang, R. Price, J. M. Bonar, J. Zhang, P. L. F. Hemment and P. Ashburn, Materials Science in Semiconductor Processing 8 (2005) 103.

[62] H. A. W. E. Mubarek, J. M. Bonar, G. D. Dilliway, P. Ashburn, M. Karunaratne, A. F. Willoughby, Y. Wang, P. L. F. Hemment, R. Price, J. Zhang and P. Ward, Journal of Applied Physics 96 (2004) 4114.

[63] B. L. Yang, H. Wong, P. G. Han and M. C. Poon, Microelectronics Reliability 40 (2000) 277.

[64] G. Y. Jeon, J. S. Kim, C. N. Whang, S. Im, J.-H. Song, J. H. Song, W. K. Choi and H. K. Kim, Nuclear Instruments and Methods in Physics Research B 206 (2003) 409.

[65] D. Girginoudi, N. Georgoulas, A. Thanailakis and E. K. Polychroniadis, Materials Science and Engineering B 114 (2004) 381.

[66] W.-K. Chu, L. Shao, J. Liu, P. E. Thompson, X. Wang and H. Chen, IEEE (2002) 48.

[67] F. Cristiano, N. Cherkashin, P. Calvo, Y. Lamrani, X. Hebras, A. Claverie, W.Lerch and S. Paul, Materials Science and Engineering B 114-115 (2004) 174.

[68] V. Privitera, Current Opinion in Solid State and Materials Science 6 (2002) 55.

# **Chapter 3: Diamond properties and defects**

## 3.1 Introduction