Organic/inorganic hybrid solar cells based on electroplated CdTe.

MANAF, Nor Azlian Binti Abdul.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/20010/

#### A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/20010/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

Adsetts Centre, City Campus

Sheffield S1 1WD

102 153 135 9

Sheffield Hallam University Learning and Information Services Adsetts Centre, City Campus Sheffield S1 1WD

### REFERENCE

ProQuest Number: 10697317

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10697317

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

# ORGANIC/INORGANIC HYBRID SOLAR CELLS BASED ON ELECTROPLATED CDTE

MANAF. N.A.A.

Ph.D.

## Organic/Inorganic Hybrid Solar Cells Based on Electroplated CdTe

Nor Azlian Binti Abdul Manaf

A thesis submitted in partial fulfilment of the requirements of Sheffield Hallam University for the degree of **Doctor of Philosophy**

November 2015

#### **Declaration**

I hereby declare that the work described in this thesis is my own work, done by me and has not been submitted for any other degree anywhere.

#### **Abstract**

Name: Nor Azlian Binti Abdul Manaf

Supervisor: Professor I. M. Dharmadasa

Second supervisor: Dr. Aseel Hassan

Department/ Faculty: Materials and Engineering Research Institute (MERI), Faculty of

Arts, Computing, Engineering and Sciences (ACES)

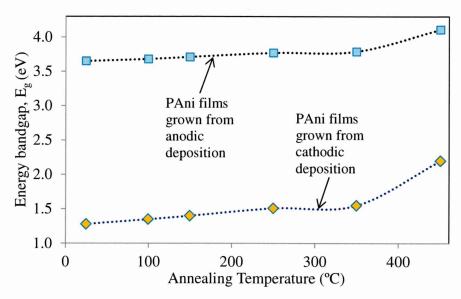

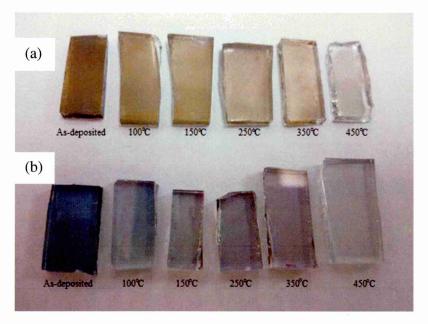

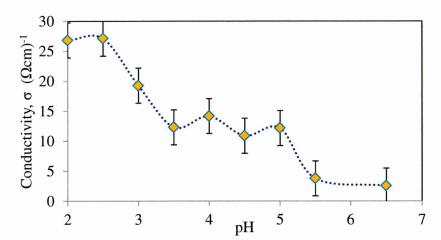

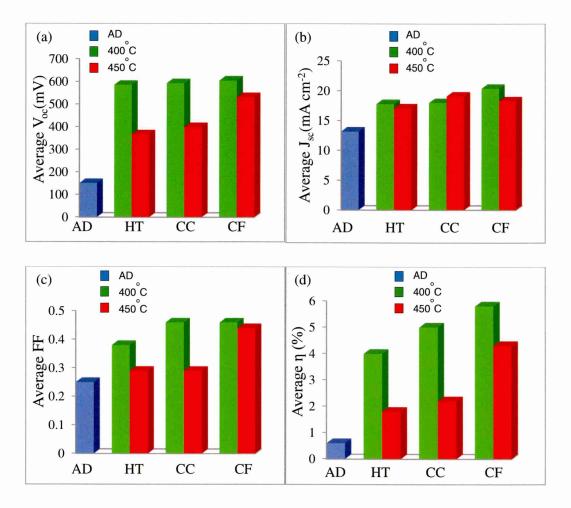

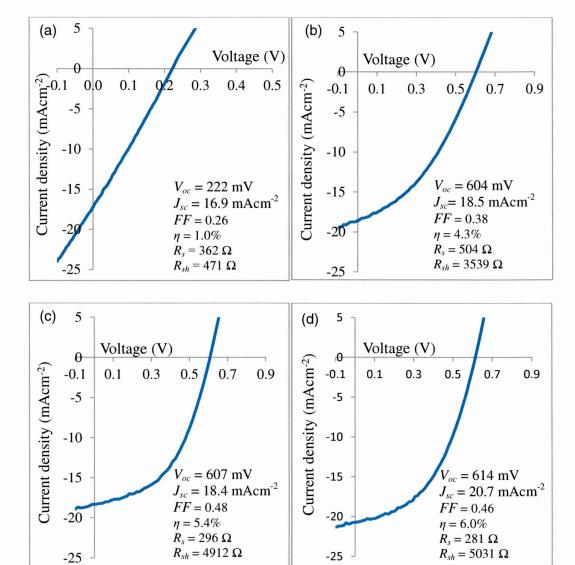

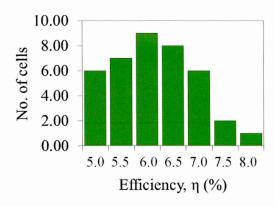

The purpose of this work is to develop organic/inorganic hybrid solar cells based on electroplated CdTe. The materials used in this research are CdS, CdTe and PAni. These materials have been characterised by XRD, Raman spectroscopy, EDX, SEM, AFM, UV-Vis spectroscopy, PEC, C-V and DC measurements, UPS and PL for their structural, compositional, morphological, optical, electrical and defect properties. CdS has electrodeposited from the electrolyte using (NH<sub>4</sub>)<sub>2</sub>S<sub>2</sub>O<sub>3</sub> as the sulphur source. The optimum growth voltage  $(V_g)$  and temperature  $(T_g)$  are obtained at 1455 mV and 85°C, respectively. The best annealing condition is found to be at 400°C for 20 minutes in the presence of CdCl<sub>2</sub>+CdF<sub>2</sub>. CdTe thin films were electrodeposited from CdCl<sub>2</sub> precursor and a comprehensive study was carried out for the first time. The work has demonstrated a better understanding of material issues and some clues on the effect of  $CdCl_2$  treatment. The optimum  $V_g$  and annealing condition were obtained at 698 mV with respect to the calomel electrode and 420°C for 20 minutes in the presence of CdCl<sub>2</sub>+CdF<sub>2</sub> or CdCl<sub>2</sub>+CdF<sub>2</sub>+GaCl<sub>3</sub>. The development of PAni thin films has been established using anodic and cathodic deposition. The pernigraniline salt PAni grown from anodic has an amorphous structure, large bandgap and cementing growth effect while leucoemeraldine salt PAni grown from cathodic deposition shows the best crystallinity at  $V_g$ =1654 mV with respect to carbon anode, smaller grain size, higher resistivity and lower bandgap. The CdS, CdTe and PAni thin films have been studied in device structures, assessing their solar cell device performance. The best of CdS/CdTe solar cell was observed with efficiency of 5.8% when using CdS thin film treated with CdCl<sub>2</sub>+CdF<sub>2</sub> at 400°C. The best solar cell from CdTe study shows the efficiency of 6.8% when using CdTe thin films treated with CdCl<sub>2</sub>+CdF<sub>2</sub> at 420°C. Further study demonstrates that a device with g/FTO/n-CdS(~200 nm)/n-CdTe(~1200 nm)/p-CdTe( $\sim$ 300 nm)/Au shows high  $J_{sc}$  and highest efficiency (7.7%) due to the formation of n-n heterojunction, p-n homojuction and ohmic contact within the structure. The efficiency of the solar cell increased from ~2.4% to ~4.2% when incorporating ~81 nm thick PAni layer grown from anodic deposition. The devices incorporating ZnS, ZnTe and CdSe layers show the prospect of graded bandgap solar cell, but proper optimisation on each material should be carried out before using in multi-layer device structures. The study on the lifetime of solar cells show slow degradation and it maintained more than 83% of its initial efficiency after 9,000 hours.

#### Acknowledgements

#### Bismillahirrahmannirrahim.

First and foremost I would like to thank my supervisor, Professor I. M. Dharmadasa. It has been a pleasure to work under his supervision for the past 3 years and 6 months. His enthusiasm and dedication has truly been an inspiration. I would also like to thank my second supervisor, Dr. Aseel Hassan, my colleagues, the PhD students (past and present) of the SHU Solar Energy group as well as lecturers and friends outside of the group.

Various research collaborators should be acknowledged such as Professor T. Druffel, R. Dharmadasa and their research group from University of Louisville, USA for their efforts to perform UPS and PL measurements. Thank you to Mr. L. Bowen from Durham University to perform many SEM measurements in the early research work, Professor M. Dergacheva from Institute of Organic Catalyst & Electrochemistry, Kazakhstan for the AFM measurements during the lab movement and Professor M. Walls and research group from CREST, Loughborough University for the knowledge sharing and discussion on the defects in CdTe thin films.

I would like to express my gratitude to Ministry of Education, Malaysia and National Defence University of Malaysia for the financial support.

Thank you to my supportive husband, Azraai Shamshuddin and my three little children, Aisyah Umairah, Alya Mysarra and Umar Rayyan. Although this journey is quite challenging, their understanding, patient and continuous support have motivated me to complete this PhD. I also would like to thank my parents, my parents in-law and my siblings for all their support during my degree, master and PhD. Last but not least, to whoever has support over the years and has allowed me to pursue my aspirations, I am immensely grateful, thank you.

#### **List of Publications**

#### Journal publications

- N. A. Abdul-Manaf, O.K. Echendu, F. Fauzi L. Bowen and I. M. Dharmadasa, Development of Polyaniline Using Electrochemical Technique for Plugging Pinholes in Cadmium Sulfide/Cadmium Telluride Solar Cells. *Journal of Electronic Materials*, 43:11 (2014) 4003–4010.

- N. A. Abdul-Manaf, R. Weerasinghe, O.K. Echendu and I. M. Dharmadasa, Electro-plating and characterisation of Cadmium Sulphide thin films using Ammonium Thiosulphate as the sulphur source, *Journal of Materials Science:* Materials in Electronics, 26: 4 (2015) 2418-2429.

- 3. N. A. Abdul-Manaf, H. I. Salim, M. L. Madugu, O. I. Olusola and I. M. Dharmadasa, Electro-plating and characterisation of CdTe thin films using CdCl<sub>2</sub> as the cadmium source, *Energies*, 8:10 (2015) 10883-10903.

- 4. I. M. Dharmadasa, O.K. Echendu, F. Fauzi, N. A. Abdul-Manaf and H.I. Salim, Effects of CdCl<sub>2</sub> treatment on deep levels in CdTe and their implications on thin film solar cells; A comprehensive photoluminescence study, *Journal of Materials Science: Materials in Electronic*, 26 (2015) 4571-4583.

- 5. O. I. Olusola, M. L. Madugu, N. A. Abdul-Manaf and I. M. Dharmadasa, Growth and characterisation of n- and p- type ZnTe thin films for applications in electronic devices, *Current Applied Physics*, 16 (2016) 120-130.

- I. M. Dharmadasa, O.K. Echendu, N. A. Abdul-Manaf, H. I. Salim, M. L. Madugu, O. I. Olusola and A. Ojo, Improvement of composition of CdTe thin films during heat treatment in the presence of CdCl2, (submitted to *Solar Energy Materials & Solar Cells* in September 2015, status: under review).

- 7. I. M. Dharmadasa, O. K. Echendu, F. Fauzi, H. I. Salim and N. A. Abdul-Manaf, Study of Fermi level movement during CdCl<sub>2</sub> treatment of CdTe thin films using ultra-violet photoemission spectroscopy, (submitted to Journal of Materials Science: Materials in Electronics in September 2015, status: under review).

#### **Conference proceedings**

- I. M. Dharmadasa, D. G. Diso, O. K. Echendu, H. I. Salim, N. A. Abdul-Manaf, M. B. Dergacheva, K. A. Mit and K. A. Urazov, Thin film photovoltaic solar cells with nano- and micro-rod type II-VI semiconducting materials grown by electroplating, *Proceedings of the 9th Photovoltaic Science, Applications and Technology Conference C95*, Swansea, United Kingdom, 10-12 April 2013, pp 79-82.

- N. A. Abdul-Manaf, O. K. Echendu, H. I. Salim, L. Bowen and I. M. Dharmadasa, Electrodeposition and characterization of polyaniline for development of organic/inorganic hybrid solar cells, *Solar Asia 2013*, CIUM, University of Malaya, Kuala Lumpur, Malaysia, 22-24 August 2013, pp. 105-110.

- 3. F. Fauzi, N. A. Abdul-Manaf, O. K. Echendu and I. M. Dharmadasa, Electrochemical deposition of organic and inorganic pin-hole plugging layers for CdS/CdTe solar cells, *Solar Asia 2013*, CIUM, University of Malaya, Kuala Lumpur, Malaysia, 22-24 August 2013, pp. 47-54.

- 4. I. M. Dharmadasa, O. K. Echendu, N. A. Abdul Manaf, M. B. Dergacheva, K. A. Mit and K. A. Urazov, Next generation solar cells using graded bandgap structures utilising nano- and micro- rod type semiconductors, *Solar Asia 2013*, CIUM, University of Malaya, Kuala Lumpur, Malaysia, 22-24 August 2013, pp. 17-22.

- 5. N. A. Abdul-Manaf, O. K. Echendu, F. Fauzi, L. Bowen and I. M. Dharmadasa, Electrodeposition and characterization of polyaniline to develop organic/inorganic hybrid solar cells based on cadmium telluride, *Proceedings of the 28th European Photovoltaic Solar Energy Conference and Exhibition*, Paris, France, 1-3 October 2013 pp. 2327 2332.

- N. A. Abdul-Manaf, H. I. Salim, M. L. Madugu and I. M. Dharmadasa, Electrodeposition of CdTe thin films using chloride precursor for the application in solar cells, *Photovoltaic Science Application and Technology Proceeding*, PVSAT 11, University of Leeds, Leeds, 15-17 April 2015, pp. 137-140.

- N. A. Abdul-Manaf and I. M. Dharmadasa, Fabrication of CdS, CdTe, and PAni Thin Films For Solar Cell Application Based on Electrodeposition Technique, *UK Semiconductors & UK Nitrides Consortium Summer Meeting*, 1-2 July, 2015, Sheffield, United Kingdom, pp. 132.

#### **Table of Contents**

| Declaration                                                        | i   |

|--------------------------------------------------------------------|-----|

| Abstract                                                           | ii  |

| Acknowledgements                                                   | iii |

| List of Publications                                               | iv  |

| Table of Contents                                                  | vi  |

| Chapter 1 - Introduction                                           | 1   |

| 1.1 Current issue on energy                                        | 1   |

| 1.2 Renewable energy                                               | 1   |

| 1.3 Solar energy                                                   | 4   |

| 1.3.1 Solar radiation                                              | 4   |

| 1.3.2 Photovoltaic technology                                      | 6   |

| 1.3.3 Brief history of solar cells                                 | 8   |

| 1.3.4 A range of next generation solar cells                       | 8   |

| 1.3.4.1 Hot carrier solar cells                                    | 9   |

| 1.3.4.2 Plasmonic solar cells                                      | 9   |

| 1.3.4.3 Organic solar cells                                        | 10  |

| 1.3.4.4 Quantum dot and nano solar cells                           | 11  |

| 1.3.4.5 Up conversion and down conversion for solar cells          | 11  |

| 1.3.4.6 Perovskite solar cell                                      | 12  |

| 1.4 CdS/CdTe thin film solar cell                                  | 13  |

| 1.5 Current issues in CdS/CdTe solar cell fabrication              | 15  |

| 1.6 Research objectives                                            | 16  |

| 1.7 Organisation of chapters                                       | 17  |

| References                                                         | 20  |

| Chapter 2 - Material properties and device physics of photovoltaic | 23  |

| 2.0 Introduction                                                   | 23  |

| 2.1 Solar energy materials                                         | 23  |

| 2.1.1 Intrinsic and extrinsic materials                            | 25  |

| 2.1.2 Structure of materials                                       | 26  |

| 2.1.3 Polymer                                                      | 29  |

| 2.1.4 Materials used in this work                                  | 32  |

| 2.1.4.1 Cadmium Sulphide                                           | 32  |

| 2.1.4.2 Cadmium Telluride                                          | 33  |

| 2.1.4.3 Polyaniline                                                | 34  |

| 2.2 Junctions and interfaces in solar cell devices                 | 35  |

|     | 2.2.1 Homojunction and heterojunction                                    | 36 |

|-----|--------------------------------------------------------------------------|----|

|     | 2.2.2 p-n and p-i-n junctions                                            | 37 |

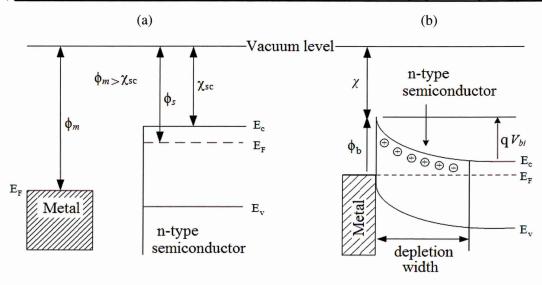

|     | 2.2.3 Metal-Semiconductor interfaces: Schottky diodes and Ohmic contacts | 39 |

|     | 2.2.4 Metal-Insulator-Semiconductor junctions                            | 42 |

|     | 2.3 Thin film deposition                                                 | 43 |

|     | 2.3.1 Various deposition techniques in thin film solar cells             | 44 |

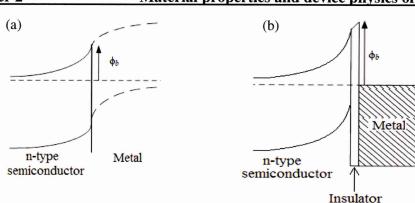

|     | 2.3.2 Electrodeposition                                                  | 46 |

| Ref | ferences                                                                 | 49 |

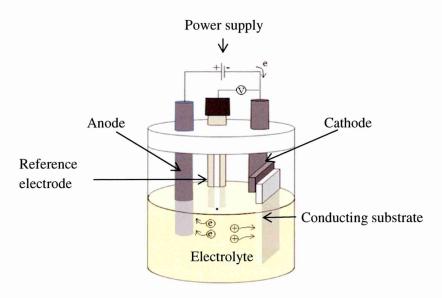

| Ch  | apter 3 - Experimental methods                                           | 54 |

|     | 3.0 Introduction                                                         | 54 |

|     | 3.1 Substrate preparation                                                | 55 |

|     | 3.1.1 The substrate: Cutting and cleaning procedure                      | 55 |

|     | 3.2 Electrochemical deposition (ED) of thin films                        | 55 |

|     | 3.2.1 Electrodeposition of cadmium sulphide (CdS)                        | 56 |

|     | 3.2.2 Electrodeposition of cadmium telluride (CdTe)                      | 57 |

|     | 3.2.3 Electrodeposition of polyaniline (PAni)                            | 58 |

|     | 3.2.4 Cyclic voltammogram                                                | 58 |

|     | 3.3 Thin films characterisation techniques                               | 59 |

|     | 3.3.1 Structural characterisation                                        | 59 |

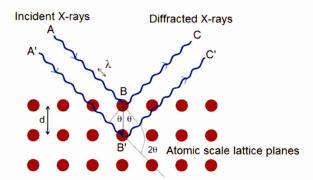

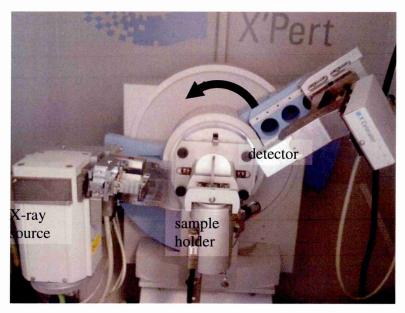

|     | 3.3.1.1 X-ray diffraction (XRD)                                          | 59 |

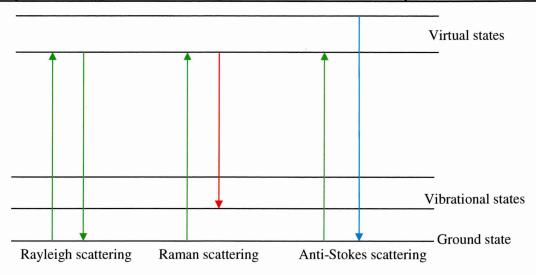

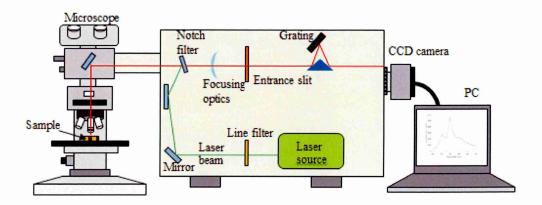

|     | 3.3.1.2 Raman spectroscopy                                               | 61 |

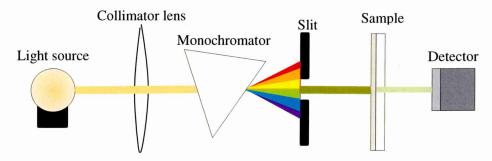

|     | 3.3.2 Optical characterisation                                           | 63 |

|     | 3.3.2.1 UV-Vis spectroscopy                                              | 64 |

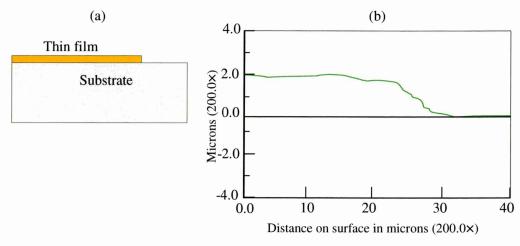

|     | 3.3.3 Thickness measurements                                             | 65 |

|     | 3.3.3.1 Optical profilometry                                             | 66 |

|     | 3.3.3.2 Faraday's law equation                                           | 67 |

|     | 3.3.4 Electrical characterisation                                        | 67 |

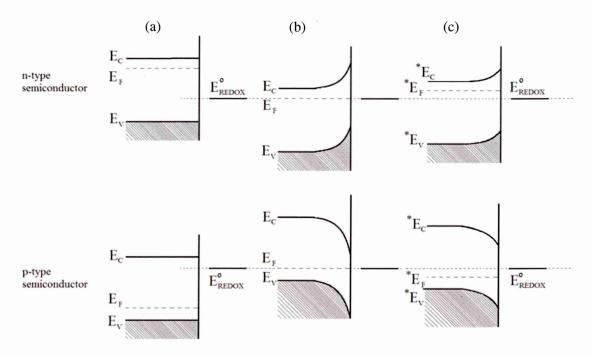

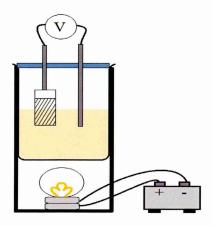

|     | 3.3.4.1 Photoelectrochemical (PEC) cell characterisation                 | 68 |

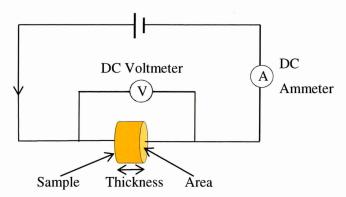

|     | 3.3.4.2 Direct current (DC) conductivity measurement                     | 70 |

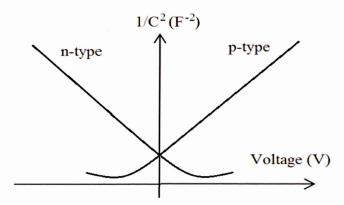

|     | 3.3.4.3 Capacitance-Voltage (C-V) measurement                            | 71 |

|     | 3.3.4.4 Ultra-violet photoemission spectroscopy (UPS)                    | 73 |

|     | 3.3.5 Morphological characterisation                                     | 74 |

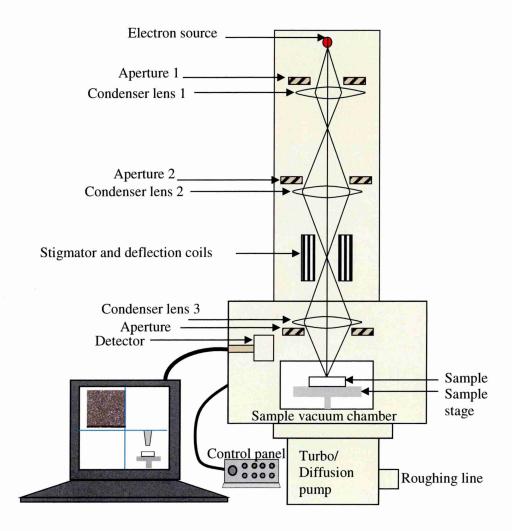

|     | 3.3.5.1 Scanning electron microscopy (SEM)                               | 74 |

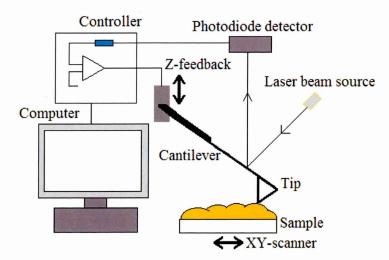

|     | 3.3.5.2 Atomic force microscopy (AFM)                                    | 76 |

|     | 3.3.6 Compositional characterisation                                     | 77 |

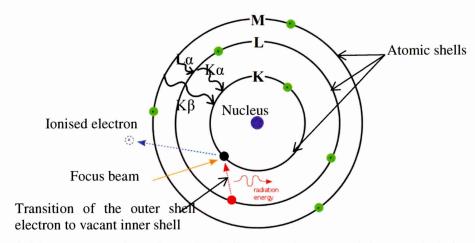

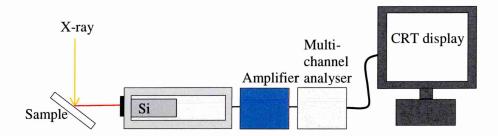

| 3.3.6.1 Energy dispersive X-ray (EDX) spectroscopy                                 | 77          |

|------------------------------------------------------------------------------------|-------------|

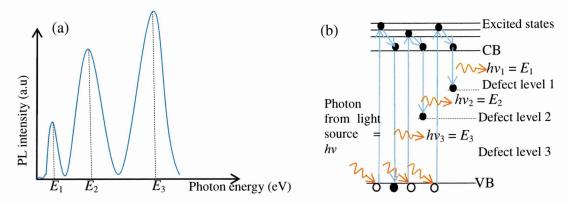

| 3.3.7 Defects characterisation                                                     | 79          |

| 3.3.7.1 Photoluminescence (PL)                                                     | 79          |

| 3.4 Fabrication and development of solar cell devices                              | 80          |

| 3.4.1 Fabrication of the glass/FTO/CdS/CdTe solar cells                            | 80          |

| 3.4.2 The etching process                                                          | 81          |

| 3.4.3 Back metal contact deposition                                                | 81          |

| 3.5 Characterisation of solar cell devices                                         | 82          |

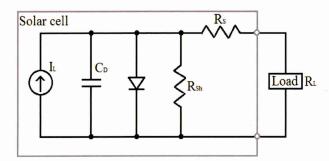

| 3.5.1 Current-Voltage (I-V) characterisation                                       | 82          |

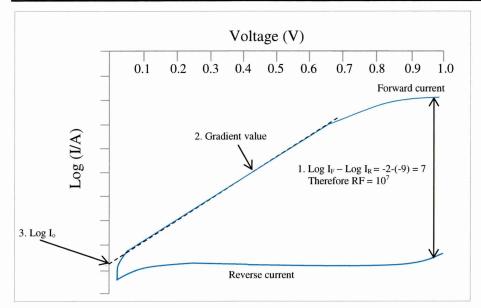

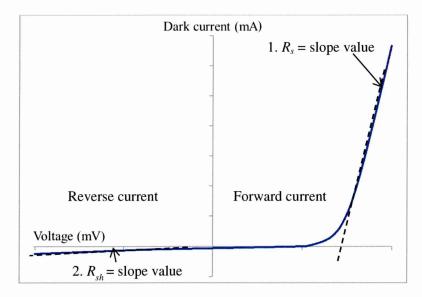

| 3.5.1.1 I-V characterisation under dark condition                                  | 83          |

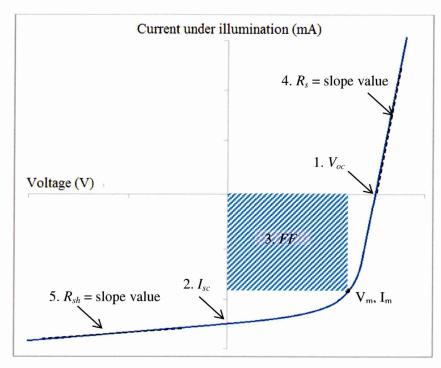

| 3.5.1.2 I-V characterisation under illumination                                    | 85          |

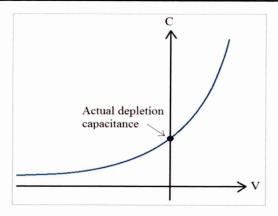

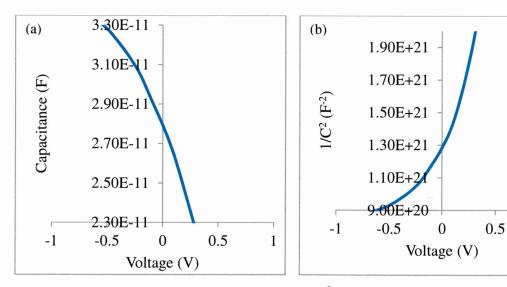

| 3.5.2 Capacitance-Voltage (C-V) characterisation                                   | 87          |

| 3.6 Overall conclusions                                                            | 89          |

| References                                                                         | 91          |

| Chapter 4 - Characterisation of CdS thin films                                     | 94          |

| 4.0 Introduction                                                                   | 94          |

| 4.1 Study the effect of growth voltage and temperature on the Cd electrodeposition |             |

| 4.1.1 Voltammogram                                                                 | 95          |

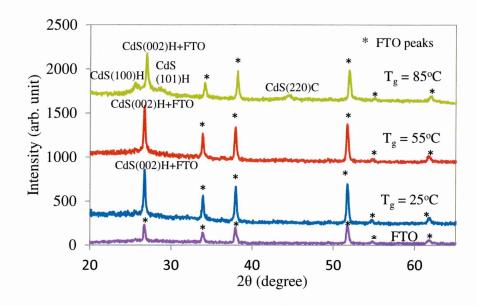

| 4.1.2 Structural characterisation                                                  | 97          |

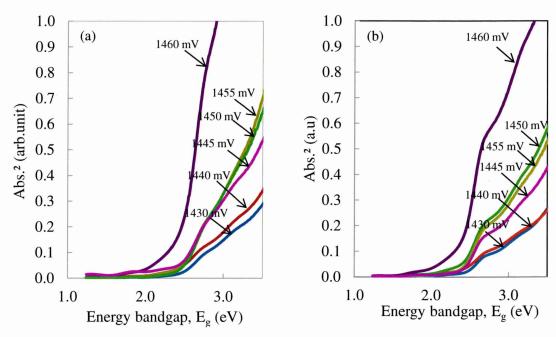

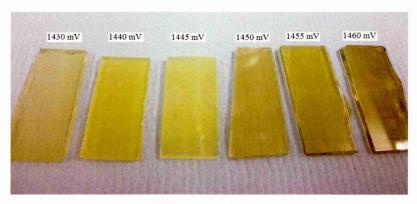

| 4.1.3 Optical characterisations                                                    | 100         |

| 4.1.4 Thickness measurements                                                       | 102         |

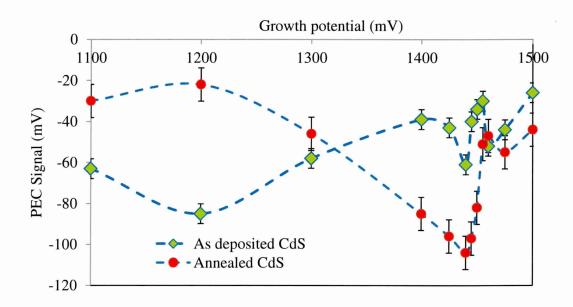

| 4.1.5 Electrical characterisation                                                  | 102         |

| 4.1.6 Morphological characterisation                                               | 103         |

| 4.1.7 Composition characterisation                                                 | 104         |

| 4.1.8 Conclusion                                                                   | 105         |

| 4.2 Study the effect of annealing temperature and time on CdS thi                  | n films 106 |

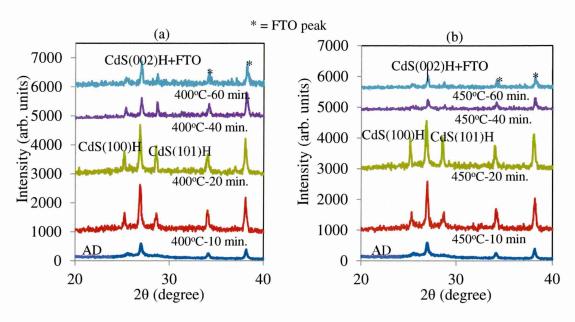

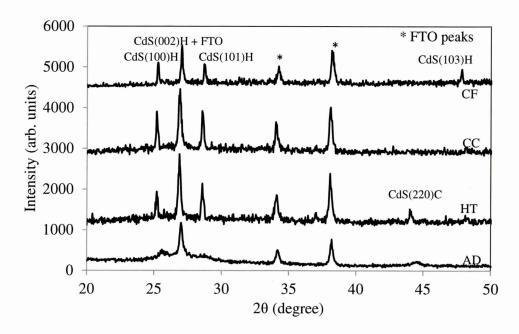

| 4.2.1 Structural characterisation                                                  | 106         |

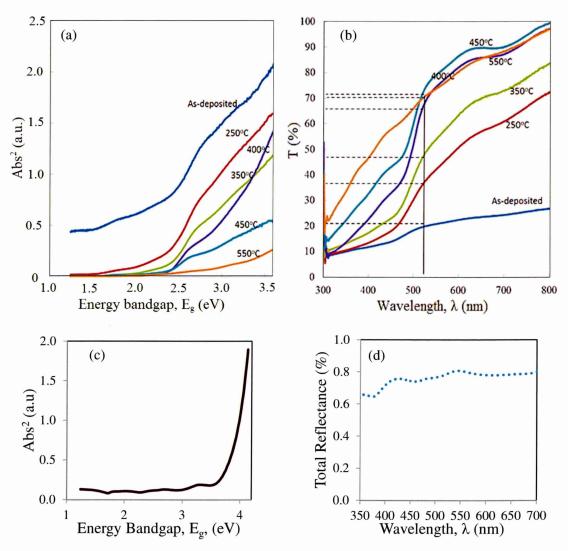

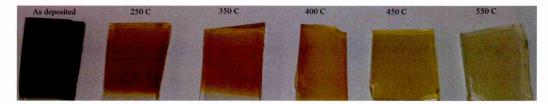

| 4.2.2 Optical characterisation                                                     | 108         |

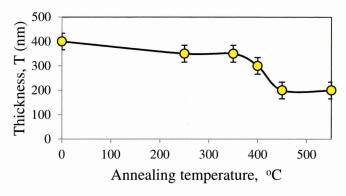

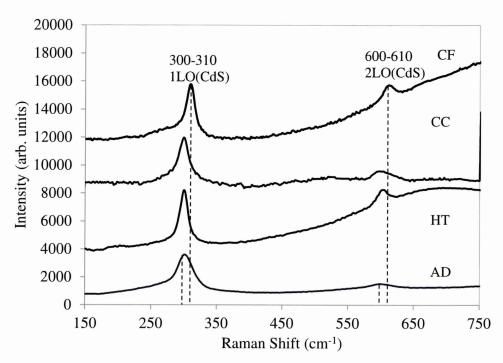

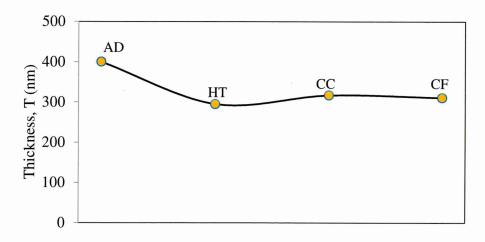

| 4.2.3 Thickness measurement                                                        | 110         |

| 4.2.4 Electrical characterisation                                                  | 111         |

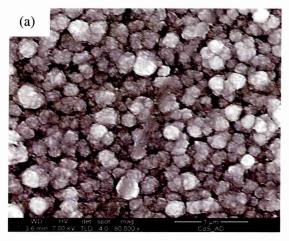

| 4.2.5 Morphological characterisation                                               | 113         |

| 4.2.6 Compositional characterisation                                               | 114         |

| 4.2.7 Conclusion                                                                   | 116         |

| 4.3 Study the effect of chemical treatments on CdS thin films                      | 117         |

| 4.3.1 Structural characterisation                                                  | 117         |

|      | 4.3.2 Thickness measurement                                                         | . 120 |

|------|-------------------------------------------------------------------------------------|-------|

|      | 4.3.3 Electrical characterisation                                                   | . 121 |

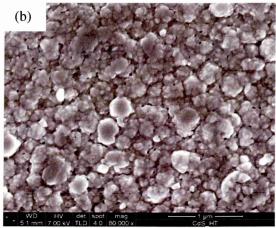

|      | 4.3.4 Morphological characterisation                                                | . 122 |

|      | 4.3.5 Conclusion                                                                    | . 123 |

|      | 4.4 Study the effect of sulphur concentrations in the CdS electrolyte               | . 124 |

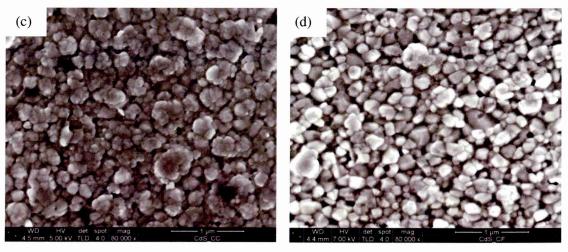

|      | 4.4.1 Structural characterisation                                                   | . 124 |

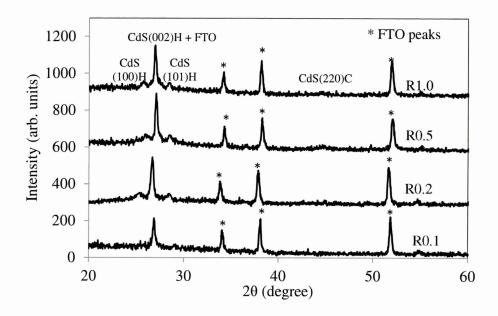

|      | 4.4.2 Optical characterisation                                                      | . 125 |

|      | 4.4.3 Thickness measurement                                                         | . 127 |

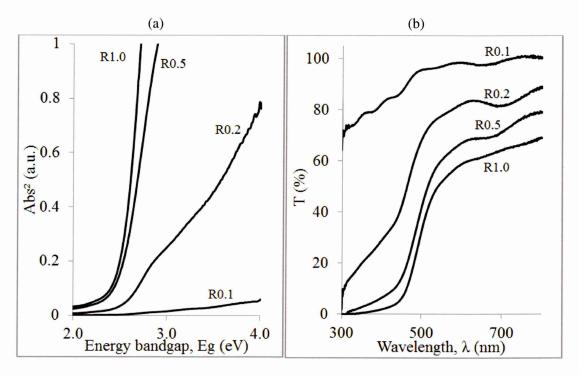

|      | 4.4.4 Morphological characterisation                                                | . 128 |

|      | 4.4.5 Conclusion                                                                    | . 129 |

|      | 4.5 Overall Conclusions                                                             | . 129 |

| Refe | rences                                                                              | . 130 |

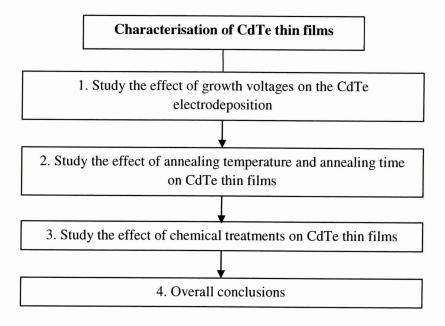

| Chap | oter 5 - Characterisation of CdTe thin films                                        | . 133 |

|      | 5.0 Introduction                                                                    | . 133 |

|      | 5.1 Study the effect of growth voltages on the CdTe electrodeposition               | . 133 |

|      | 5.1.1 Voltammogram                                                                  | . 134 |

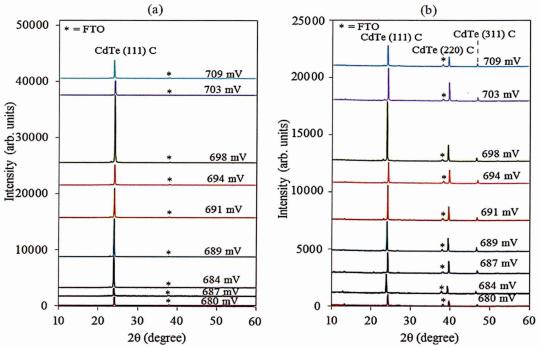

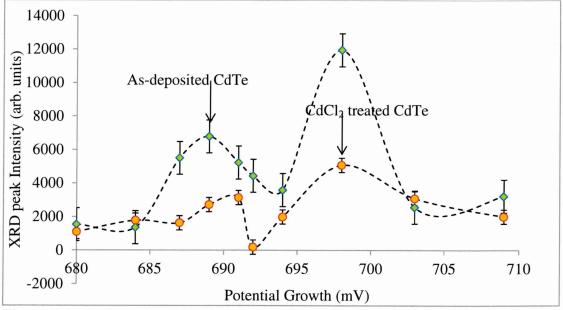

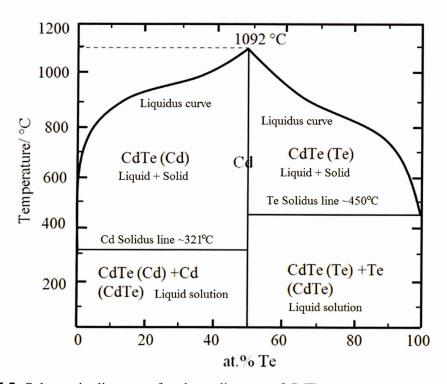

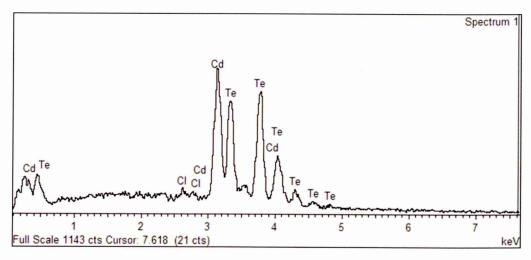

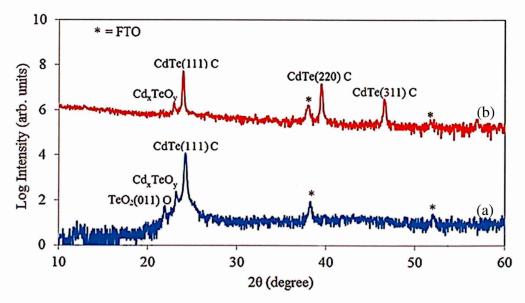

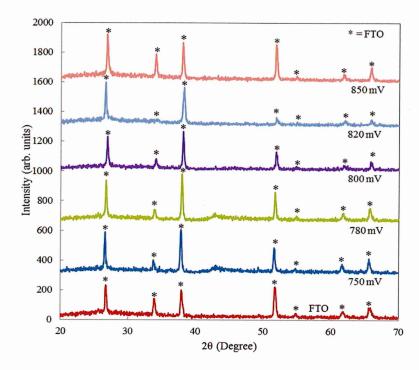

|      | 5.1.2 Structural characterisation                                                   | . 136 |

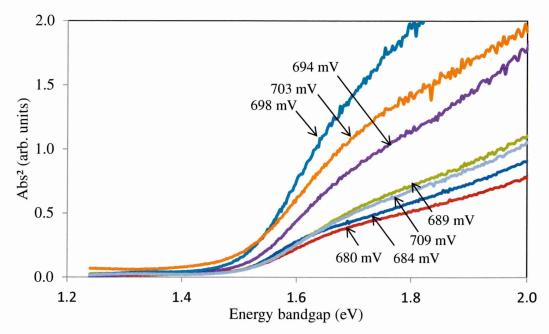

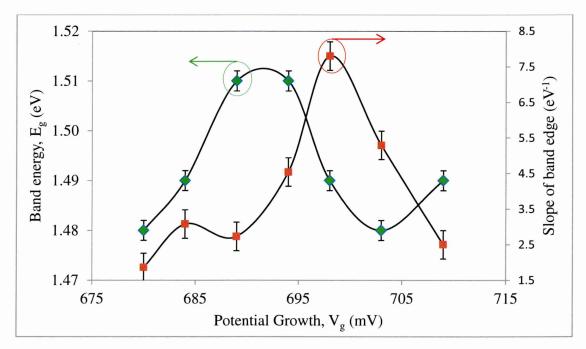

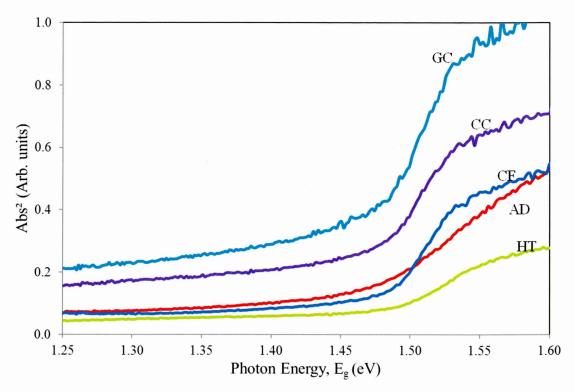

|      | 5.1.3 Optical characterisations                                                     | . 140 |

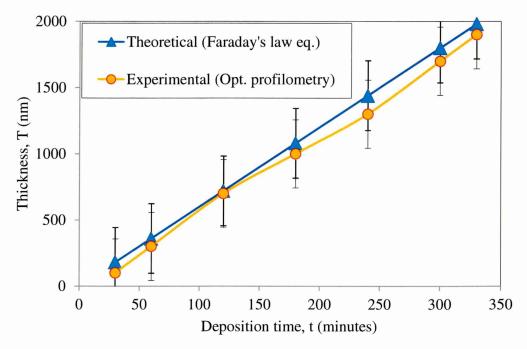

|      | 5.1.4 Thickness measurement                                                         | . 142 |

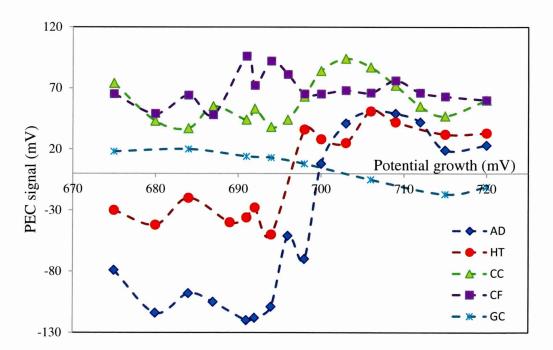

|      | 5.1.5 Electrical characterisation                                                   | . 143 |

|      | 5.1.6 Conclusion                                                                    | . 147 |

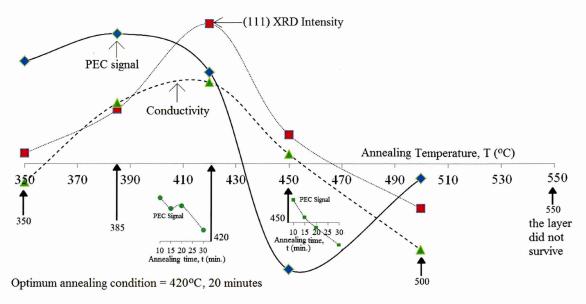

|      | 5.2 Study the effect of annealing temperature and annealing time on CdTe thin films | . 148 |

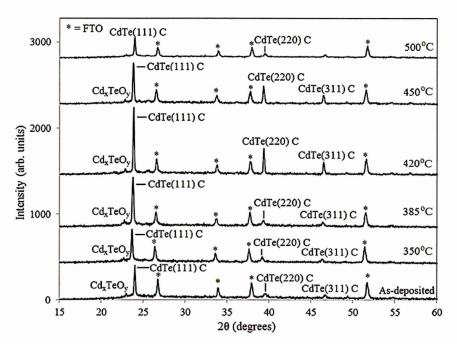

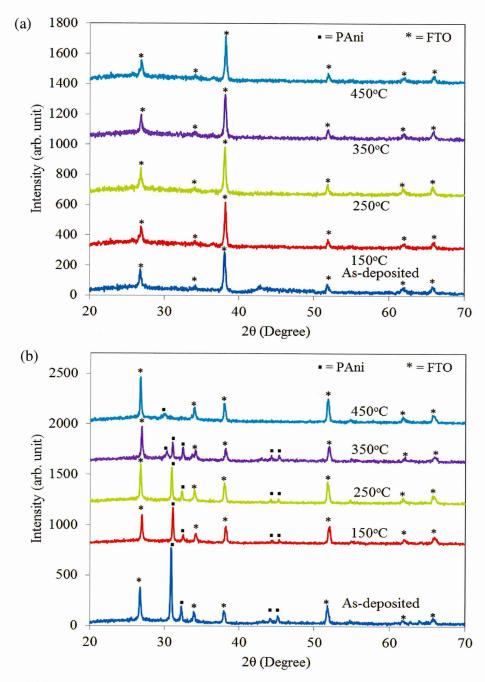

|      | 5.2.1 Structural characterisation                                                   | . 149 |

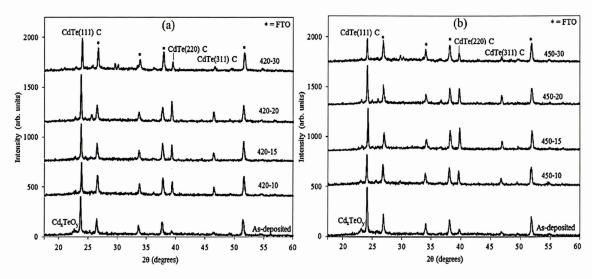

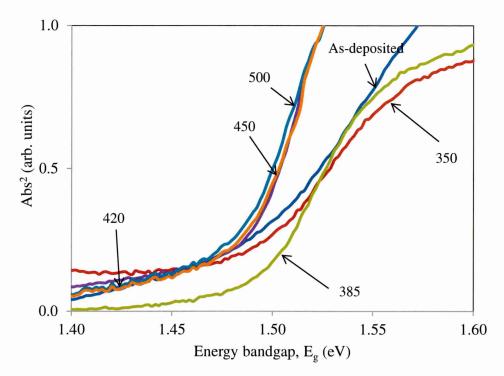

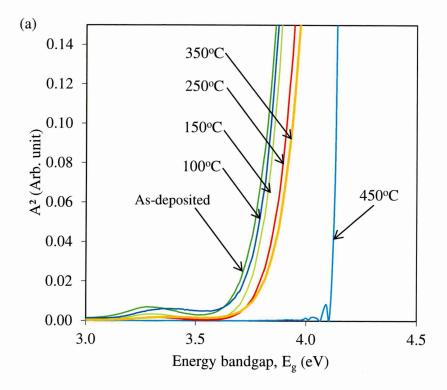

|      | 5.2.2 Optical characterisation                                                      | . 152 |

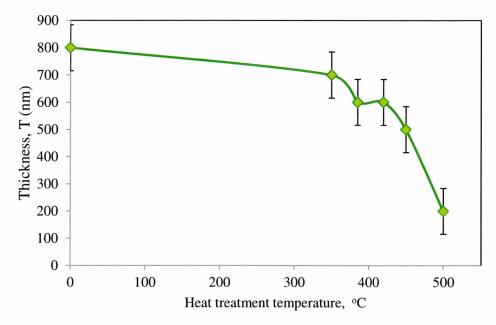

|      | 5.2.3 Thickness measurement                                                         | . 153 |

|      | 5.2.4 Electrical characterisation                                                   | . 154 |

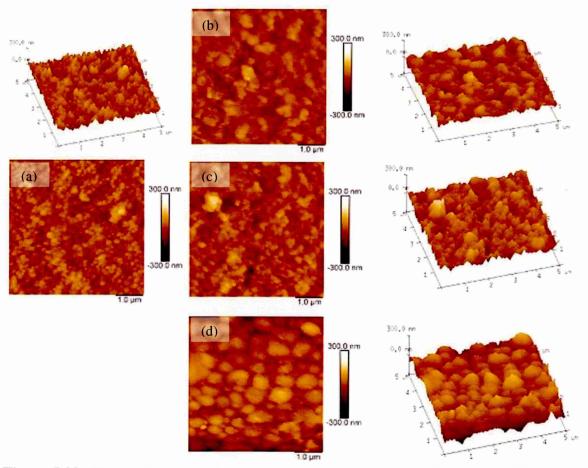

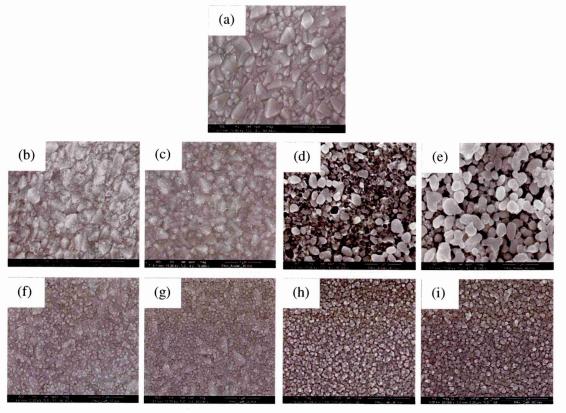

|      | 5.2.5 Morphological characterisation                                                | 158   |

|      | 5.2.6 Conclusion                                                                    | 162   |

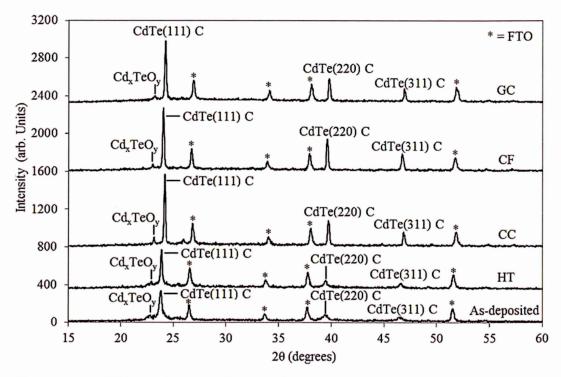

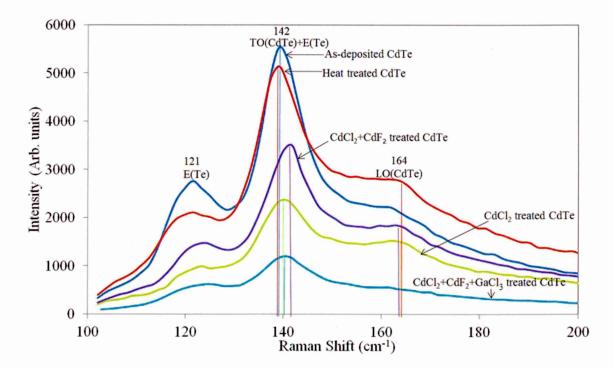

|      | 5.3 Study the effect of chemical treatments on CdTe thin films                      | 163   |

|      | 5.3.1 Structural characterisation                                                   | 164   |

|      | 5.3.2 Optical characterisation                                                      | 167   |

|      | 5.3.3 Electrical characterisation                                                   | 168   |

|      | 5.3.4 Morphological characterisation                                                | 174   |

|      | 5.3.5 Conclusion                                                                    | 176   |

|      | 5.4 Overall conclusions                                                             | 177   |

| References                                                                                     | 179 |

|------------------------------------------------------------------------------------------------|-----|

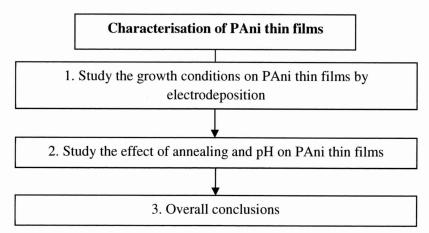

| Chapter 6 - Characterisation of PAni thin films                                                | 181 |

| 6.0 Introduction                                                                               | 181 |

| 6.1 Study the growth conditions of the PAni thin films by electrodeposition                    | 181 |

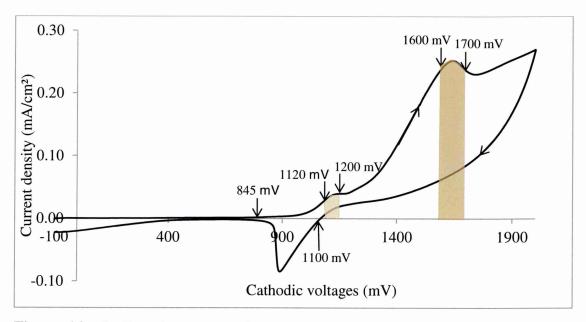

| 6.1.1 Voltammogram                                                                             | 182 |

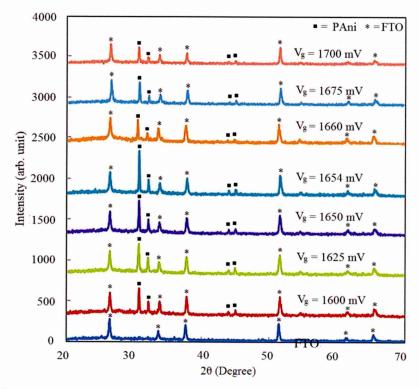

| 6.1.2 Structural characterisation                                                              | 184 |

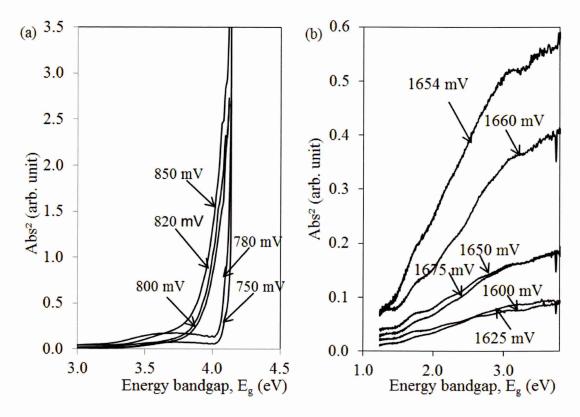

| 6.1.3 Optical characterisations                                                                | 186 |

| 6.1.4 Thickness measurement                                                                    | 188 |

| 6.1.5 Morphological characterisation                                                           | 190 |

| 6.1.6 Conclusion                                                                               | 192 |

| 6.2 Study the effect of annealing and pH on PAni thin films                                    | 193 |

| 6.2.1 Structural characterisation                                                              | 193 |

| 6.2.2 Optical characterisation                                                                 | 195 |

| 6.2.3 Electrical characterisation                                                              | 198 |

| 6.2.4 Morphological characterisation                                                           | 201 |

| 6.2.5 Conclusion                                                                               | 202 |

| 6.3 Overall Conclusions                                                                        | 202 |

| References                                                                                     | 204 |

| Chapter 7 - Characterisation of solar cells                                                    | 206 |

| 7.0 Introduction                                                                               | 206 |

| 7.1 Characterisation of CdS/CdTe solar cells                                                   | 207 |

| 7.1.1 The effect of CdS thin film conditions on CdS/CdTe solar cells.                          | 208 |

| 7.1.2 The effect of CdTe thin film conditions on CdS/CdTe solar cells                          | 213 |

| 7.1.2.1 Defect characterisation and study of Fermi-level movement                              | 221 |

| 7.1.3 The effect of p- or n-absorber layer (CdTe) on CdS/CdTe solar cells                      |     |

| 7.2 Incorporation of PAni thin films in CdS/CdTe solar cells                                   |     |

| 7.2.1 The effect of PAni thin films as buffer and pinhole plugging layers in solar cells       |     |

| 7.2.2 The effect of thickness of the PAni thin film as a pinhole plugging layer in solar cells |     |

| 7.3 Development of solar cell devices with other device structures                             |     |

| 7.3.1 Incorporation of ZnS and CdSe as buffer and/or window layers i                           | n   |

| 7.3.2 Incorporation of ZnTe as a capping layer in solar cells                                  |     |

| 7.4 The effect of etching conditions in device fabrication on device                           |     |

| performance                                                                                    | 242 |

| 7.5 Conclusions                                           | 246 |

|-----------------------------------------------------------|-----|

| References                                                | 249 |

| Chapter 8 - Conclusions and future work                   | 252 |

| 8.0 Intoduction                                           | 252 |

| 8.1 General conclusions                                   | 252 |

| 8.2 Challenges encountered in this work                   | 254 |

| 8.3 Suggestions for future work                           | 255 |

| 8.3.1 Monitoring the concentration of the electrolyte     | 255 |

| 8.3.2 Comparative study of PAni layers and lifetime issue | 256 |

| 8.3.3 Replace the glass/FTO with more suitable substrate  | 256 |

| 8.3.4 Graded bandgap solar cells                          | 256 |

| References                                                | 259 |

| Appendix                                                  | 260 |

#### **Chapter 1 - Introduction**

#### 1.1 Current issue on energy

Global demand for energy has risen inevitably in the last few decades, in line with industrial development and population growth. The various usages of energy became more important due to the technological inventions created by scientists. According to the International Energy Agency, (IEA) technological development in electronic utensils and appliances has increased the demand for residential energy over the past 10 years [1]. As the world today moves towards high-technology lifestyles and industrialisation, more energy resources are needed to cover people's needs.

Today, world energy consumption is highly dependent on fossil fuel-based sources, such as petroleum, natural gas and coal. They provide 84% of the primary energy used worldwide [2]. In spite of this, these sources have presented several drawbacks to the environment, human health and society in general. Petroleum is a carbon-based fuel and the combustion of petroleum produces carbon dioxide, which contributes to the greenhouse effect [3]. Coal provides around 28% of our energy. However, burning coal produces sulphur dioxide, an acidic gas that contributes to the formation of acid rain [2,4]. Although natural gas is cleaner than petroleum and coal, the huge quantity of methane is much more dangerous, since it can cause an enormous explosion due to any leakage of the gas. Fossil fuels are not renewable, since they cannot be replenished when they are used. It is estimated that the resources of petroleum and natural gas will run out within 50 and 30 years, respectively, while coal can endure for the next 90 years [2].

Therefore, it is vital for us to find an alternative renewable energy to ensure long-term security of energy supplies. Renewable energy is a natural form of energy that is much cleaner and sustainable, and has a low impact on the environment. Possible alternative renewable kinds of energy include hydropower, wind, biofuel, geothermal, wave and solar [5]. A brief discussion on this area follows in section 1.2.

#### 1.2 Renewable energy

The demand on renewable energy sources has become more crucial these days, due to environmental and economical sustainable issues. Renewable energy comes from resources such as water, wind, biomass, geothermal heat, ocean and sunlight that are

constantly replenished. It will not deplete our natural resources, is clean and has a very low impact on the environment or greenhouse effect.

Hydropower is power gained from the energy of falling or flowing water. The kinetic energy produced from the gravitational force or movement of water converts into mechanical energy through the spinning of turbines. The generator uses a magnetic field to convert this mechanical energy into electrical energy. Hydro-electric power stations can produce a great deal of power at a very low cost. It is much more reliable than other renewable energies, since electricity can be generated constantly. In fact, the water can be stored in the reservoir and ready to cope with peaks in demand. In spite of this, building a large reservoir is very expensive and will flood a very large area upstream, which causes problems for the residents and animals living there. Water quality of downstream can also be affected, which can have an impact on the health of the community and the environment [6].

Wind energy generated by the wind flows through a wind turbine that converts the kinetic energy into mechanical power [7]. This mechanical power can be used for specific tasks, such as grinding grain or pumping water. In the case of electricity, the generator is needed to convert the mechanical energy into electricity for various uses. Wind energy is a free, non-polluting and clean energy source. However, the cost of wind power technology requires a high initial investment for the machinery, site preparation and installation. In addition, some concern over the noise produced by the rotor blades and threat to the birds and bats turns out to be due to issues regarding this energy source. In fact, the major challenge of using wind as a source power is that it is intermittent. Although the generated electricity can be stored, not all winds can be harnessed to meet the timing of electricity demands.

Biofuel is an energy obtained from biomass materials through a process that converts carbon compounds into useful fuel. Biomass is a wide range of materials such as wood, agricultural residues, food and industrial waste. As there is a wide range of materials, the conversion technology of biomass into energy can be achieved by various methods, subject to the application. For example, the burning of biomass for direct usage, such as cooking, to produce heat and steam turbines has been extensively practised since ancient times. Moreover, the biomass is converted into liquid or gas, known as biodiesel, and this has been used widely for transportation [8]. In many ways, biodiesel works better than diesel, due to less polluting and the high quality of lubricating, which is good for engines. However, it has lower energy output than traditional fuels, and therefore requires greater quantities to be consumed, in order to

produce the same energy level. In fact, the requirement of large cropland to grow fuel crops could have an impact on the cost of food and could possibly lead to food shortages.

Geothermal is an energy obtained from the Earth, in particular from the hot rocks present inside the Earth. The energy is produced by the fission of radioactive materials in the Earth core and causes water deep inside the Earth to form steam. The steam becomes compressed at high pressure and comes out in the form of hot springs, which produces geothermal power [9]. Geothermal energy can be used directly, is non-polluting, does not generate by products, such as biofuels, and requires less maintenance cost. In fact, in ancient times, people used this source of energy for heating homes and other purposes. However, due to the small generation potential, there is no guarantee that the amount of energy produced will justify the capital expenditure and operation costs. Moreover, the safety issue regarding the poisonous gases and the eruption of volcano also becomes one of the disadvantages of this renewable energy source.

Wave energy is the energy generated from the interminable march of waves of the oceans. The kinetic energy formed by the continuous oscillating water is converted to the mechanical energy through the turbine rotation. Then, a generator converts this mechanical energy into useful electricity. Also, tidal energy is a hydropower that converts the energy of the tides into electricity. The tides are created by the gravitational effect of the sun and the moon on the earth due to the orbital characteristics of the Earth-Moon system and bring about cyclical movement of the seas. Both wave and tidal energies have unlimited supply. They can produce significant amount of energies with low running costs and no waste products. Nevertheless, these renewable energies are suitable only for certain locations. The wave energy has low performances in rough weather. Moreover, both of these energies also create hazards for some of the creatures near it. Large machines have to be placed nearby and in the water to gather energy from the waves and tides. These machines disturb the seafloor, change the habitat of near-shore populations and create noise that disturbs the sea life around them.

Solar energy is produced from the radiant energy emitted by the Sun. There are two types of solar energy; solar thermal and solar photovoltaic (PV). Solar thermal absorbs energy from sunlight to a heat receiver, which transforms energy from heat into solar thermal electricity for hot water heating and a variety of purposes. Solar PV panels convert the solar energy into electricity directly through photovoltaic conversion, using a PV cell [10]. Solar energy makes absolutely no noise at all, is clean, non-polluting and will last forever. It is reliable because electricity is actively created in just a few

millimetres thickness. Additionally, it requires only a low cost of maintenance, since there are no moving parts such as turbines in a solar panel, and this makes it impossible to really damage them. Although solar panel installation requires an expensive initial cost, once a solar panel is installed, solar energy can be produced free of charge. In the long term, there can be a high return on investment due to the amount of free energy a solar panel can produce. The fact that solar energy can only be harnessed in daytime and in sunny conditions has become a disadvantage of this energy. However, the use of batteries can be exploited to charge the solar power to be used at any time.

In general, each source of renewable energy has unique benefits and cost, but the positive and negative effects of these energies should be considered before developing them to create power. After all, replacing fossil fuels with renewable energy has been found to reduce premature mortality and overall damage, including public health and global warming emissions. Among all, solar energy is the most diversified form of renewable energy. It is a long-lasting source of energy, which can be used almost anywhere, even where there is no national grid such as at remote site areas or in space.

#### 1.3 Solar energy

#### 1.3.1 Solar radiation

The Sun produces about 386 billion billion Megawatts (386 x  $10^{24}$  W) of energy by the nuclear fusion of hydrogen into helium in its core [11]. This energy is then radiated out from the core and moves across the solar system. The Earth then receives 174 petawatts (174 x  $10^{15}$  W) of solar energy at the upper atmosphere [12]. Some of this energy has been bounced off to space and about 89 petawatts has passed through the atmosphere and reached the Earth's surface. Worldwide energy consumption, reported by IEA was about ~15 terawatts (15 x  $10^{12}$  W) in 2012 [12]. This figure is only 1/5900 of the total energy received from the sun. Therefore, the main challenge facing us is to capture that energy. A lot of study and research should be done to harness the Sun, and transform its energy to meet our needs.

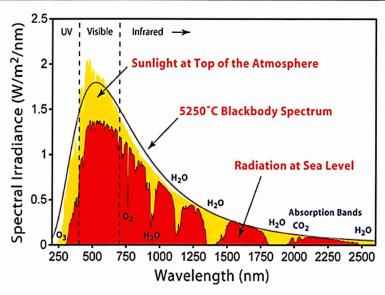

The Sun radiates light across a broad range of the electromagnetic spectrum from the ultraviolet, (UV) through the visible to the far infrared, (IR). Thus, the solar spectrum can be divided into three main regions as shown in Figure 1.1. UV in the wavelength range from 100 to 400 nm contains ~5% of irradiance, visible light with the wavelength range from 400 to 700 nm containing ~43% of the irradiance and IR with the wavelength range from 700 nm to ~1 mm, consisting of almost ~52% of irradiance.

**Figure 1.1:** The shape of the solar spectrum at different condition.

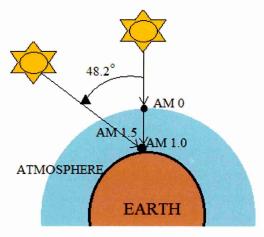

The intensity and the spectral distribution of the radiation received on the Earth's surface are subject to the optical path length between the Earth and the Sun, the angle of incident radiation and the atmospheric conditions. The path length through the atmosphere is characterised by the term air-mass (AM). It is defined as the thickness of the air layer around the Earth through which sunlight passes. The spectrum, as detected from a satellite at outer space, is referred to as AM0, where there is no absorption of the radiation. The power density of AM0 is about 1360 Wm<sup>-2</sup>. The solar spectrum that has travelled through the atmosphere with normal incidence above the point on the Earth is AM1. AM1 can be used for characterising solar cells in tropical region of the Earth. AM 1.5 is the air mass when the sun is at an angle of 48.2° above the horizon. It is used in a mid-lattitudes and adopted by the global solar energy industry as a standard for the solar cells characterisation. The power density of AM1.5 is 1000 Wm<sup>-2</sup> [13]. The path length of sunlight through the atmosphere down to the Earth's surface is shown in Figure 1.2 [13].

$$AM = \frac{1}{\cos \theta_z} = \sec \theta_z \tag{1.1}$$

where  $\theta_z$  is the angle made between the Sun and the zenith.

Figure 1.2: Path length of the Sun's illumination through the atmosphere.

Several conditions within the atmosphere can have an adverse effect on the intensity of solar radiation. The atmosphere contains 78% nitrogen, 21% oxygen, 0.9% argon, and 0.03% carbon dioxide with very small percentages of other elements. Our atmosphere also contains water vapour and traces of dust particles, pollen, plant grains and other solid particles. Apart from that, latitude, terrain, season, weather and clouds can also affect the amount of radiation that reaches the surface at any given location.

As mentioned in the previous section, there are two techniques to harvest solar radiance. These are solar thermal and solar PV. Solar thermal technology absorbs solar radiance from the Sun, using appropriate equipment, and converts into heat or electrical energy through solar thermal conversion, while solar PV converts light energy (photons) into electricity through the PV cell. In this conversion, specific materials, typically semiconductor materials are used to absorb the photons and release electrons. The free electrons are collected through the external circuit and then produce electricity. Further explanations on PV conversion are given in section 1.3.2.

#### 1.3.2 Photovoltaic technology

PV technology is a method of generating electricity by converting solar radiation into direct current electricity through a semiconductor device, known as a solar cell, that exhibits the PV effect.

PV conversion requires three principal processes starting from the absorption of photons, which creates electron-hole pairs, separation of these photo-generated charge carriers pair of opposite types (free electron and free hole), and, finally, extraction of these separated carriers to an external circuit [14,15].

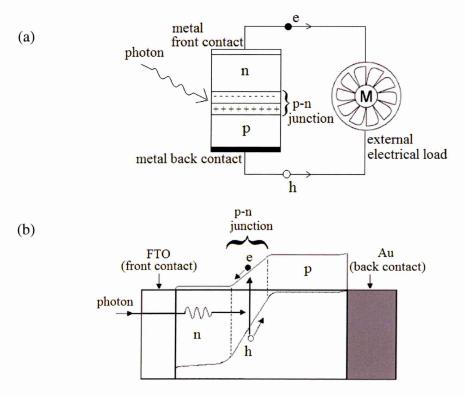

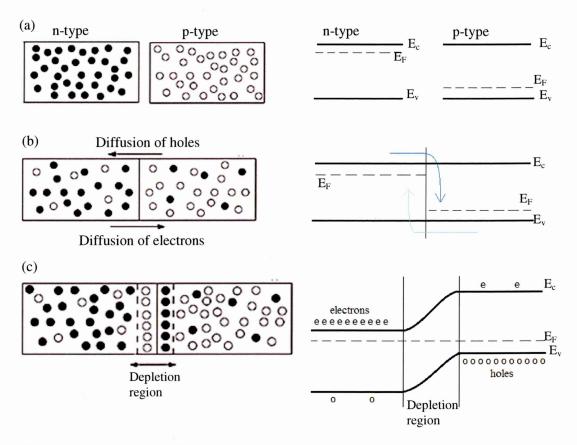

The energy supply for a solar cell is from photons, which comes from the Sun. These photons contain various amounts of energy corresponding to the different wavelengths of the solar spectrum. When photons strike the solar cell, some of them will be reflected, some will be absorbed, while others are transmitted. The absorbed photons generate electricity by transferring their energy to electrons in the bonded state (in the valence band). With its newfound energy, the electron leaves a hole behind and excites to a higher energy state corresponding to the energy of the incident photon. A variety of materials and processes can potentially satisfy the requirements for photovoltaic energy conversion, but in practice, nearly all photovoltaic energy conversion systems use semiconductor materials in the form of a p-n junction. Further explaination on p-n junction is discussed in Section 2.2.2. This p-n junction creates an internal electric field in solar cell devices and thus drives the holes to the p- side and electrons to the n- side. The electrons then dissipate their energy in the external circuit and return to the solar cell. The PV conversion in solar cell devices and the band diagram of the p-n junction can be seen in Figure 1.3.

**Figure 1.3:** Schematic of (a) PV conversion in p-n junction solar cell and (b) Energy band diagram of a p-n junction solar cell.

#### 1.3.3 Brief history of solar cells

A solar cell is an electronic device that converts the energy of light to electrical energy through the photovoltaic effect. Solar to electricity conversion was first invented by a French physicist, Edmond Becquerel in 1839. Becquerel was observing the photovoltaic effect while experimenting with a solid electrode in an electrolyte solution, when he saw voltage being generated when light fell upon the electrode. Several inventions were made afterwards, contributing to the evolution of solar energy use. In 1891, the first solar heater was created, and in 1893, the first solar cell was introduced. Solar power equipment started becoming popular and commercialised in the 1950s [16]. Now, it has been used to power space exploration equipment and the research and developments are in progress to establish solar power in transportation systems. At each phase of development, advanced large-scale solar energy plants are produced. In June 2015, the largest photovoltaic power plant was completed in Antelope Valley, Carlifonia and currently it is operating with 579 Megawatts [17].

Solar cells can be categorised into three generations, based on the order of their prominence. The first generation contains solar cells that are relatively expensive to produce. They are based on silicon (Si) or germanium (Ge) that are doped with phosphorus, P and boron, B to form p-n junctions. This generation is dominating the commercial solar cell market. Silicon cells have high efficiency, but particularly only pure silicon is needed, and due to the required complex process, the price is still high compared to the power output. Second generation solar cells are usually called thin-film solar cells, because they are made from layers of semiconductor materials only a few micrometres thick. The most common light absorbing materials used in thin film solar cells are cadmium telluride, (CdTe), copper indium gallium diselenide, (CIGS) and amorphous silicon, (a-Si). The biggest advantage of this technology is that it has a lower price than crystalline silicon solar cells, since it uses less material and lower cost manufacturing processes. This is the generation that we focus on in the following section of this research work. The third generation solar cells are being made from a variety of new materials, including nanotubes, quantum dots, silicon wires, solar inks using conventional printing press technologies, organic dyes, and conductive plastics. However, these solar cells need cutting edge technology and, currently, they produce low efficiency along with serious lifetime issues.

#### 1.3.4 A range of next generation solar cells

The ideas on next generation of solar cells have been proposed for the development of solar cell devices. The next generation of solar cells should be cheaper, more efficient

and much more environmentally friendlier than current versions. There could be future design improvements or a potential to exceed the Shockley-Queisser limit of power conversion for a single junction or multi-junction solar cells. Following sections highlight some of the next generation solar cells.

#### 1.3.4.1 Hot carrier solar cells

The main purpose of the hot carrier solar cell is to tackle the carrier thermalisation loss after the absorption of high energy photons with energy greater than the bandgap. In conventional solar cells, the photo-generated electrons usually lose their energy by cooling down from their initial energetic position to the band edges through optical phonon emission [18]. Hot carrier solar cells attempt to minimise this loss by extracting the generated carriers at higher energies. This process involves slowing the rate of carrier cooling in the absorber from picoseconds (ps) to nanoseconds (ns) and the extraction of energy selective carrier through energy selective contacts. In general, the three common approaches of hot carrier solar cells are such as by direct extraction of hot carriers through energy selective contacts, by application of an intermediate band assisted absorber and by using the multiple exciton generation. Hot carrier solar cells are an attractive alternative to the multilayer approach and offer simplicity of design with greater conversion efficiencies. The maximum achievable efficiency has been predicted to be 66%, but the practical realisation of actual hot carrier solar cells has never been successful [19]. The thermalisation in the absorber layer leading to insufficient collection of hot carrier at the electrical contact and the heat production in the environment could be harmful to the output of the solar cells [20, 21].

#### 1.3.4.2 Plasmonic solar cells

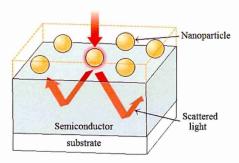

The plasmonic solar cell is among the third generation solar cells that convert light into electricity by improved light absorption using quantum of plasma oscillation known as plasmons. Plasmons are free-electron oscillations in a conductor that allow light to be manipulated at the nanoscale. The ability of plasmons is to guide and confine the light on sub-wavelength scales [22]. The designs for plasmonic solar cells vary depending on the method being used to trap and scatter light across the surface and through the material. The nanopartical cell is one of the common designs by deposit metal nanoparticles on the upper surface of the thin film semiconductor as shown in Figure 1.4 [23]. The basic principles for the functioning of plasmonic solar cells are such as scattering and absorption of light due to the deposition of metal nanoparticles. When

light hits these metal nanoparticles at their surface plasmon resonances, the light is scattered in many different directions. This allows light to travel along the semiconductor and bounce between the substrate and the nanoparticles, enabling the semiconductor to absorb more light. According to the proposers, the plasmonic solar cell is cheaper, more practical and the design offers a promising way to increase the efficiency of the solar cell. However, in addition to plasmonic effects, other effects such as doping effects of nanoparticles can have detrimental result for the solar cell. Practical devices with improved efficiencies are yet to come.

Figure 1.4: Example of a nanoparticle cell of the plasmonic solar cell.

#### 1.3.4.3 Organic solar cells

An organic solar cell is a type of solar cell that uses an organic compound, commonly a polymer, to absorb light and produces electricity through the photovoltaic effect [24, 25]. The conversion process is made by the combination of several types of materials, all having distinct optical and electrical properties. Although the photovoltaic concepts of the organic solar cell are quite similar to inorganic solar cells, certain mechanisms somehow differ from inorganic solar cells. For instance, the separation of electrons and holes in organic solar cells is caused by the electric field at the organic-metal interface created by the differences in electron affinity and ionisation potential between these two materials and the electric field is not associated with any band-bending, unlike in the inorganic solar cells. Organic solar cells can be formed in a single layer, bilayer, bulk heterojunction and graded heterojunction. The single layer organic solar cell is the simplest form. This cell is made by sandwiching a layer of organic electronic material between the two metallic conductors. The organic solar cell has low production costs in high volumes since the modification in molecular engineering and device architecture can be done by changing the chain length and functional group of polymers, which consequently forming variation of HUMO-LUMO gaps [24]. The optical absorption coefficient of organic molecules is high, so a large amount of light can be absorbed with

a small amount of materials. In spite of this, the major drawbacks associated with organic photovoltaic cells are the lifetime issue, low stability, low efficiency and low strength compared to inorganic photovoltaic cells.

#### 1.3.4.4 Quantum dot and nano solar cells

The quantum dot solar cell has secured its place as another promising next generation solar cells due to its operational feasibility, durability and ease of maintenance. This particular solar cell uses quantum dot as the absorbing material. As the bandgap in bulk material is fixed by the choice of the material, quantum dot can adjust its own bandgap by changing the size of the dots. This makes quantum dots attractive for multi-junction solar cells where a variety of materials are used to improve efficiency by harvesting multiple portions of the solar spectrum [26].

Another promising solar cell is the type with the attachment of semiconductor nanostructures such as nano-wires, nano-tubes and nano-rods in the device structure. In recent years it has been observed and experimentally verified that many nanostructures as such can improve solar cell efficiency by modifying the properties of previously used materials and can reduce cost due to their self-assemble property [27]. For instance, single-wall carbon nanotube polymer solar cells are able to produce cheaper, light and flexible devices for space power applications.

#### 1.3.4.5 Up conversion and down conversion for solar cells

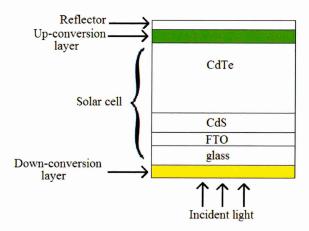

Up and down conversion is a strategy to improve the efficiency of the solar cell. In practice, a photon with a lower energy than the bandgap will be lost in a solar cell and a photon with very high energy will also lose the energy above the bandgap limit due to thermalisation [28]. So, this solar cell uses up conversion technology to convert two or more of the lower energy photons into a photon with energy above the band gap energy. Meanwhile, the down conversion technology converts the excessive high-energy photon into several lower energy photons but the energy is still above the bandgap of the absorber used [28, 29]. Therefore, all the photons now have sufficient energy to be absorbed by the photovoltaic cell. The optimised down-conversion and up-conversion theoretical efficiency limits are 40% and 48%, respectively [30].

Up and down conversion material is a thin film of material, which is fabricated separately from the solar cell device. The up conversion layer usually lies between the solar cell material and the back reflector while the down conversion layer lies on the

front of the solar cell material. This is illustrated in Figure 1.5. The research is in progress to enhance the up and down conversion layers in solar devices.

Figure 1.5: Schematic diagram of the device with up and down conversion layers.

#### 1.3.4.6 Perovskite solar cell

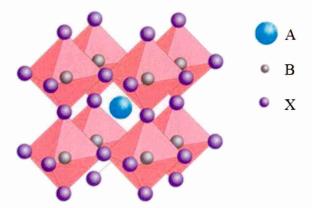

Perovskite solar cells hold an advantage over other typical solar cells in the simplicity of their processing. This infact the extension of the dye sensitized solar cells (DSSCs). Perovskite solar cell is a type of cell containing a perovskite structure compound with the ABX<sub>3</sub> crystal structure of the absorber material [31]. Perovskite materials with an ABX<sub>3</sub> formula as illustrated in Figure 1.6 with A and B are the cations of different size and X is anion. Most of the perovskite solar cells are based on organic-inorganic halide perovskite where A, the larger cation is organic material, B, the smaller cation is inorganic material such as Pb or Sn and X, anion is a halogen such as F, Cl, Br or I [32].

Figure 1.6: Typical Perovskite crystal structure of the form ABX<sub>3</sub>.

Some key attributes of this type of solar cell include strong solar absorption, flexibility and low non-radiative carrier recombination rates. Perovskites are easily synthesised, and their distinctive crystalline structure makes them a perfect match for the

Chapter 1 Introduction

development of efficient solar cells. The efficiency limit of perovskite solar cells is about 31%, which approaches the Shockley-Queisser limit of gallium arsenide (33%). The past three years have seen the extraordinary rapid development of perovskite solar cells and brought them to the attention of the academic community, researchers and industry. The highest conversion efficiency in perovskite solar cell has been reported up to 20.1% by S. Seok from Korea Research Institute of Chemical technology (KRICT) [33]. The current issues are mainly on stability and lifetime of the devices. Once these issues are solved, these materials show high potential in the PV field.

#### 1.4 CdS/CdTe thin film solar cell

Among the different photovoltaic device structures under development, the CdS/CdTe thin film solar cell has attracted considerable attention. The CdS/CdTe solar cell device was first reported in 1963 by Cusano [34]. It was a two-layers solar cell, where the ptype material was Cu<sub>2</sub>Te and the n-type material was CdTe. Cusano reported that this solar cell was a p-n hetero-junction device with efficiency of 6.0%. Typically, CdS/CdTe solar cells have a superstrate structure where the light incident passes through the CdS layer. Therefore, it needs a transparent substrate such as glass. The glass substrate was deposited with a transparent conducting oxide (TCO) layer to serve as a front contact. Glass panels coated with fluorine-doped tin oxide (FTO) or indium-doped tin oxide (ITO) are commercially available. Both coatings provide transparency of the glass/TCO substrate above 85% in the spectral range of interest and low sheet resistance.

The use of CdS as a window layer is ideal, since it has a direct wide bandgap of 2.42 eV, which absorbs only the photons with energy greater than 2.42 eV and transmits almost all other photons to the absorber layer, CdTe. CdS is a binary compound of the group II-VI semiconductor family and generally has a cubic or hexagonal crystal structure with lattice constant of cubic ~5.82 Å and hexagonal (a=4.14 Å, c=6.71 Å) [35, 36]. CdS films are always n-type with a typical carrier concentration in a range of ~10<sup>16</sup> cm<sup>-3</sup> to 10<sup>18</sup> cm<sup>-3</sup> due to the presence of excess cadmium or sulphur vacancies [37]. It also has an electron affinity of 4.50 eV [38], which is similar to that of CdTe and enables the conduction bands of CdS and CdTe to join smoothly at the interface.

CdTe is one of the most attractive semiconductor materials, which is widely used in infrared optical windows and solar cell absorber materials. It commonly has a cubic crystal structure with lattice constant ~6.48 Å, as well as a direct bandgap of 1.45 eV for maximum photovoltaic conversion efficiency [36, 39]. CdTe has a high chemical

stability as well as a high optical absorption coefficient of more than  $5\times10^{-4}$  cm<sup>-1</sup> [38]. The theoretical efficiency of CdTe p-n junction thin film solar cell is expected to be around 28 - 30% [40]. Only about ~2 µm thickness of CdTe is sufficient to absorb a major part of the solar radiation with energy greater than the energy bandgap.

A final step in the solar cell fabrication is the application of back electrical contact to the CdTe layer. One of the most important potential issues of instability in CdTe/CdS solar cells is related to the back contact degradation due to the use of copper as a dopant in Au/Cu contact. Therefore, in this research only, Au contact is used to prevent the degradation issue in solar cell devices.

The work on CdS/CdTe thin film solar cell started in the 1970s, but progress in research and development gained real impetus in the 1980s with the development of various techniques and efficiencies exceeding 10% for CdTe/CdS hetro-junction solar cells [41, 42, 43]. The work from different groups in the 1990s pushed the efficiency to ~15-16% [43]. The commercialisation of the CdTe photovoltaic technology began in the late 1990s and CdTe photovoltaic modules were available in the market with efficiency at about 10% and the output power ranging from 45-55 W at the size scale of 60x120 cm². Over a period of 20 years, the efficiency of CdS/CdTe was not increasing mainly due to the lack of understanding of the material issues and the physics behind the device. There are now two different structures, a simple p-n junction assessed from early 1980s and a combination of n-n heterojunction with a large Schottky barrier at the back contact [44, 45]. It is interesting to observe the efficiency increase from ~16% to 21.5% as reported by the First Solar company during the past few years (2011-2015). Although the reason for this rapid increase is not available to the PV community, this must be related to improve understanding of material issues and device architectures.

Fabrication methods for CdS/CdTe layers have a significant impact on solar cell efficiency and cost. Samples have been developed successfully by several common techniques, such as electrodeposition (ED) [46], close spaced sublimation (CSS) [47], chemical bath deposition (CBD) [48], radio frequency (RF) sputtering [49] and physical vapour deposition (PVD) [50]. The deposition methods should be carefully chosen with the consideration of cost of manufacturing, high quality thin-film structure for high efficiency, proper pollution control and commercial production prospects. Although RF sputtering is a fast method of deposition, the film has a poor quality that reduces the cell efficiency. CBD could provide a dense and smooth CdS layer but the chemical solution waste recycling and management have cause extra cost in manufacturing. Among these techniques, ED has demonstrated numerous advantages due to its simplicity, low-cost

and suitability for the production of macro-scale devices such as solar panels. The highest efficiency in CdTe photovoltaic devices prepared by the ED technique was ~18%, as reported in 2003 [45].

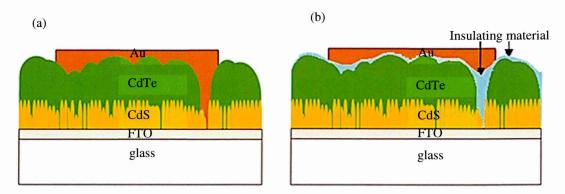

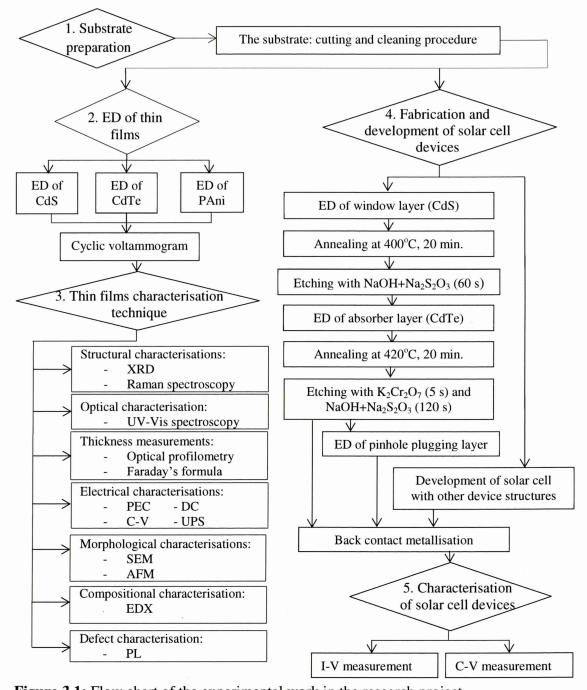

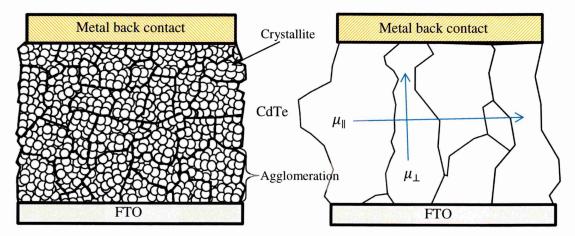

#### 1.5 Current issues in CdS/CdTe solar cell fabrication

A typical CdS/CdTe solar cell consists of glass/FTO/CdS/CdTe/Au structure. During the fabrication process of thin film solar cell devices, pinholes are formed for various reasons. Pinholes are small areas with a missing layer of the semiconducting CdS or CdTe layers. These pinholes are entropy driven and are formed randomly. The pinholes can arise from incomplete coalescence of the CdTe grains during deposition, or due to defects in the underlying surface, and are a continuing concern in thin film polycrystalline devices. If these pinholes are left untreated, they will lead to short-circuit in photovoltaic devices after deposition of a metal contact. In order to prevent this, insulating layers can be introduced to fill these pinholes. PAni is a semi-insulating polymer, with tuneable bandgap, high chemical stability and has been widely used in various fields. A very thin layer of PAni film has been proposed to plug these pinholes in order to cover the leakage part, forming an MIS type structure, increasing the barrier's height and consequently improving the efficiency of solar cells.

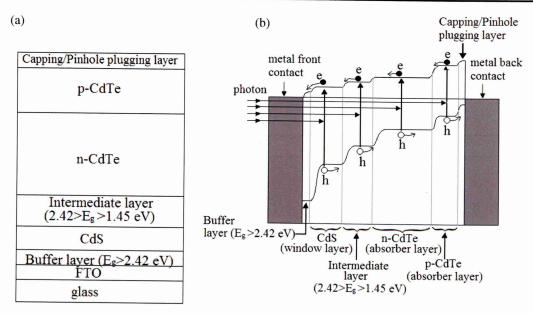

**Figure 1.7:** Schematic diagram of (a) conventional CdS/CdTe thin film solar cell and (b) proposed CdS/CdTe thin film solar cell with a pinhole plugging layer.

During fabrication of CdTe/CdS thin film solar cells, a CdCl<sub>2</sub> treatment is essential after the deposition of a CdTe layer. The use of CdCl<sub>2</sub> treatment has been practised extensively since the 1979 to improve the material properties, in particular enhancement of the grain size and, consequently, an increase in solar cell efficiency. However, the CdCl<sub>2</sub> solution should be prepared with very high concentration in order to see a clear outcome [51, 52]. Somehow, the highly saturated CdCl<sub>2</sub> does not only

promote the larger grain growth, but also generates larger voids or pinholes between the grains. The combination of other halogen elements is proposed to enhance the reaction of the CdCl<sub>2</sub> and treatment process. Halogen elements are those such as bromine, iodine and fluorine. Among these, fluorine has been chosen since it has small atomic radii, which make it easy to diffuse into the grain boundaries and perform better treatment. In fact, Echendu and Mazzamoto have reported the advantage of using CdCl<sub>2</sub> in the presence of fluorine in improvement of material properties and solar cell device performance [53, 54]. Apart from that, the Ga-doped in CdTe has been reported by Fernández as able to dissolve the Te precipitates and enhance the electrical property of CdTe. Therefore, in this research, a variety of chemical treatments on CdS and CdTe films has been proposed to effectively improve the efficiency of CdS/CdTe solar cells.

Another challenge is how to improve the entire device parameters, including short-circuit current density  $(J_{sc})$ , open circuit voltage  $(V_{oc})$  and fill factor. The theoretical maximum of efficiency,  $J_{sc}$  and  $V_{oc}$  base on Shockley-Queisser limit are ~31%, ~30.5 mA·cm<sup>-2</sup> and ~1200 mV [55, 56]. Several factors that hindered from reaching these theoretical maximum limits are including the defects, oxidation, losses, impurities, poor crystallinity, low carrier density and mobility. The strategies for improving the solar cell parameters can be done by using high purity chemical in order to reduce the impurity. The annealing process and chemical treatments are helpful to reduce the defects and improve the crystalinity of the materials. In fact, many parameters in all features, including material properties, device architectures and device fabrication should be optimised properly before fabricating the solar cell. For that reason, the proper optimisation of each layer including CdS and CdTe films will be characterised properly before using them in device fabrication. In addition, the fabrication process, in particular the etching process and variety of device structures, including the incorporation of a buffer layer and capping layer obtained from other researchers within the SHU solar energy group will be explored in this research work.

#### 1.6 Research objectives

Based on the introduction and current issues discussed above, the research objectives of this programme are formulated as follows:

1. Optimise the growth parameter of CdS electrodeposition from an aqueous electrolyte containing CdCl<sub>2</sub> and ammonium thiosulphate ((NH<sub>4</sub>)<sub>2</sub>S<sub>2</sub>O<sub>3</sub>). Full characterisation of CdS thin films, using a wide range of analytical techniques, such as XRD, Raman spectroscopy, UV-Vis spectrometer, optical profilometer,

DC conductivity measurement, PEC cell characterisation, SEM, AFM and EDX. Fabrication of solar cell device by using CdS thin film as a window layer.

- 2. Preparation of CdTe thin films, electrodeposited from an aqueous solution containing CdCl<sub>2</sub> as the Cd source instead of typical CdSO<sub>4</sub>. Optimise the growth parameter of CdTe electrodeposition through the variety of analytical techniques, such as XRD, Raman spectroscopy, UV-Vis spectrometer, optical profilometer, DC conductivity measurement, PEC cell characterisation, CV measurement, SEM and AFM. Fabrication of solar cells by using n- and p-CdTe thin films as absorber layer.

- 3. Establish the growth of PAni thin films, using electrodeposition technique. Full characterisation of PAni thin films, using a wide range of analytical techniques such as XRD, UV-Vis spectrometer, optical profilometer, DC conductivity measurement and SEM. Fabrication of solar cells by incorporating PAni as a pinhole plugging layer.

- 4. Development of low-cost solar cell devices, fabricated using the three materials characterised above. The general main structure of the device is glass/FTO/CdS/CdTe/back contact, and an attempt to use PAni for pinhole plugging layers will be made to study the effect of this layer on the device performances.

- 5. Development of solar cells with other device structures involving zinc sulphide (ZnS), cadmium selenide (CdSe) and zinc telluride (ZnTe) for buffer or capping layers to achieve highest possible efficiency.

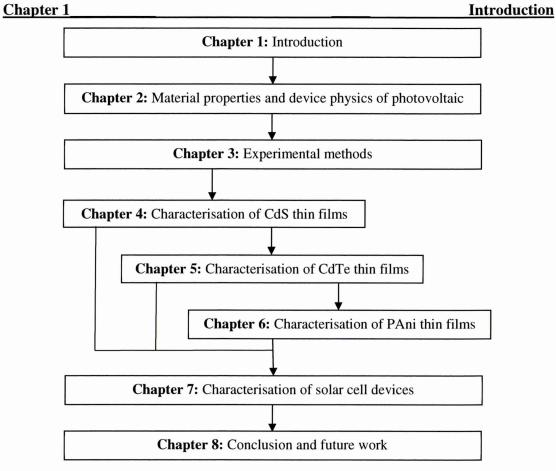

#### 1.7 Organisation of chapters

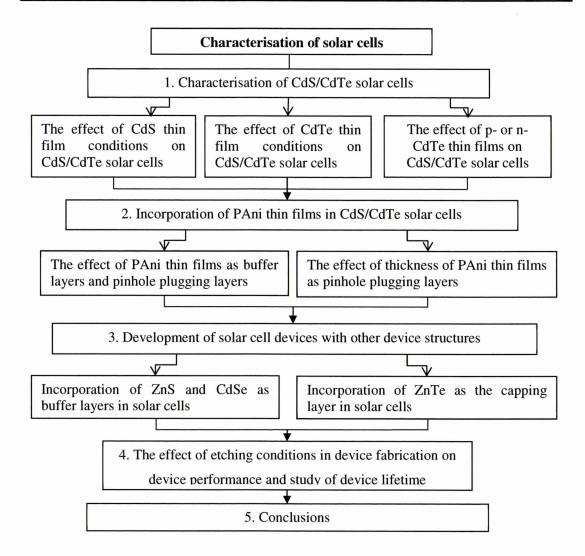

This thesis is organised into eight chapters, as illustrated in Figure 1.8. The introduction and the research background of this work are presented in the first two chapters. This is then followed by the explanation on experimental work including material growth and characterisation techniques as well as solar cell fabrication procedure and assessments. Chapters 4 to 6 are presented on electrodepositions and characterisations of the main three materials used in this work. These are such as CdS, CdTe and PAni thin films. The device assessments are presented at Chapter 7 and finally the conclusion and suggestion for future work are presented in chapter 8. The summary of each chapter is as follows:

Chapter 1 discusses the current issue on energy, a brief review on other renewable energy sources and further in-depth discussion on solar energy, including solar

radiation, photovoltaic technology, solar cells, brief history of solar cells and CdS/CdTe thin film solar cell. Research objectives have been proposed after a broad discussion on current issues in CdS/CdTe solar cell fabrication.

Chapter 2 reviews the literature of solar cells. The review on p-n junction, Schottky barrier, ohmic contact, thin film deposition, as well as material background including CdS, CdTe and PAni has been discussed intensively in this chapter.

The experimental methods of this research are discussed in Chapter 3. The research work has been divided into five main parts, which are sample preparation, electrodeposition of thin films, characterisation of thin films, development of solar cell devices and characterisation of solar cell devices.

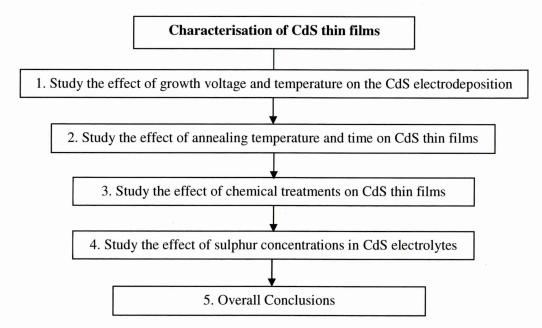

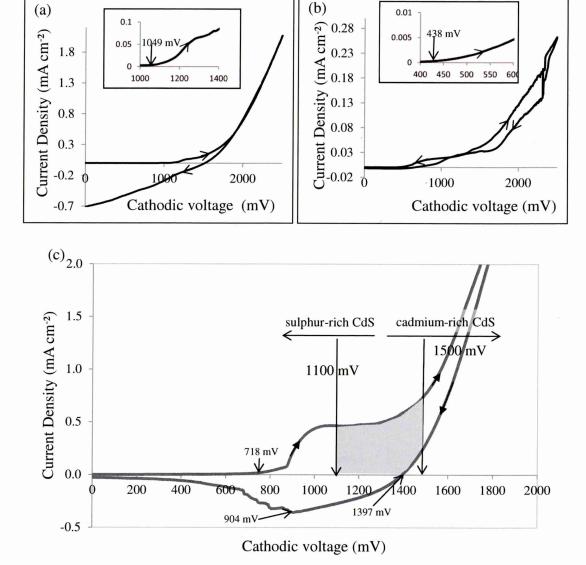

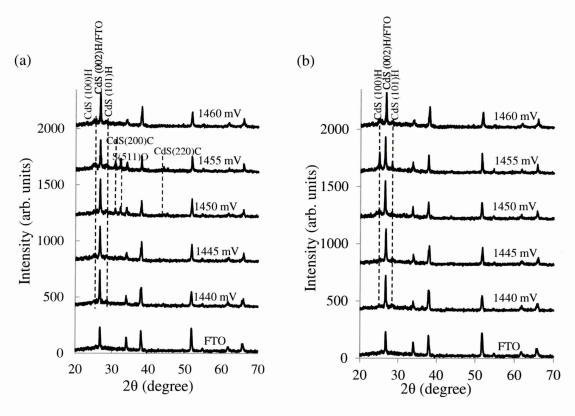

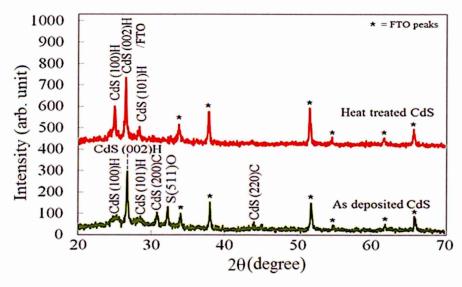

The materials growth and characterisations The characterisation of CdS thin films under various conditions, such as growth parameters, annealing conditions, chemical treatments and sulphur concentrations in CdS precursor has been presented in Chapter 4.

Chapter 5 presents the growth and material characterisation of CdTe thin films. The effects of growth voltage, annealing conditions and chemical treatments have been studied systematically through various characterisation techniques.

The effort to establish PAni thin films from electrodeposition has been presented in Chapter 6. PAni thin films have been studied with various growth conditions, annealing temperatures and pH concentrations.

Chapter 7 presents the characterisation of solar cell devices, mainly from the CdS and CdTe thin films. The attempt to use PAni for pinhole plugging layers, buffer layers, capping layers, intermediate layers and graded bandgap solar cells has also been shown in this chapter. The effect of etching conditions in device fabrication and analysis on device lifetime is discussed in the final part of this chapter.

Final conclusion, future work and the thoughts on the next generation solar cells have been presented in Chapter 8. This discussion includes the challenges encountered in this work and suggestions for future work.

Figure 1.8: Outline of chapters.

#### References

- B. Sorenson, Renewable Energy, 3rd edition, Elsevier Science Publishers, New York (2004).

- 2. K. Ahmed, Renewable Energy Technologies: A review of the status and costs of selected technologies, World Bank Technical Publications, 240 (1994) 169.

- 3. R. Bailis, M. Ezzati, D. M. Kammen, Science, 308:57 (2005) 98-103.

- 4. S. J. Smith, H. Pitcher and T. M. L. Wigley, Global and Planetary Change, 29:1-2 (2001) 99-119.

- 5. I. Dincer, Renewable and Sustainable Energy Reviews, 4 (2000) 157-175.

- 6. J. R. Moreira and A. D. Poole, Hydropower and its constraints, 1<sup>st</sup> edition, Island Press, Washington DC, United State (1993).

- 7. R. Saidur, N. A. Rahim, M. R. Islam and K.H. Solagi, Renewable and sustainable energy reviews, 15 (2011) 2423-2430.

- 8. F. Ma and M. A. Hanna, Bioresource Technology, 70:1 (1999) 1-15.

- 9. D. L. Gallup, Geothermics, 38:3 (2009) 326-334.

- 10. J. Lemmens, <a href="http://blogs.dnvgl.com/utilityofthefuture/the-future-of-solar-energy-concentrated-solar-power-vs-photovoltaic-power-plants">http://blogs.dnvgl.com/utilityofthefuture/the-future-of-solar-energy-concentrated-solar-power-vs-photovoltaic-power-plants</a> (Retrieved 24/8/2015).

- 11. http://nineplanets.org/sol.html (Retrieved 10/10/2015)

- 12. ASTM Standard G173- 03, ASTM International, West Conshohocken, PA, (2008).

- 13. http://www.eyesolarlux.com/Solar-simulation-energy.htm#International Standards for Solar Simulation Spectral Distribution (Retrieved 20/8/2015).

- 14. S. J. Fonash, Solar Cell Device Physics, 2<sup>nd</sup> edition, Academic Press Publication, Massachusetts, United States (2010).

- 15. I. M. Dharmadasa, Advances in Thin-Fim Solar Cells, 1<sup>st</sup> edition, Pan Standford Publishing, Singapore (2013).

- 16. J. Perlin, <a href="http://www.popsci.com/article/science/invention-solar-cell">http://www.popsci.com/article/science/invention-solar-cell</a> (Retrieved 10/8/2015).

- 17. E. Wesoff, <a href="http://www.greentechmedia.com/articles/read/Solar-Star-Largest-PV-Power-Plant-in-the-World-Now-Operational">http://www.greentechmedia.com/articles/read/Solar-Star-Largest-PV-Power-Plant-in-the-World-Now-Operational</a> (Retrieved 10/10/2015).

- X. D. Konig, K. Casalenuovo, Y. Takeda, G. Conibeer, J. F. Guillemoles, R. Patterson, L. M. Huang and M. A. Green, Physica E: Low-dimensional System and Nanostructures, 42:10 (2010) 2862-2866.

- 19. R. T. Ross and A. J. Nozik, Journal of Applied Physics, 53:5 (1982) 3813–3818.

Chapter 1\_\_\_\_\_ Introduction

20. Y. Takeda, T. Ito, T. Motohiro, D. K"onig, S. Shrestha, and G. Conibeer, Journal of Applied Physics, 105:7 (2009) 074905.

- 21. P. Kirk and M. V. Fischetti, Phys. Review B, 86:16 (2012) 165206.

- 22. B. M. A. Green and S. Pillai, Nature Photonic, 6 (2012) 130-132.

- 23. A. K. R. Catchpole and A. Polman, Opt. Express, 16 (2008) 21793-21800.

- 24. L. Rachel, W. Nicholas, M. Nina, R. Daniel, H. Naiman, Q. Daniel and K. E. Howard, 6:4 (2012) 2865–70.

- 25. H. F. Dam and T. Larsen-Olsen, (<a href="http://plasticphotovoltaics.org/lc/lc-polymersolarcells/lc-how.html">http://plasticphotovoltaics.org/lc/lc-polymersolarcells/lc-how.html</a> (Retrieved 29/08/2015)

- 26. A. Kongkanand, K. Tvrdy, K. Takechi, M. Kuno and P. V. Kamat, Journal of the American Chemical Society, 130: 12 (2008) 4007-4015.

- 27. H. J. Snaith, The journal of physical chemistry letters, 4.21 (2013) 3623-630.

- 28. H. Lin, J. M. Hueso, D. Chen, Y. Wang and B. S. Richards, Materials Research Bulletin 47:12 (2012) 4433-4437.

- 29. D. Verma, T. O. Saetre and O. M. Midtgard, Photovoltaic Specialists Conference (PVSC), 38th IEEE, Austin, Texas (2012) 2608-2613.

- 30. X. Wang and Z. M. Wang, High-Efficiency Solar Cells: Physics, Materials and Devices, e-book, Springer International Publishing, Switzerland (20140).

- 31. H. J. Snaith, The Journal of Physical Chemistry Letters, 4.21 (2013) 3623-630.

- 32. M. A. Green, A. Ho-Baillie and H. J. Snaith, Nature Photonics, 8 (2014) 506-514.

- 33. M. Gough, <a href="http://www.sciencealert.com/low-cost-perovskite-solar-cell-sets-efficiency-record">http://www.sciencealert.com/low-cost-perovskite-solar-cell-sets-efficiency-record</a> (Retrieved 1/10/2005)

- 34. D. A. Cusano, Solid State Electronics, 6 (1963) 217-232.

- 35. K. L. Chopra and S. K. Das, Thin Film Solar Cells, Plenum Press New York and London, (1983).

- 36. N. A. Abdul-Manaf, A. R. Weerasinghe, O. K. Echendu and I. M. Dharmadasa, Journal of Materials Science: Materials in Electronics: 26: 4 (2015) 2418-2429.

- P. Capper, Narrow Gap II-VI Compounds for Optoelectronic and Electromagnetic Applications in Infrared Detectors and Emitters: Materials and Devices, ebook, Springer (1997).

- 38. A. C. Beer and K. Zanio, Semiconductors and Semimetals: Cadmium Telluride, 2<sup>nd</sup> edition, Academic Press, (1978).

- 39. F. V. Wald, Revue De Physique Appliquée, 12 (1977) 277.

- 40. First Solar, 2004. http://www.firstsolar.com/index.html. (Retrived 24/8/2015).

- 41. B. M. Basol, Solar Cells, 23 (1988) 69–88.

Chapter 1 \_\_\_\_\_ Introduction

- 42. T. L. Chu, Solar Cells, 23 (1988) 31-48.

- 43. K. Mitchell, A. L. Fahrenbruch and R. H. Bube, Journal of Applied Physics, 48 (1977) 829-830.

- 44. I. M. Dharmadasa, A. Ojo, H. I. Salim and R. Dharmadasa, Energies, 8:6 (2015) 5440-5458.

- 45. N. B. Chaure, A. P. Samantilleke and I. M. Dharmadasa, Solar Energy Materials and Solar Cells, 77:3 (2003) 303-317.

- 46. B. M. Basol, Solar Energy Material and Solar Cells, 23 (1988) 69.

- 47. C. S. Ferekides, D. Marinskiy, V. Viswanathan, B. Tetali, V. Palekis, P. Selvaraj,D. I. Morel, Thin Solid Films, 361-362 (2000) 520.

- 48. D. Cunningham, M. Rubcich, D. Skinner, Progress in Photovoltaics: Research and Applications, 10 (2002) 159.

- 49. N. Romeo, A. Bosio, R. Tedeschi, A. Romeo, V. Canevari, Solar Energy Material and Solar Cells, 58 (1999) 209.

- 50. T. Takamoto, T. Agui, H. Kurita and M. Ohmori, Solar Energy Materials and Solar Cells, 49 (1997) 219-225.

- 51. W. K. Metzger, D. Albin, D. Levi, P. Sheldon, X. Li, B. M. Keyes and R. K. Ahrenkiel, Journal of Applied Physics, 94:5 (2003) 3549-3555.

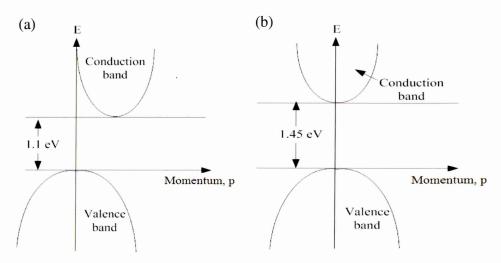

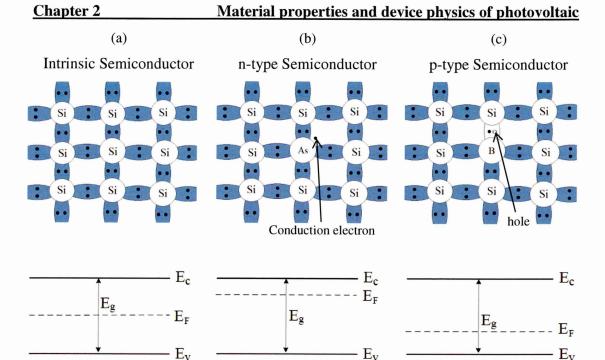

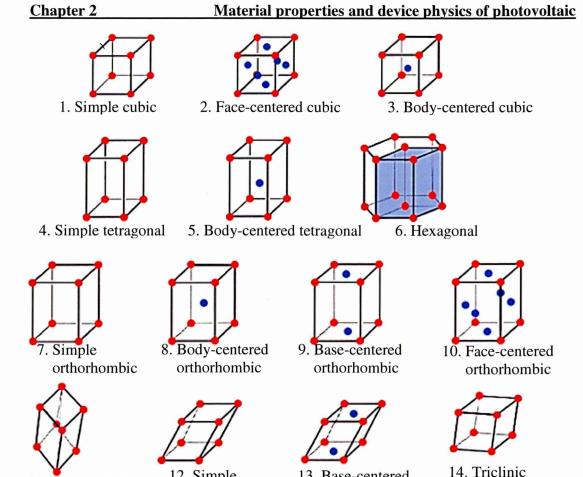

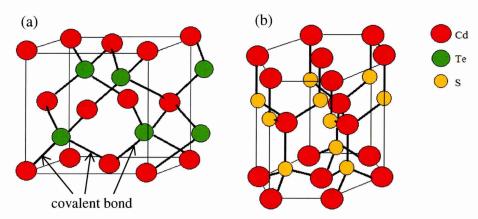

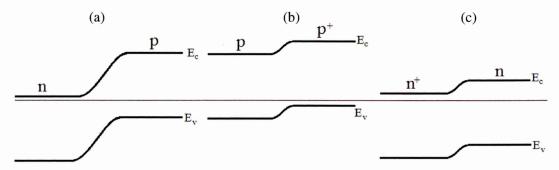

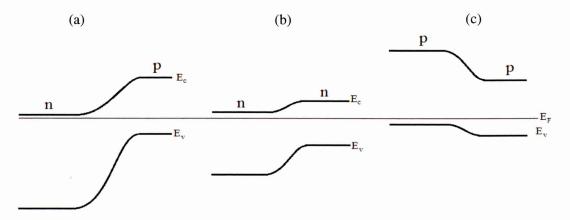

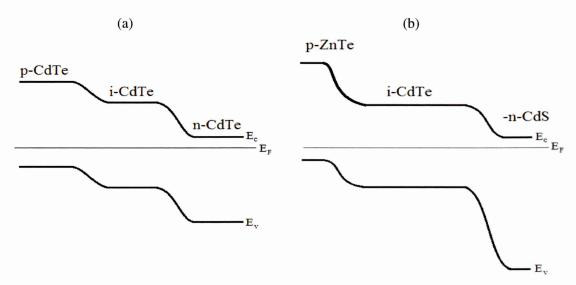

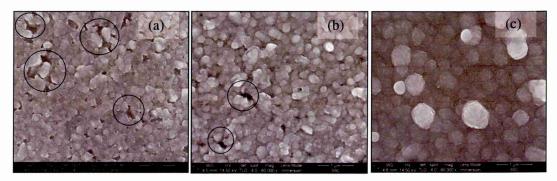

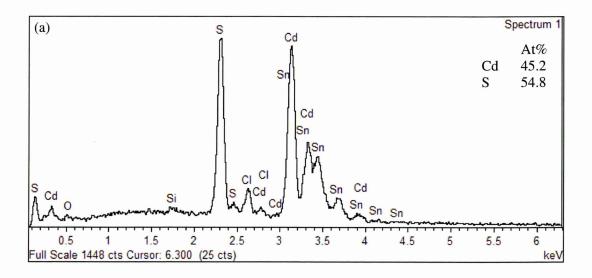

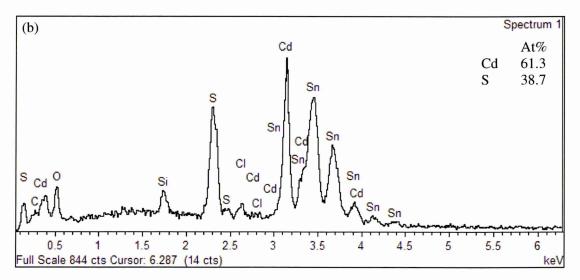

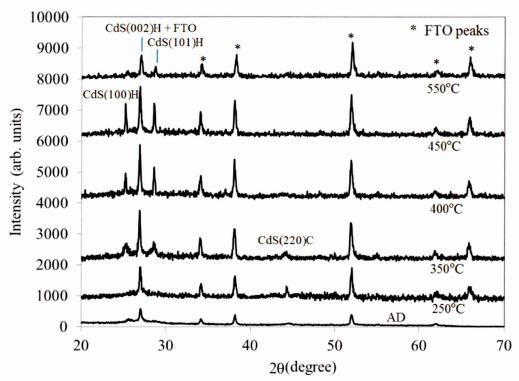

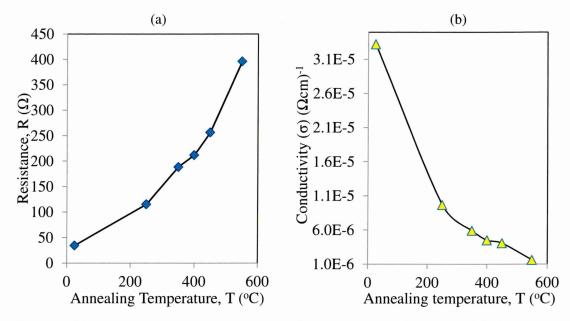

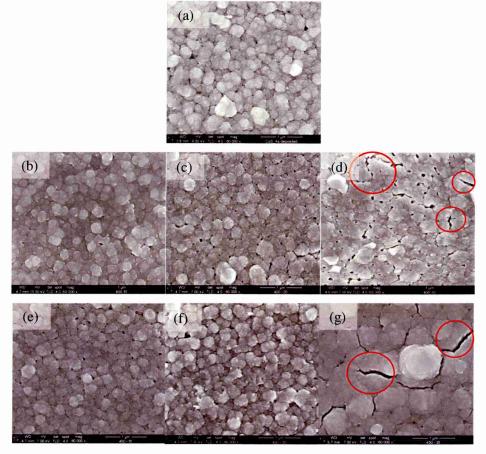

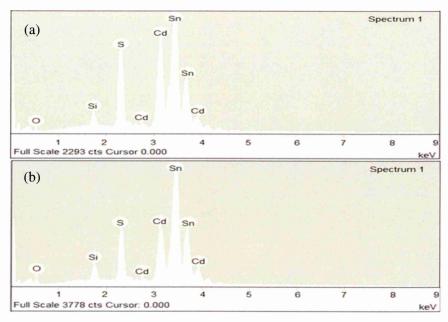

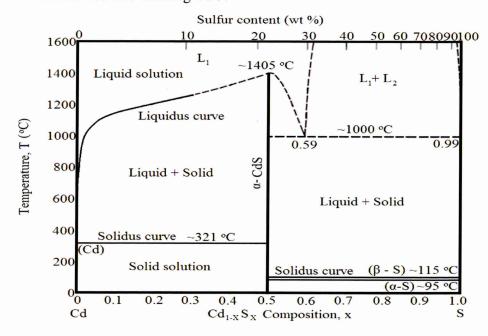

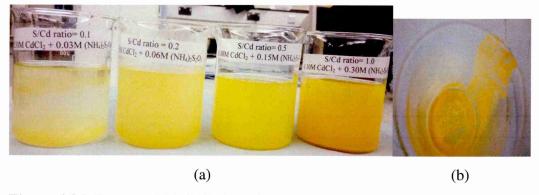

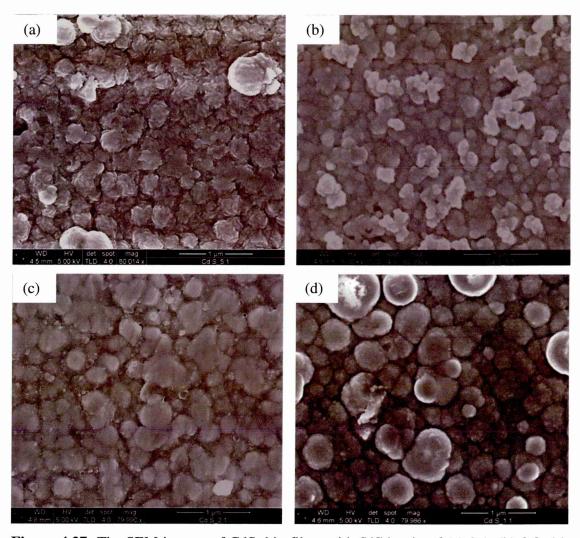

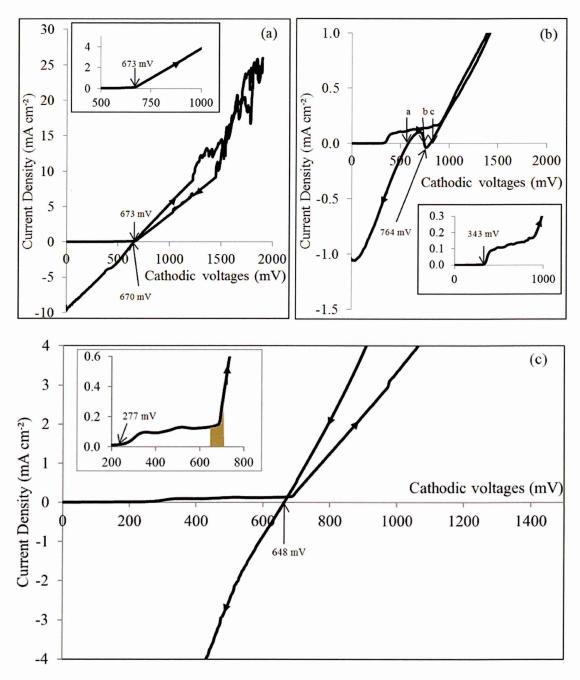

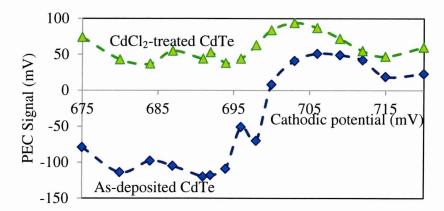

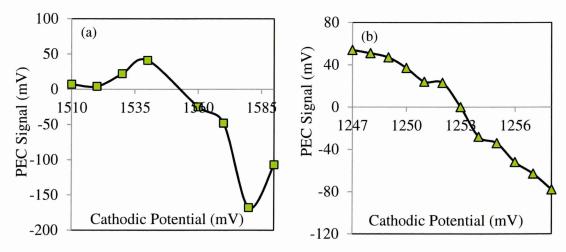

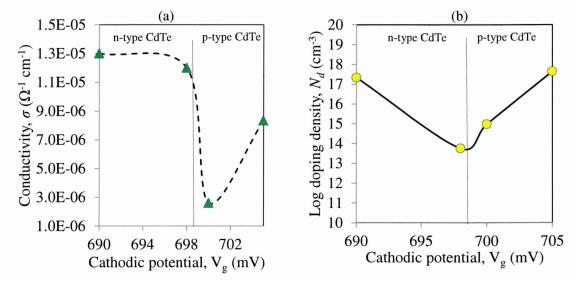

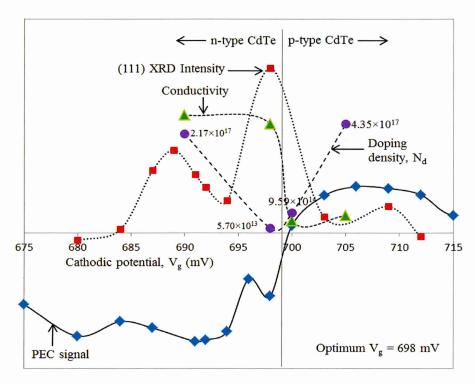

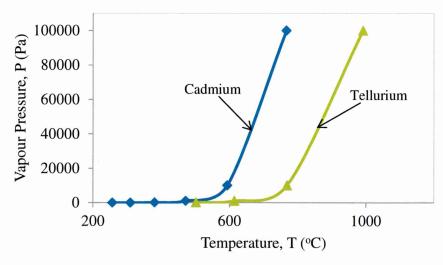

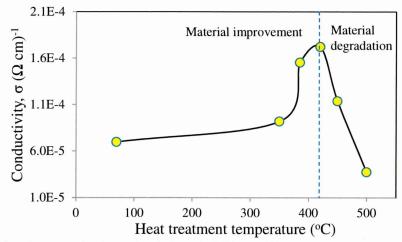

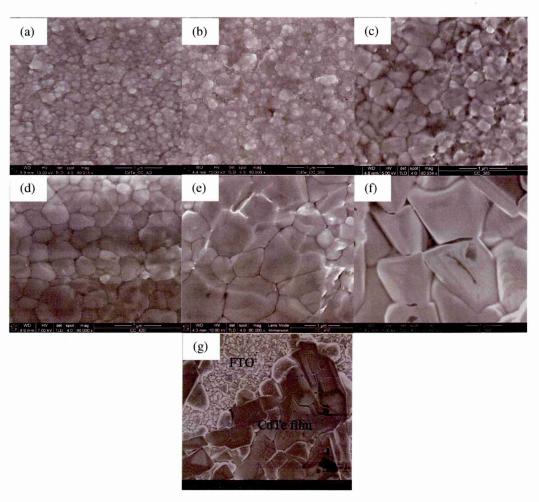

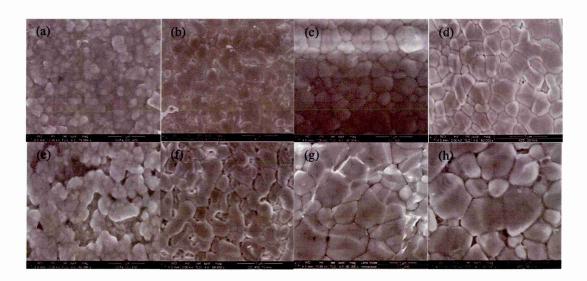

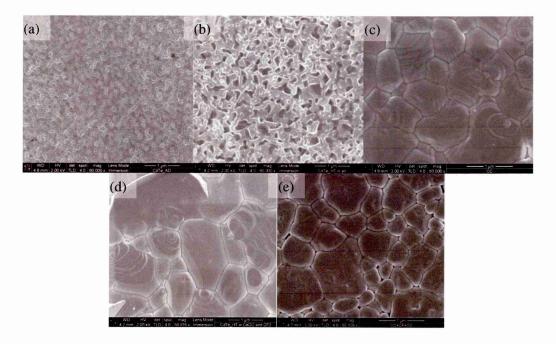

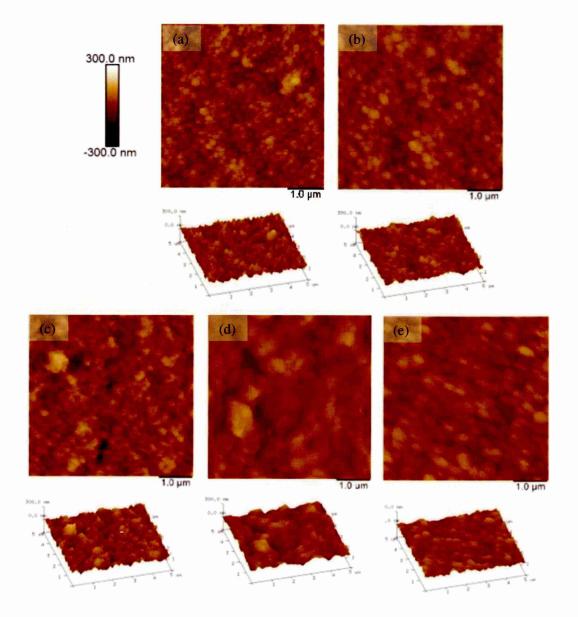

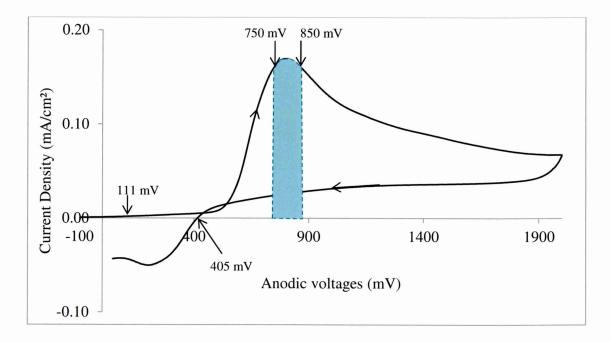

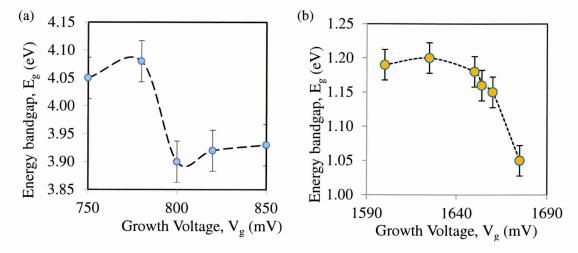

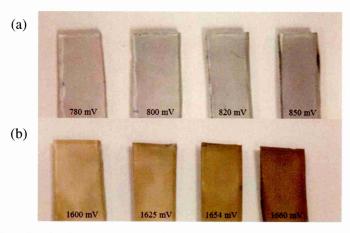

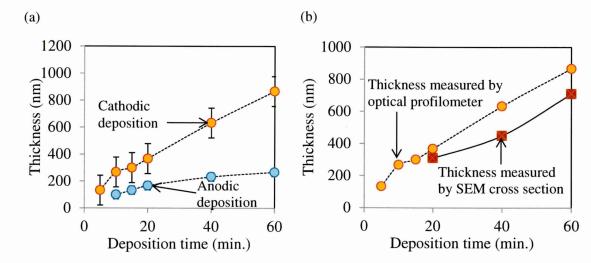

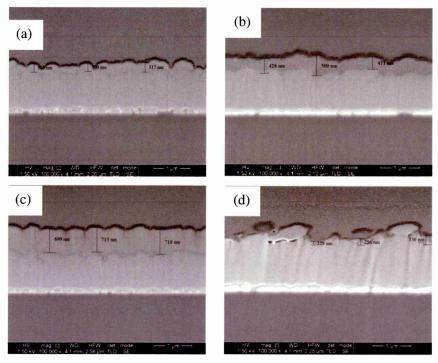

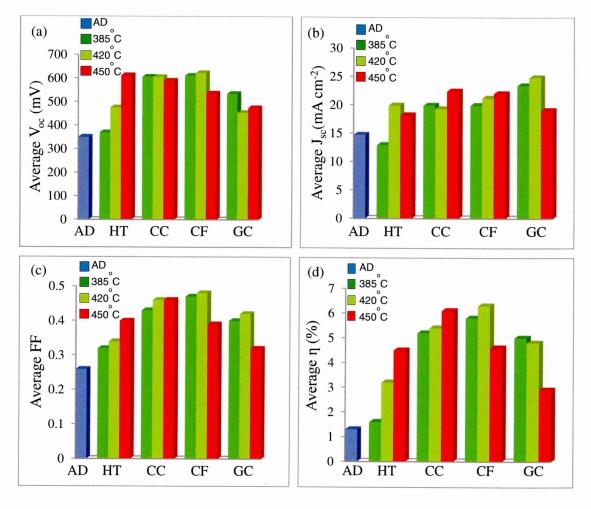

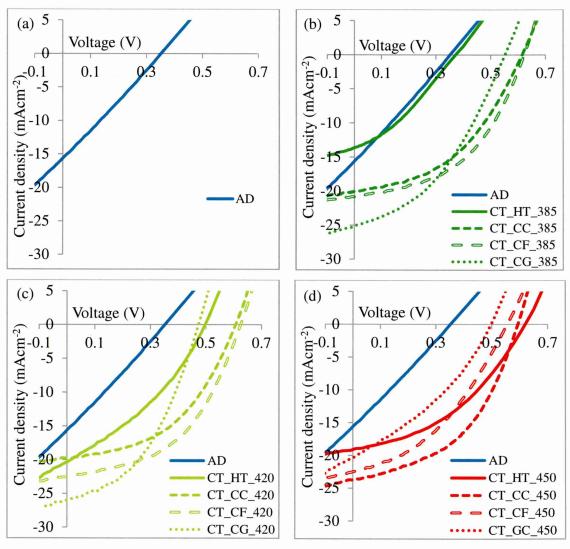

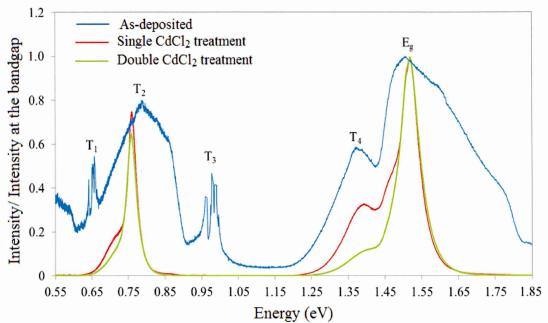

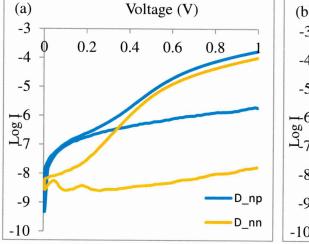

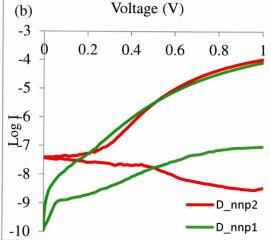

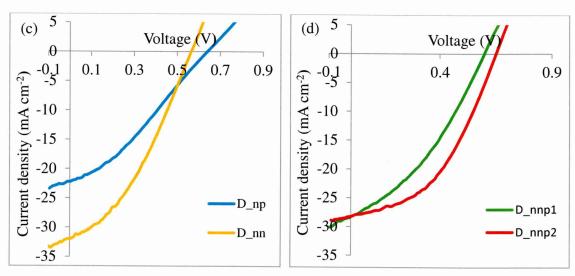

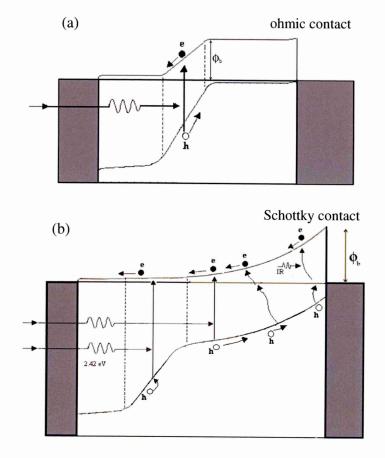

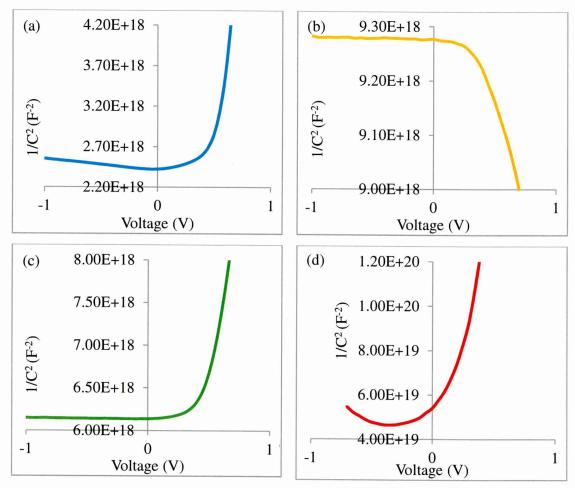

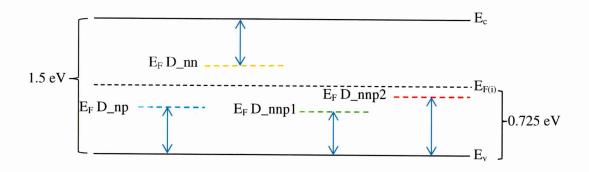

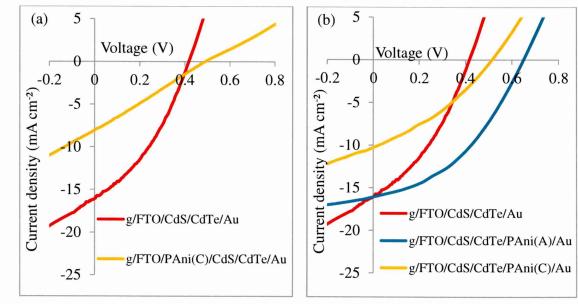

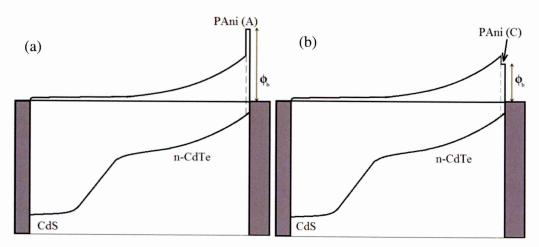

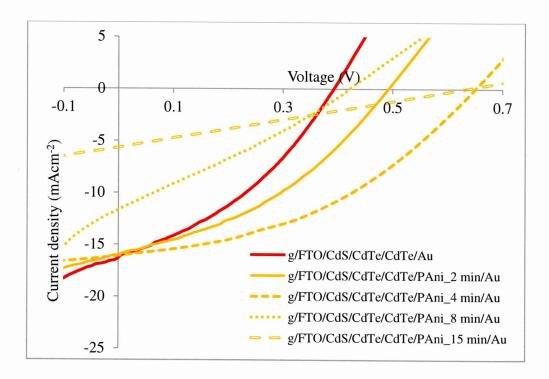

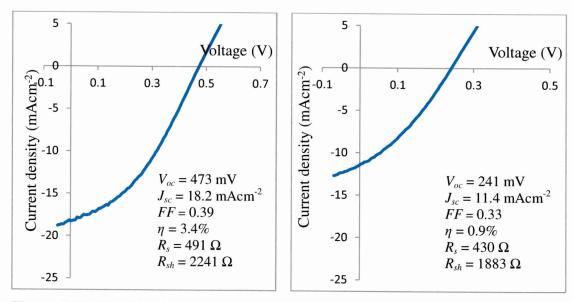

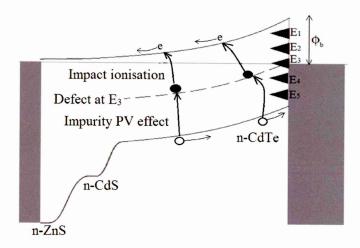

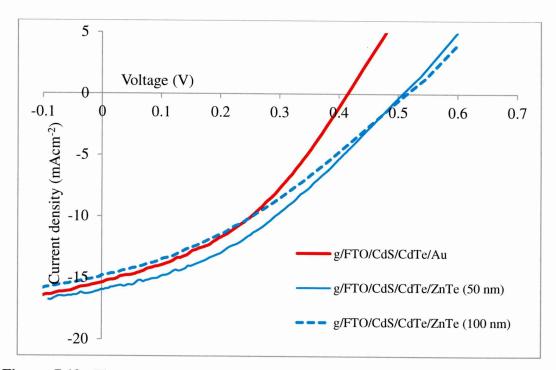

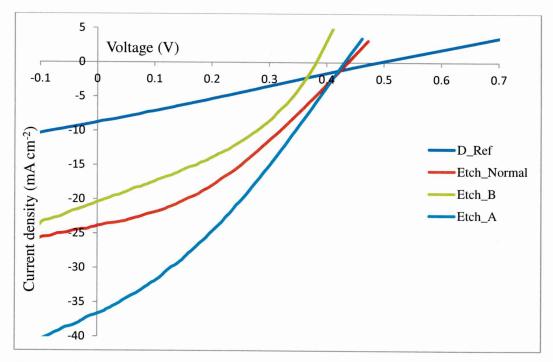

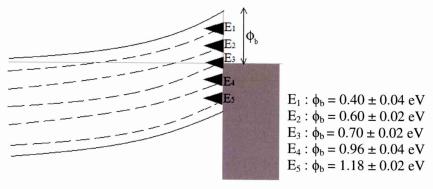

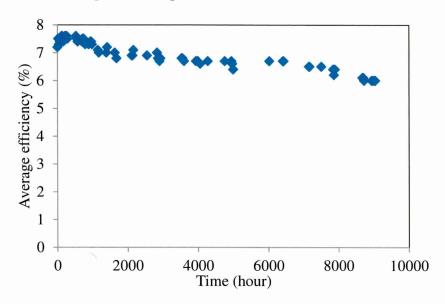

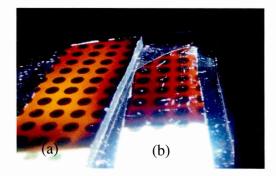

- 52. X. Wu, P. Sheldon, Y. Mahathongdy, R. Ribelin, A. Mason, H. R. Moutinho and T. J. Coutts, "CdS/CdTe thin-film solar cell with a zinc stannate buffer layer." AIP Conference Proceedings. IOP Institute of Physics Publishing Limited (1998).