Processing of semiconductors and thin film solar cells using electroplating.

MADUGU, Mohammad Lamido.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/19997/

### A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/19997/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

Sheffield S1 1WD

102 114 757 5

ProQuest Number: 10697304

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10697304

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

# Processing of Semiconductors and Thin Film Solar Cells Using Electroplating

# Mohammad Lamido Madugu

A thesis submitted in partial fulfilment of the requirements of

Sheffield Hallam University for the degree of

Doctor of Philosophy

September, 2016

# **Declaration**

I hereby declare that the work presented in this thesis is my own work, carried out by me and has not been submitted elsewhere for the award of any degree.

Mohammad Lamido Madugu

# **Dedication**

To the memory of my late uncle, Alhaji Madugu Abubakar for his love and caring, may Allah (S.W.A) have mercy on him.

### Acknowledgement

The successful completion of this thesis could not have been possible without the help and contributions of many people. First and foremost, I would like to express my most sincere gratitude to my director of studies and supervisor Prof. I.M. Dharmadasa for his excellent guidance and encouragement. I remained indebted for tapping from his wealth of knowledge in the area of semiconductor devices and applications. I would also like to thank my second supervisor, Prof. Alexei Nabok for his help in the course of this work.

To my colleagues in the electroplating group of Materials and Engineering Research Institute (MERI), Dr Ajith Weerasinghe, Dr O.K. Echendu, Dr Fijay Bn Fauzi, Dr H.I. Salim, Dr A. Abdul-Manaf, Dr O.I. Olusola, A.A. Ojo, I appreciate you all for the moral support and useful discussions during this programme. I appreciate sincerely the contributions of Abubakar Mohammed for helping in the formatting of this document and Burak Kadem is also thank for his help. I would also like to say thank you to Dr D.G. Diso and Dr Inuwa Faragai for their help.

My special thanks goes to MERI staff members, Corrie Houton, Rachael Toogood, Deeba Zahoor, Stuart Creasy, Bob Burton, Paul Allender, Gary Robinson, Dr Yashodhan Purandare, Vinay Patel and all who in one way or the other help in the completion of this thesis. I am also indebted to our collaborators who helped in vital experimental measurements in this thesis. Prof. Thad Druffel and Dr R. Dharmadasa and their research group from the University of Louiseville, USA, for UPS and PL measurements. Prof. M. Dergacheva, Institute of Organic Catalysis and Electrochemistry, Kazakhstan, for AFM measurements.

Let me also thank sincerely my colleagues at the Physics Department, Gombe State University; Dr Seydou Hankouraou, Dr Abubakar D. Bajoga and others who supported me with goodwill messages and prayers during this research programme.

Many thanks to my brothers; Yaya Maikudi, Usman, Maikudi, Jaji, Muhammad (Julde), Maigari, Alh. Goggo, Saleh, and Umaru for their prayers and support in many more ways. Baba A. Madugu is very much appreciated for taking pains to look after my family while i was away. I would like to thank my friends in MERI and Sheffield for the good time and moral support during this project, these include; Khalid R, Faraj K,

Ali Dastan, Hadi Al-Sagur, Mukhtar Libya, Muhammad Khamkham, Ahmad Adam, Ma'aruf Raheem, Tauqeer Hussain and Ali Madlool, Dr Mu'azu Shehu, Dr M.Saddiq, Dr Usman Ladan, Lawan Grema, Faisal Abubakar and Dr Taofeek Bn Muhammad.

To my late parent, may Allah (SWA) forgive their short comings and grand them Jannatil Firdaus amin. The encouragement, love and prayer of my family have been my strength throughout this research programme. I thank you all for this priceless caring. Many thanks to Anne Kingstone a very good friend of my family who made them feel at home while in Sheffield.

To my lovely wife, Adama M. madugu (Hajja Gana), I appreciate her patience, sacrifices and support in taking good care of me and our children through this difficult journey. I always remember when my young Abdul will rush and try to open the door for me after a hectic day. I would also like to thank my sponsor, Petroleum Technology Development Fund (PTDF), Abuja, Nigeria. Lastly, Gombe State University is sincerely appreciated for financial assistance in the course of this programme.

### List of publications

#### **Journal Publications**

- 1. **M.L. Madugu**, L. Bowen, O.K. Echendu, I.M. Dharmadasa, Preparation of indium selenide thin films by electrochemical technique, J. Mater. Sci. Mater. Electron. 25 (2014) 3977-3983.

- 2. **M.L. Madugu**, O.I. Olusola, O.K. Echendu, B. Kadem, I.M. Dharmadasa, Intrinsic Doping in Electrodeposited ZnS Thin Films for Application in Large-Area Optoelectronic Devices, J. Eelectron. Mater. (2016).

- 3. O.I. Olusola, M.L. Madugu, I.M. Dharmadasa, Growth of n- and p-type ZnTe semiconductors by intrinsic doping, Mater. Res. Innov. 19 (2015) 497-502.

- 4. N.A. Abdul-Manaf, H.I. Salim, **M.L. Madugu**, O.I. Olusola, I.M. Dharmadasa, Electroplating and characterisation of CdTe thin films using CdCl<sub>2</sub> as the cadmium source, Energies. 8 (2015) 10883-10903.

- 5. O.I. Olusola, **M.L. Madugu**, N.A. Abdul-Manaf, I.M. Dharmadasa, Growth and characterisation of n- and p-type ZnTe thin films for applications in electronic devices, Curr. Appl. Phys. 16 (2016) 120-130.

- 6. I.M. Dharmadasa, O.K. Echendu, F. Fauzi, N.A. Abdul-Manaf, O.I. Olusola, H.I. Salim, **M.L. Madugu**, A.A. Ojo, Improvement of composition of CdTe thin films during heat treatment in the presence of CdCl<sub>2</sub>, Submitt. to J. Mater. Sci. Mater. Electron. (2016).

- A.A. Ojo, H.I. Salim, O.I. Olusola, M.L. Madugu, I.M. Dharmadasa, Effect of thickness: A case study of electrodeposited CdS in CdS/CdTe based photovoltaic devices, Submitt. to J. Mater. Sci. Mater. Electron.

- 8. O.I. Olusola, **M.L. Madugu**, A.A. Ojo, I.M. Dharmadasa, Investigating the effect of GaCl<sub>3</sub> incorporation into the usual CdCl<sub>2</sub> treatment on CdTe-based solar cell device structures, Curr. Appl. Phys. 17 (2017) 279-289.

- 9. O.I. Olusola, **M.L. Madugu,** I.M. Dharmadasa, Investigating the electronic properties of multi-junction ZnS/CdS/CdTe graded bandgap solar cells, Submitt. to J. Mater. Chem. and Phys. (2016).

#### **Conference Proceedings**

- 10. M.L. Madugu, P. A. Bingham, H. I. Salim, O. I Olusola and I. M. Dharmadasa, Development of In<sub>x</sub>Se<sub>y</sub> Buffer Layers for Applications in CdTe Based Thin Film Solar Cells, in: Proc. of 29<sup>th</sup> European Photovoltaic Solar Energy Conference and Exhibition, Amsterdam, The Netherlands, (2014) pp. 1847-1851. DOI: 10.4229/EUPVSEC20142014-3DV.2.48 (Poster).

- 11. **M.L. Madugu**, L. Bowen, O.K. Echendu, I.M. Dharmadasa, Characterisation of electrodeposited In<sub>x</sub>Se<sub>y</sub> for thin film solar cell application, in proc. of PVSAT-10, Loughborough University, UK, (2014), PP 185-188 (Poster).

- 12. **M.L. Madugu,** I.M. Dharmadasa, Preparation of ZnS thin film for Application in photovoltaic device fabrication, UK Semiconductors, 9-10<sup>th</sup> July, Sheffield Hallam University, 2014 (Poster).

- 13. **M.L. Madugu** and I.M. Dharmadasa, Development of CdS/CdTe solar cell using In<sub>x</sub>Se<sub>y</sub> buffer layer, Material and Engineering Research Institute (MERI) research symposium, May 19-20, 2015, at Sheffield Hallam University, UK. (Oral presentation).

- 14. M.L. Madugu, O.I. Olusola and I.M. Dharmadasa, Electroplating of n-type and p-type ZnS thin films by Intrinsic doping, Photovoltaic Technical Conference (PVTC), "From advance Materials and Processes to Innovative Application, May 27-29, 2015; At Centre de Congrés, Aixen Provence (Oral and Poster presentations).

- 15. **M.L. Madugu,** I.M. Dharmadasa, The effect of annealing temperature on the structural, optical and and morphological properties of cadmium telluride (CdTe) thin films, UK Semiconductors, 1-2 July, Sheffield Hallam University, 2015 (Poster).

- 16. O.I. Olusola, M.L. Madugu, I.M. Dharmadasa, Development of n- and p-type ZnTe Semiconductors for application in Electronic Devices, UK Semiconductors & UK Nitrides Consortium Summer Meeting, Sheffield, United Kingdom, 1-2 July, 2015, pp. 130 (Poster)

- 17. **M.L. Madugu**, I.M. Dharmadasa, The effects of inclusion of fluorine in the CdCl<sub>2</sub> treatment on FTO/n-In<sub>x</sub>Se<sub>y</sub>/n-CdS/n-CdTe Multi-layer solar cells, in Proc. of PVSAT-12, University of Liverpool, Liverpool, UK, (2016), (Poster) http://www.pvsat.org.uk/proceedings/.

18. N.A. Abdul-Manaf, H.I. Salim, M.L. Madugu, I.M. Dharmadasa, Electrodeposition of CdTe thin films using Chloride precursor for the application in solar cells, in proc. of PVSAT-11, University of Leeds, UK, (2015) 137-140 (Poster).

#### **Submitted Articles for Publication**

19. I.M. Dharmadasa, M.L. Madugu, O.I. Olusola, O.K. Echendu, F. Fauzi, D.G. Diso, A.R. Weerasinghe, T. Druffel, R. Dharmadasa, B. Lavery, J.B. Jasinski, T.A. Krentsel, G. Sumanasekera, Electroplating of CdTe Thin Films from Cadmium Sulphate Precursor and Comparison of layers grown by 3-electrode and 2-electrode systems, Submitt. to Coatings. (2016).

#### **Abstract**

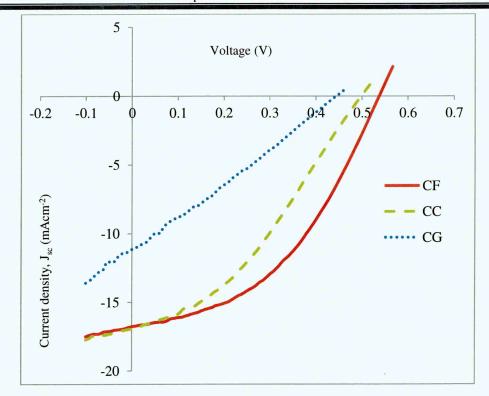

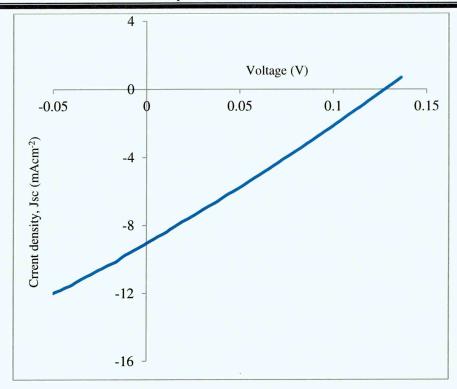

The global need for a clean, sustainable and affordable source of energy has triggered extensive research especially in renewable energy sources. In this sector, photovoltaic has been identified as a cheapest, clean and reliable source of energy. It would be of interest to obtain photovoltaic material in thin film form by using simple and inexpensive semiconductor growth technique such as electroplating. Using this growth technique, four semiconductor materials were electroplated on glass/fluorine-doped tin oxide (FTO) substrate from aqueous electrolytes. These semiconductors are indium selenide (In<sub>x</sub>Se<sub>y</sub>), zinc sulphide (ZnS), cadmium sulphide (CdS) and cadmium telluride (CdTe). In<sub>x</sub>Se<sub>v</sub> and ZnS were incorporated as buffer layers while CdS and CdTe layers were utilised as window and absorber layers respectively. All materials were grown using two-electrode (2E) system except for CdTe which was grown using 3E and 2E systems for comparison. To fully optimise the growth conditions, the as-deposited and annealed layers from all the materials were characterised for their structural, morphological, optical, electrical and defects structures using X-ray diffraction (XRD), Raman spectroscopy, scanning electron microscopy (SEM), atomic force microscopy (AFM), optical absorption (UV-Vis spectroscopy), photoelectrochemical (PEC) cell measurements, current-voltage (I-V), capacitance-voltage (C-V), DC electrical measurements, ultraviolet photoelectron spectroscopy (UPS) and photoluminescence (PL) techniques. Results show that In<sub>x</sub>Se<sub>y</sub> and ZnS layers were amorphous in nature and exhibit both n-type and p-type in electrical conduction. CdS layers are n-type in electrical conduction and show hexagonal and cubic phases in both the as-deposited and after annealing process. CdTe layers show cubic phase structure with both n-type and ptype in electrical conduction. CdTe-based solar cell structures with a n-n heterojunction plus large Schottky barrier, as well as multi-layer graded bandgap solar cells were fabricated. This means that the solar cells investigated in this thesis were not the conventional p-n junction type solar cells. The conventional cadmium chloride (CdCl<sub>2</sub> or CC) treatment was applied to the structures to produce high performance devices; however, by modifying the treatment to include cadmium chloride and cadmium fluoride (CdCl<sub>2</sub>+CdF<sub>2</sub> or CF) device performance could be improved further. The fabricated devices were characterised using I-V and C-V measurement techniques. The highest cell efficiency achieved in this research was ~10\%, with an open circuit voltage of 640 mV, short-circuit current density of 38.1 mAcm<sup>-2</sup>, fill factor of 0.41 and doping concentration of 2.07×10<sup>16</sup> cm<sup>-3</sup>. These parameters were obtained for the glass/FTO/n-In<sub>x</sub>Se<sub>y</sub>/n-CdS/n-CdTe/Au solar cell structure.

# **Table of Contents**

| Declaration                                      |

|--------------------------------------------------|

| Dedicationii                                     |

| Acknowledgementiii                               |

| List of publicationsv                            |

| Abstractviii                                     |

| Table of Contentsix                              |

| List of Figuresxvi                               |

| List of Tablesxxv                                |

| Abbreviations and Symbolsxxvii                   |

| Chapter 1: Introduction 1                        |

| 1.1 Global need for renewable energy             |

| 1.2 Non-renewable energy sources                 |

| 1.3 Alternative renewable energy sources         |

| 1.3.1 Wind energy4                               |

| 1.3.2 Biomass                                    |

| 1.3.3 Hydroelectricity6                          |

| 1.3.4 Solar energy7                              |

| 1.3.4.1 The solar spectrum                       |

| 1.3.4.2 Solar thermal                            |

| 1.3.4.3 Solar Photovoltaics                      |

| 1.4 Aims and objectives of the research          |

| 1.5 Conclusions                                  |

| References                                       |

| Chapter 2: Solar energy devices and interfaces20 |

| 2.1 Introduction                                 |

| 2.2            | Silicon solar cells                                                                                                                                                                                                                                                                      | . 21                                                         |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 2.3            | Thin film solar cells                                                                                                                                                                                                                                                                    | . 23                                                         |

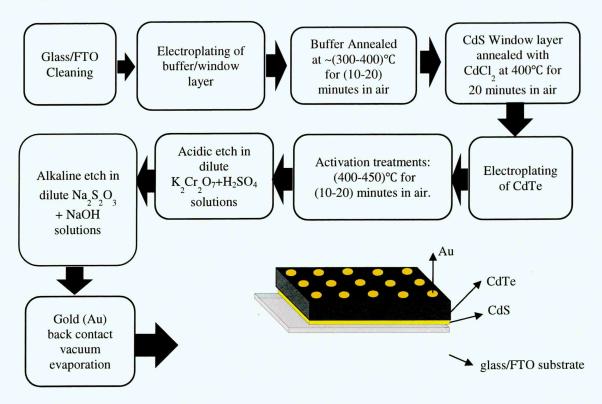

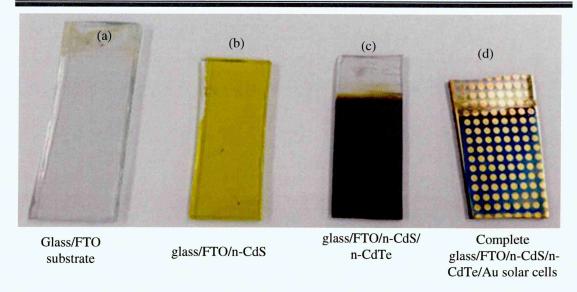

|                | 2.3.1 CdS/CdTe solar cells                                                                                                                                                                                                                                                               | . 23                                                         |

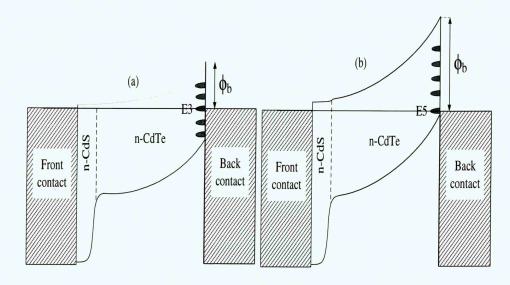

|                | 2.3.2 New model on CdS/CdTe solar cell structure                                                                                                                                                                                                                                         | . 27                                                         |

| 2.4            | Semiconductor junctions and interfaces                                                                                                                                                                                                                                                   | . 30                                                         |

|                | 2.4.1 P-n junction                                                                                                                                                                                                                                                                       | . 30                                                         |

|                | 2.4.2 p-i-n Junction                                                                                                                                                                                                                                                                     | . 32                                                         |

|                | 2.4.3 Hetero-junction                                                                                                                                                                                                                                                                    | . 32                                                         |

|                | 2.4.4 n-n and p-p Junctions                                                                                                                                                                                                                                                              | . 36                                                         |

|                | 2.4.5 Multi-layer graded bandgap devices                                                                                                                                                                                                                                                 | . 37                                                         |

| 2.5            | Metal-semiconductor contacts                                                                                                                                                                                                                                                             | . 39                                                         |

|                | 2.5.1 Ohmic MS contacts                                                                                                                                                                                                                                                                  | . 39                                                         |

|                | 2.5.2 Rectifying (Schottky) MS contacts                                                                                                                                                                                                                                                  | . 40                                                         |

|                | 2.5.3 Metal-insulator-semiconductor interface                                                                                                                                                                                                                                            | . 42                                                         |

|                |                                                                                                                                                                                                                                                                                          |                                                              |

| Ref            | erence                                                                                                                                                                                                                                                                                   | . 44                                                         |

|                | erence3: Experimental techniques used for growth and characterisation of                                                                                                                                                                                                                 |                                                              |

| Chapter        |                                                                                                                                                                                                                                                                                          |                                                              |

| Chapter<br>mat | 3: Experimental techniques used for growth and characterisation of                                                                                                                                                                                                                       | . 52                                                         |

| Chapter mat    | 3: Experimental techniques used for growth and characterisation of terials and devices                                                                                                                                                                                                   | . <b>52</b>                                                  |

| Chapter mat    | 3: Experimental techniques used for growth and characterisation of serials and devices                                                                                                                                                                                                   | . <b>52</b><br>. 52                                          |

| Chapter mat    | 3: Experimental techniques used for growth and characterisation of terials and devices                                                                                                                                                                                                   | . <b>52</b><br>. 52<br>. 53                                  |

| Chapter mat    | 3: Experimental techniques used for growth and characterisation of serials and devices                                                                                                                                                                                                   | . <b>52</b> . 52 . 53 . 53 . 54                              |

| Chapter mat    | 3: Experimental techniques used for growth and characterisation of terials and devices  Introduction  Thin films growth techniques.  3.2.1 Closed space sublimation  3.2.2 Chemical bath deposition                                                                                      | . 52<br>. 52<br>. 53<br>. 53                                 |

| Chapter mat    | 3: Experimental techniques used for growth and characterisation of terials and devices                                                                                                                                                                                                   | . 52<br>. 52<br>. 53<br>. 53<br>. 54<br>. 55                 |

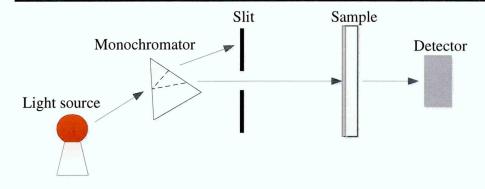

| Chapter mat    | 3: Experimental techniques used for growth and characterisation of terials and devices  Introduction  Thin films growth techniques.  3.2.1 Closed space sublimation  3.2.2 Chemical bath deposition  3.2.3 Electroplating.  Materials characterisation techniques                        | . 52<br>. 52<br>. 53<br>. 53<br>. 54<br>. 55<br>. 59         |

| Chapter mat    | 3: Experimental techniques used for growth and characterisation of terials and devices  Introduction  Thin films growth techniques  3.2.1 Closed space sublimation  3.2.2 Chemical bath deposition  3.2.3 Electroplating  Materials characterisation techniques  3.3.1 X-ray diffraction | . 52<br>. 52<br>. 53<br>. 54<br>. 55<br>. 59                 |

| Chapter mat    | 3: Experimental techniques used for growth and characterisation of terials and devices                                                                                                                                                                                                   | . 52<br>. 52<br>. 53<br>. 54<br>. 55<br>. 59<br>. 61<br>. 63 |

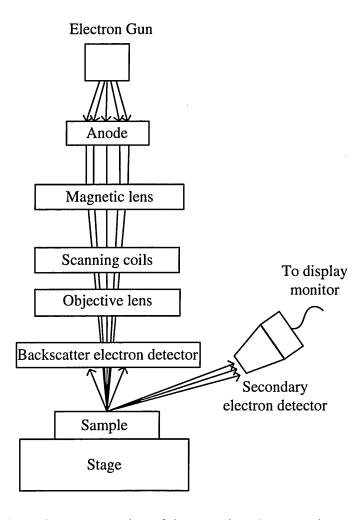

| 3.3.5 Scanning electron microscopy                                               | 66  |

|----------------------------------------------------------------------------------|-----|

| 3.3.6 Optical absorption measurement                                             | 68  |

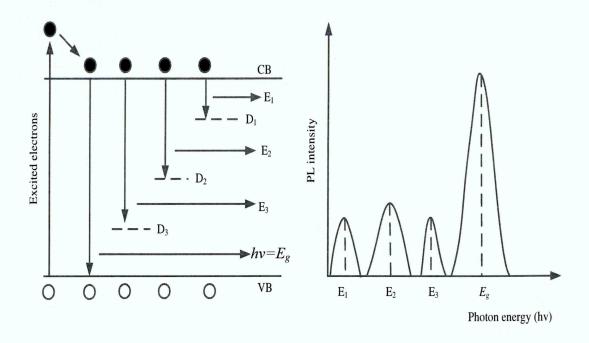

| 3.3.7 Photoluminescence spectroscopy                                             | 70  |

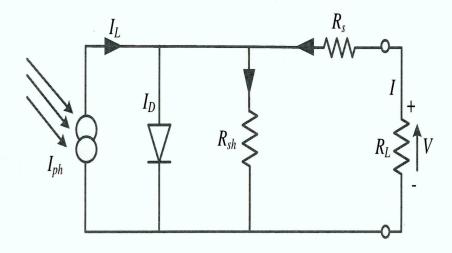

| 3.4 Device characterisation techniques                                           | 71  |

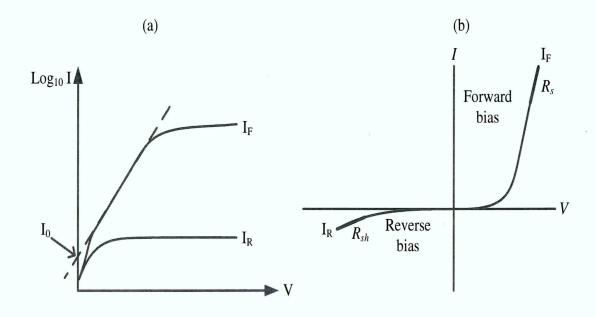

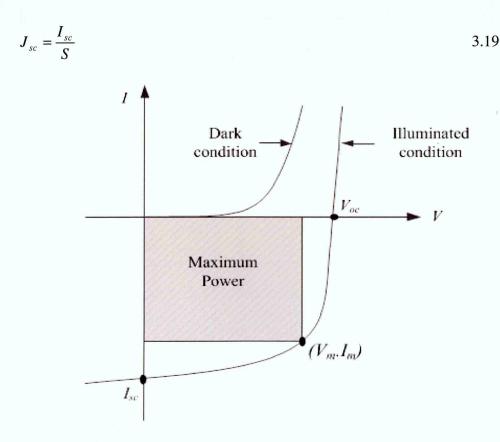

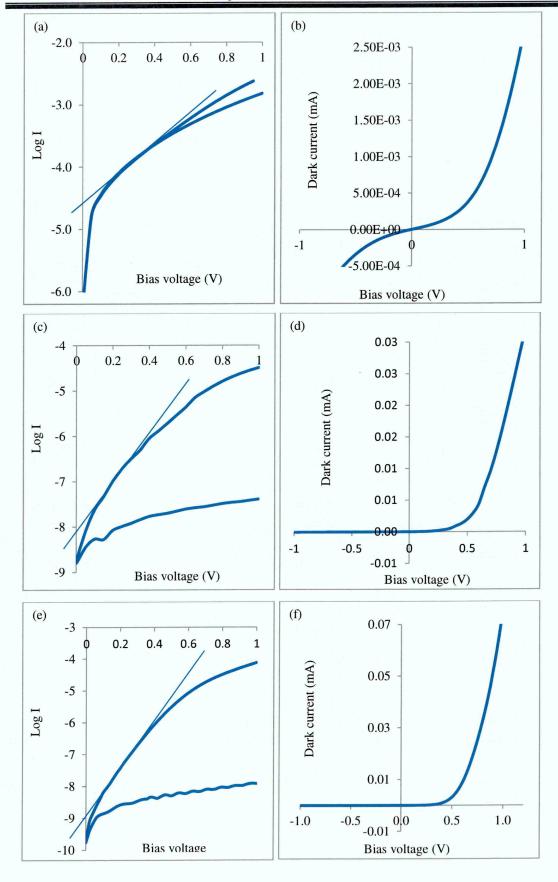

| 3.4.1 Current-voltage (I-V) characterisation                                     | 71  |

| 3.4.2 Device characterisation under dark condition                               | 72  |

| 3.4.3 Current-voltage (I-V) under illumination                                   | 75  |

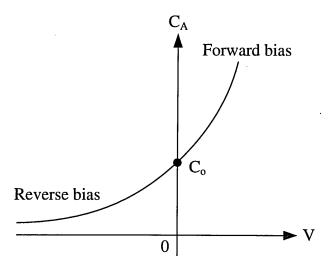

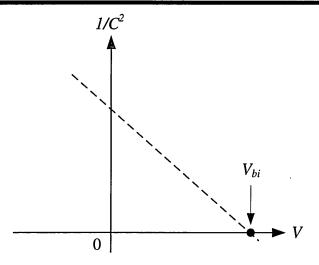

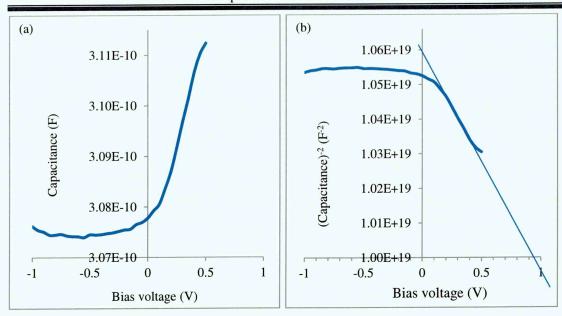

| 3.5 Capacitance-voltage (C-V) measurement                                        | 78  |

| 3.6 Conclusions                                                                  | 80  |

| Reference                                                                        | 82  |

| Chapter 4: Growth and characterisation of In <sub>x</sub> Se <sub>y</sub> layers | 89  |

| 4.1 Introduction                                                                 | 89  |

| 4.2 Preparation of In <sub>x</sub> Se <sub>y</sub> deposition electrolyte        | 90  |

| 4.3 Results and discussion                                                       | 90  |

| 4.3.1 Cyclic voltammetry                                                         | 90  |

| 4.3.2 X-ray diffraction                                                          | 92  |

| 4.3.3 Optical studies                                                            | 93  |

| 4.3.3.1 Effect of growth voltage on the optical bandgap of In,                   | •   |

| layers                                                                           | 93  |

| 4.3.4 Variation of thickness with growth time for $In_xSe_y$ layers              | 95  |

| 4.3.5 Morphological studies                                                      | 96  |

| 4.3.5.1 Scanning electron microscopy                                             | 96  |

| 4.3.5.2 Atomic Force Microscopy                                                  | 98  |

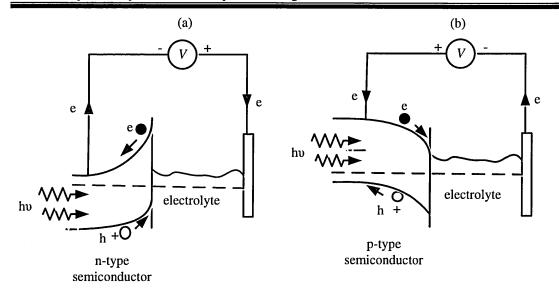

| 4.3.6 Photoelectrochemical cell measurement                                      | 99  |

| 4.4 Conclusions                                                                  | 100 |

| Reference                                                                        | 101 |

| Chapter 5: Growth and characterisation of ZnS buffer layers104                       |

|--------------------------------------------------------------------------------------|

| 5.1 Introduction                                                                     |

| 5.2 Preparation of deposition electrolyte                                            |

| 5.3 Substrate preparation                                                            |

| 5.4 Experimental procedure                                                           |

| 5.4.1 Cyclic voltammetry                                                             |

| 5.4.2 X-ray Diffraction                                                              |

| 5.4.3 Photoelectrochemical Cell studies                                              |

| 5.4.4 Raman spectroscopy                                                             |

| 5.4.5 Optical properties                                                             |

| 5.4.5.1 Effects of growth voltage on the optical properties of ZnS layers            |

| 5.4.5.2 Effects of growth temperature on the optical properties of ZnS thin films    |

| 5.4.5.3 Effects of annealing temperature on the optical properties of ZnS thin films |

| 5.4.6 Morphological studies                                                          |

| 5.4.6.1 Effects of annealing temperature on the morphology of ZnS thin films         |

| 5.4.6.2 Effects of growth temperature on the surface morphology of ZnS thin films    |

| 5.4.7 Atomic Force Microscopy Studies                                                |

| 5.4.8 Variation of thickness with growth time for ZnS layers120                      |

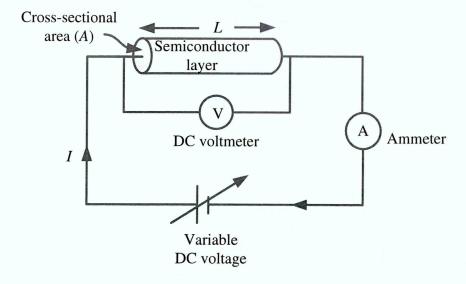

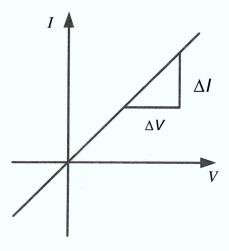

| 5.4.9 DC electrical resistivity studies                                              |

| 5.5 Conclusion                                                                       |

| Reference                                                                            |

| Chapter 6: Growth and characterisation of CdS window layers 128                      |

| 6.1 Introduction                                                                     |

| 6.2 Preparation of CdS electroplating electrolyte                                                 |

|---------------------------------------------------------------------------------------------------|

| 6.3 Result and discussion                                                                         |

| 6.3.1 Cyclic voltammetry                                                                          |

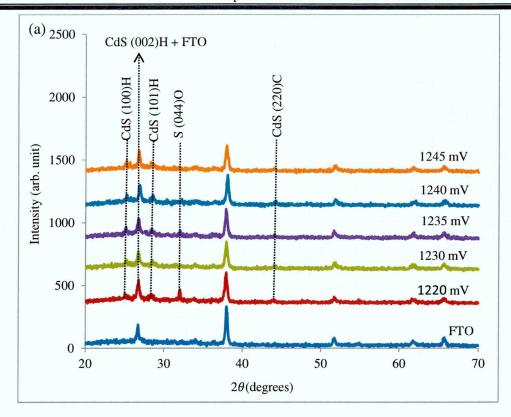

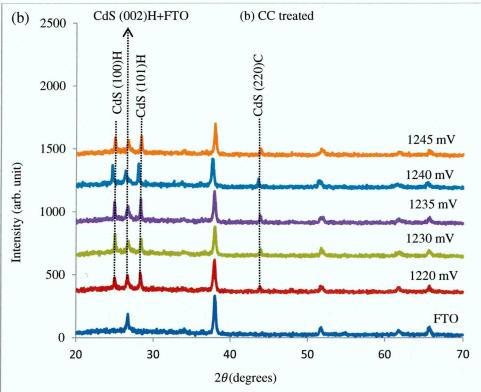

| 6.3.2 X-ray diffraction                                                                           |

| 6.3.3 Optical studies                                                                             |

| 6.3.4 Scanning electron microscopy                                                                |

| 6.3.5 Photoelectrochemical cell measurements                                                      |

| 6.4 Conclusion                                                                                    |

| Reference141                                                                                      |

| Chapter 7: Electroplating and Characterisation of CdTe Absorber Material 144                      |

| 7.1 Introduction 144                                                                              |

| 7.2 Preparation of deposition electrolyte                                                         |

| 7.3 Results and discussion                                                                        |

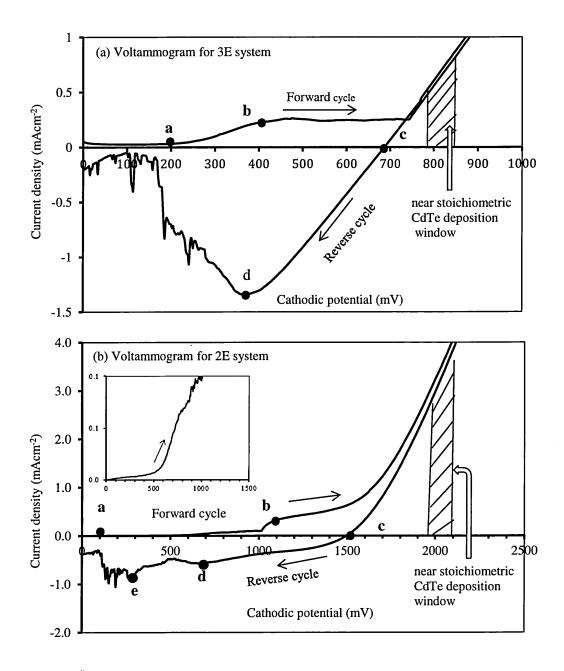

| 7.3.1 Cyclic voltammetry for 3E and 2E systems                                                    |

| 7.3.2 Characterisation of CdTe thin films grown using 3E and 2E                                   |

| systems                                                                                           |

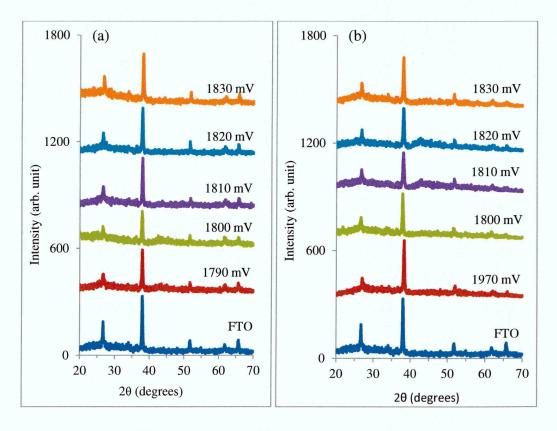

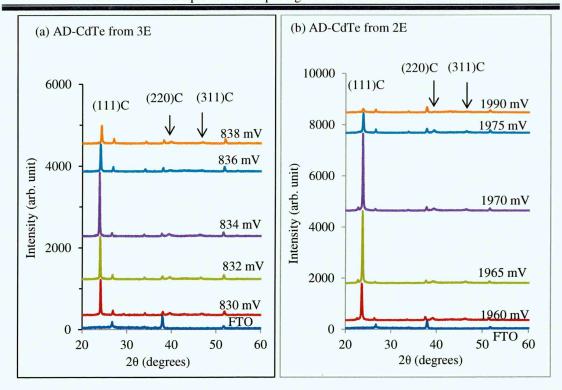

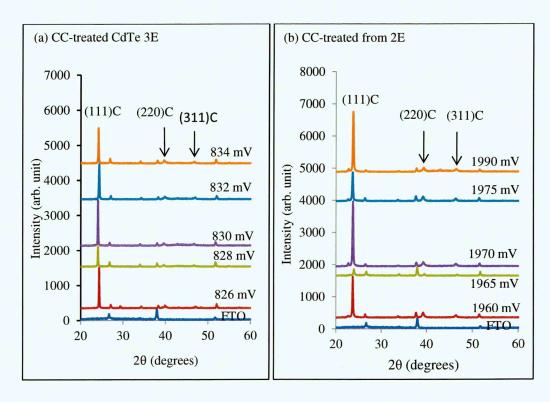

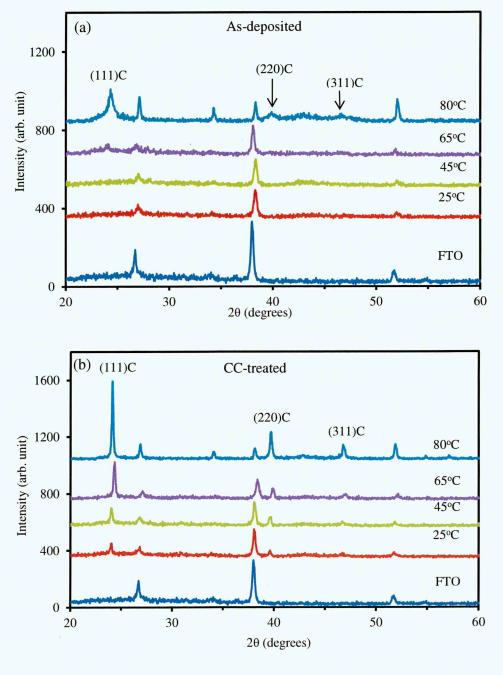

| 7.3.2.1 X-ray diffraction                                                                         |

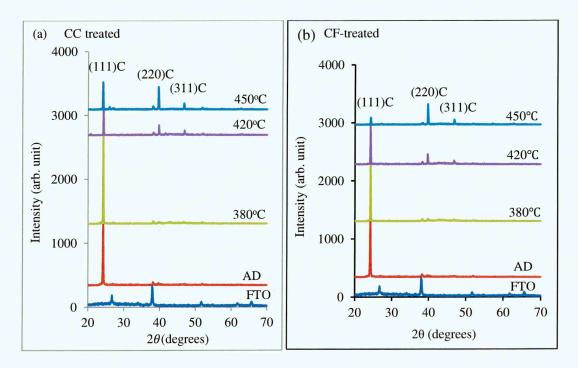

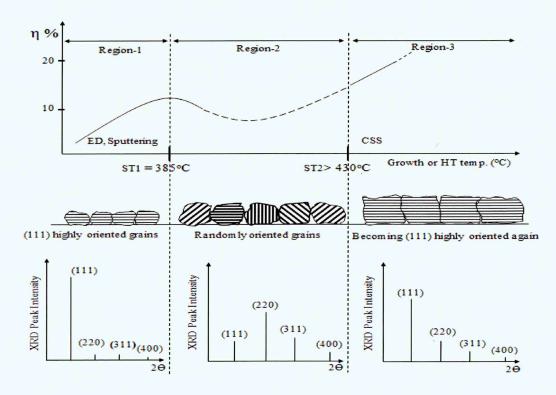

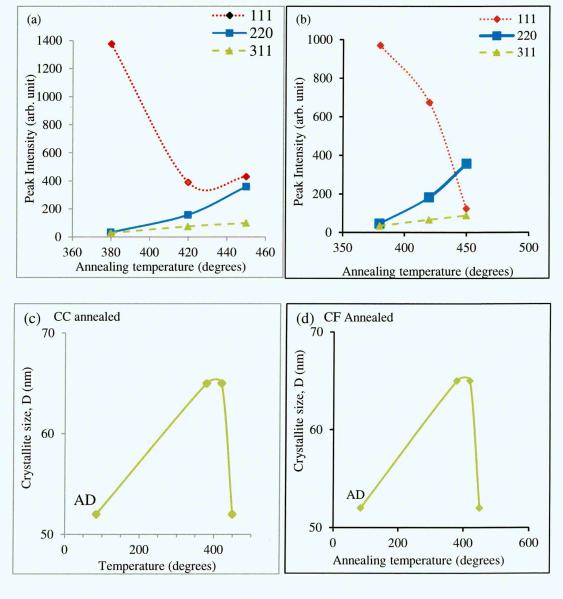

| 7.3.2.2 Effect of CdCl <sub>2</sub> and CdCl <sub>2</sub> +CdF <sub>2</sub> treatments on the XRD |

| pattern of CdTe thin films at different temperatures grown                                        |

| using 2E system151                                                                                |

| 7.3.2.3 Effects of growth temperature on XRD patterns of CdTe                                     |

| thin films grown using 2E system155                                                               |

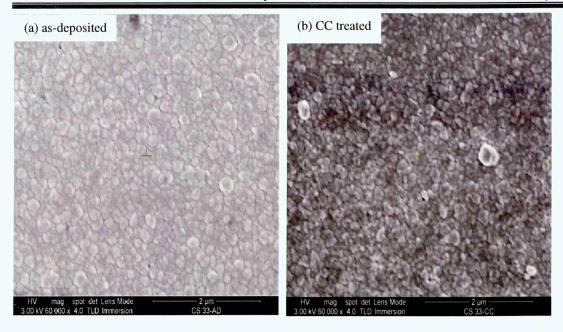

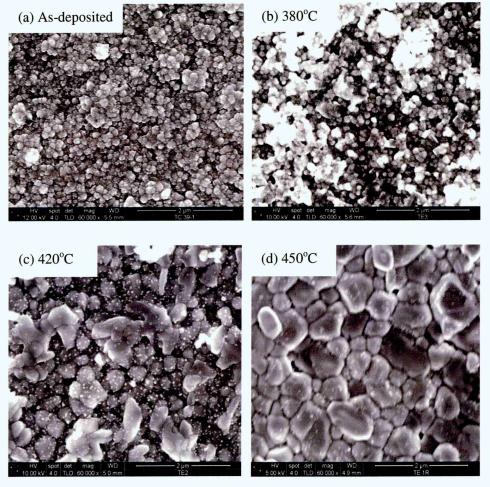

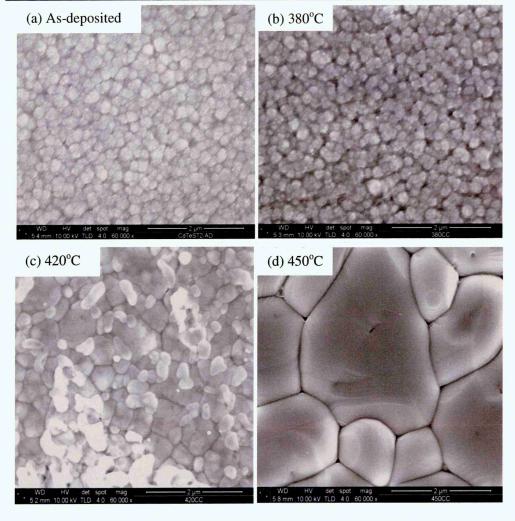

| 7.3.2.4 Morphology of CdTe layers grown using 3E system 157                                       |

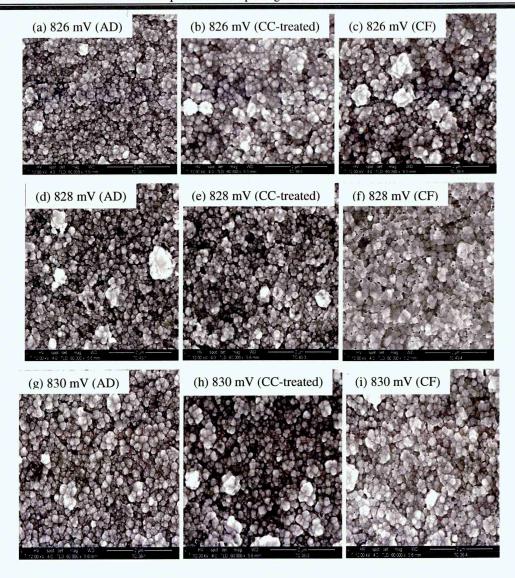

| 7.3.2.5 Effect of CdCl <sub>2</sub> and CdCl <sub>2</sub> +CdF <sub>2</sub> on the surface        |

| morphology of CdTe thin films grown using 3E system                                               |

| and annealed at different temperatures158                                                         |

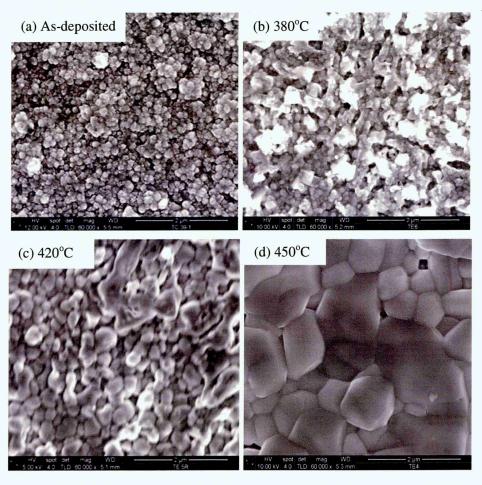

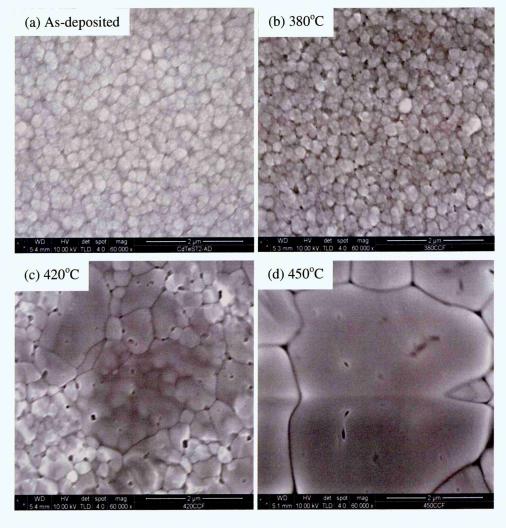

| 7.3.2.6 Effect of CdCl <sub>2</sub> and CdCl <sub>2</sub> +CdF <sub>2</sub> on the morphology of  |

| CdTe thin films grown using 2E system and annealed at                                             |

| different temperatures161                                                                         |

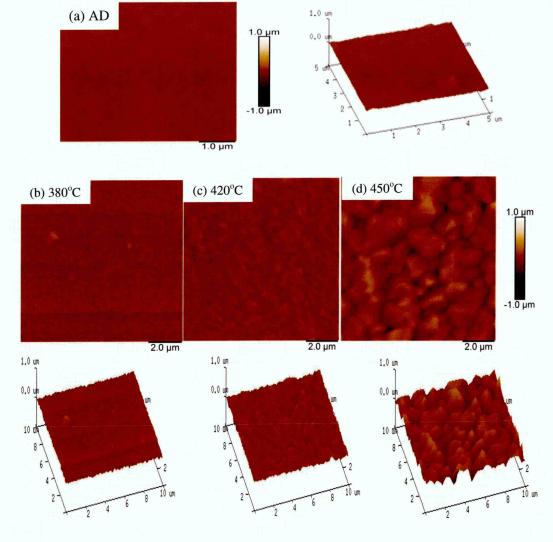

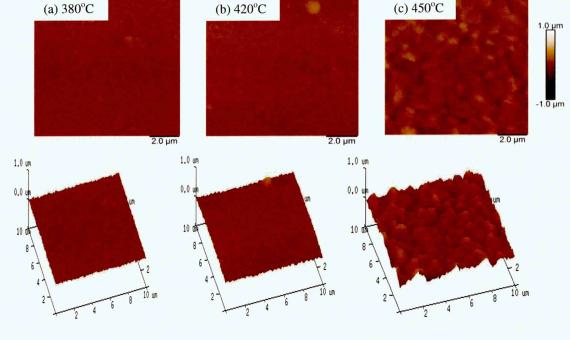

| 7.3.2.7 Atomic Force Microscopy                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.3.2.8 Effect of growth time on the CdTe layer thickness 16                                                                                     |

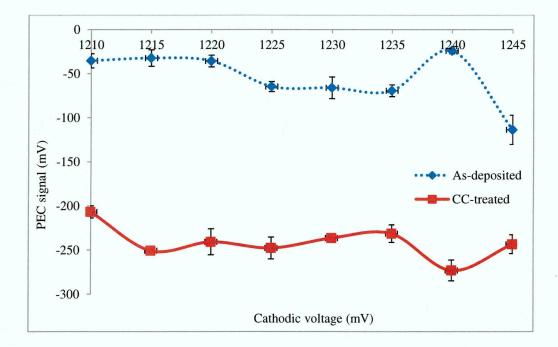

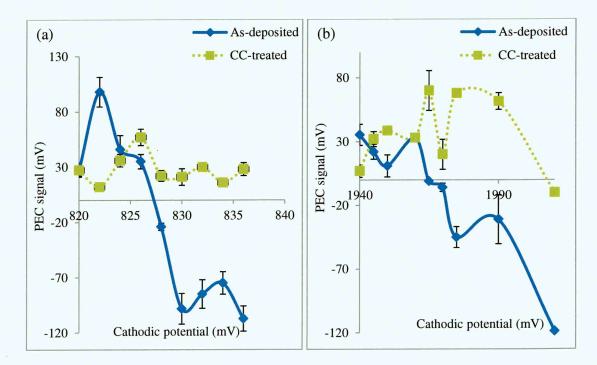

| 7.3.2.9 Photoelectrochemical cell measurements                                                                                                   |

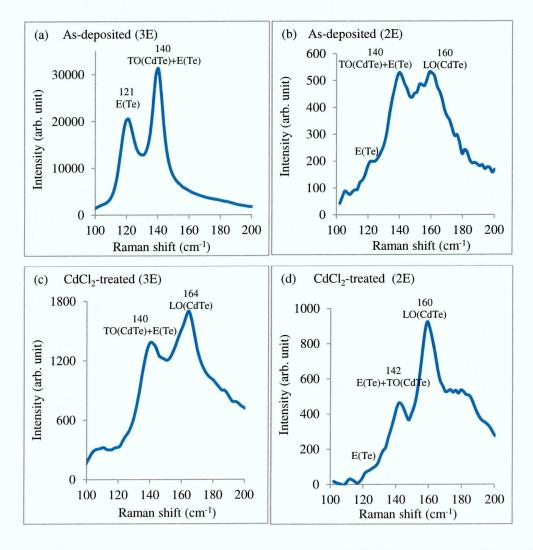

| 7.3.2.10 Raman spectroscopy                                                                                                                      |

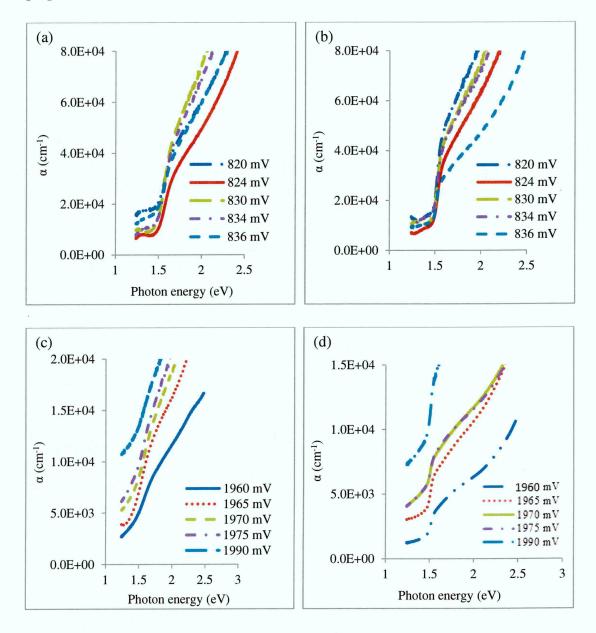

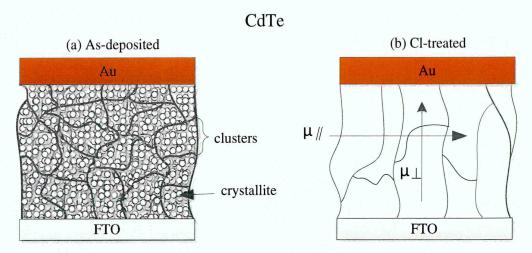

| 7.3.2.11 Optical absorption studies                                                                                                              |

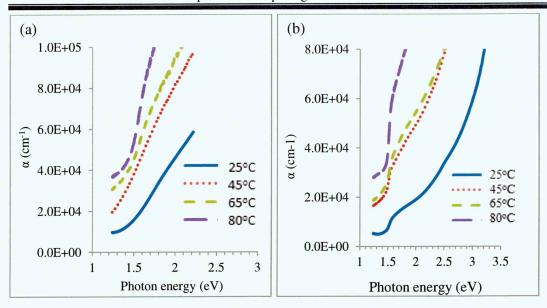

| 7.3.3 Effect of growth temperature on the optical bandgap of CdTe                                                                                |

| thin films grown using 2E system                                                                                                                 |

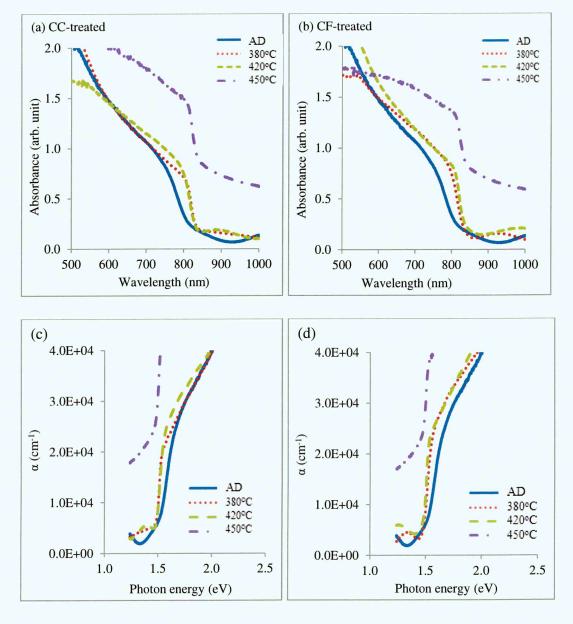

| 7.3.4 Effect of annealing temperature on the optical properties of CdCl <sub>2</sub> and CdCl <sub>2</sub> +CdF <sub>2</sub> treated CdTe layers |

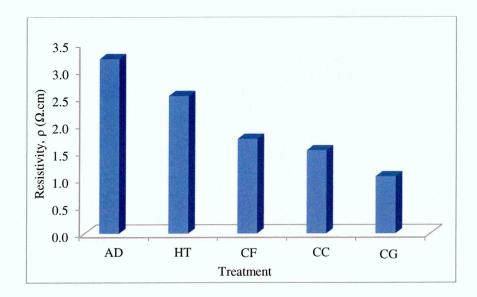

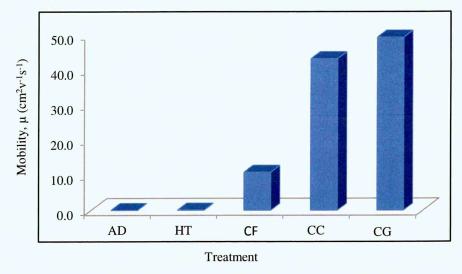

| 7.4 DC electrical conductivity measurements                                                                                                      |

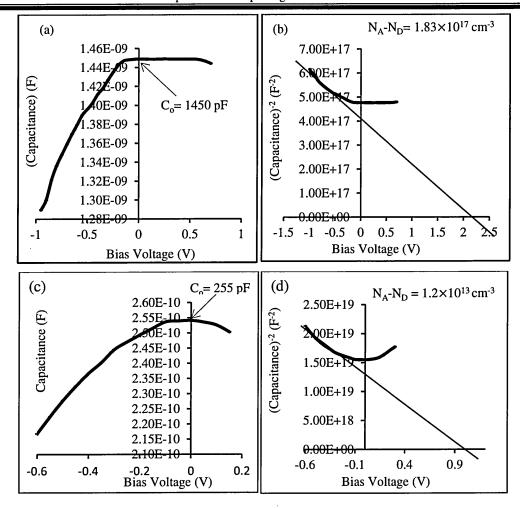

| 7.5 C-V measurements of Schottky contacts                                                                                                        |

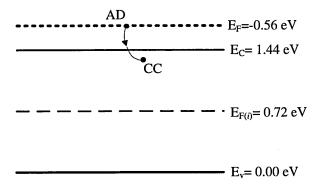

| 7.6 Ultraviolet photoelectron spectroscopy                                                                                                       |

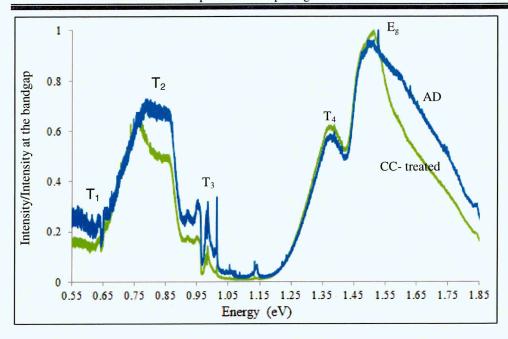

| 7.7 Photoluminescence (PL) studies                                                                                                               |

| 7.8 Conclusions                                                                                                                                  |

| 100                                                                                                                                              |

| References                                                                                                                                       |

|                                                                                                                                                  |

| References                                                                                                                                       |

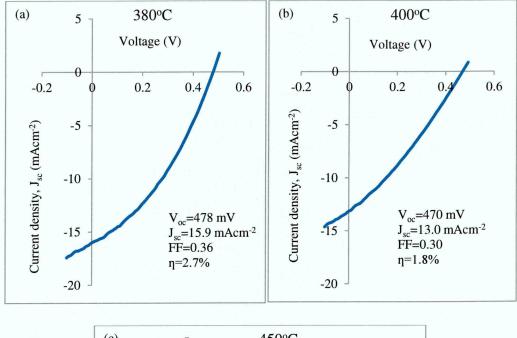

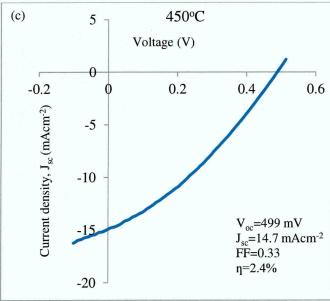

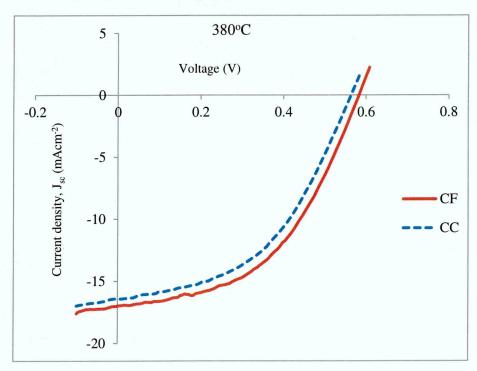

|      | 8.7~C-V measurements of glass/n-In <sub>x</sub> Se <sub>y</sub> /n-CdS/n-CdTe/Au solar cells under the s | r   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | dark condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 223 |

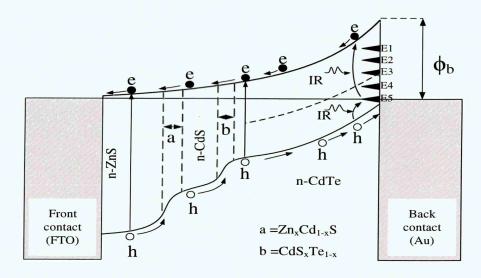

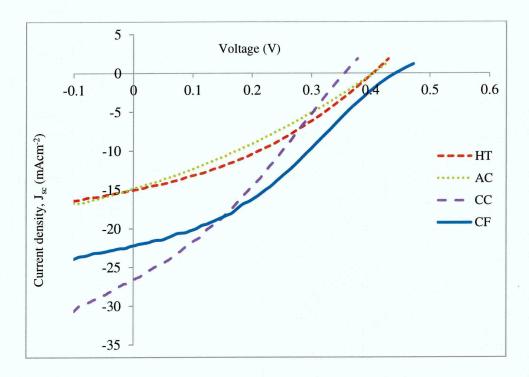

|      | 8.8 Fabrication of glass/FTO/n-ZnS/n-CdS/n-CdTe/Au multi-layer graded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | bandgap solar cell devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 225 |

|      | 8.9 Possible reasons for the observed high short-circuit current density $(J_{\text{sc}})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|      | values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 228 |

|      | 8.10 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 230 |

|      | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 232 |

| Chap | oter 9: Conclusions and future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 239 |

|      | 9.1 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 239 |

|      | 9.2 Future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 240 |

|      | 9.2.1 Purity of starting materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 240 |

|      | 9.2.2 Electrolyte replenishment using $Cd^{2+}$ and $HTeO_2^+$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 241 |

|      | 9.2.3 Front contact                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 242 |

|      | 9.3 Multi-layer Graded bandgap device structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 242 |

# **List of Figures**

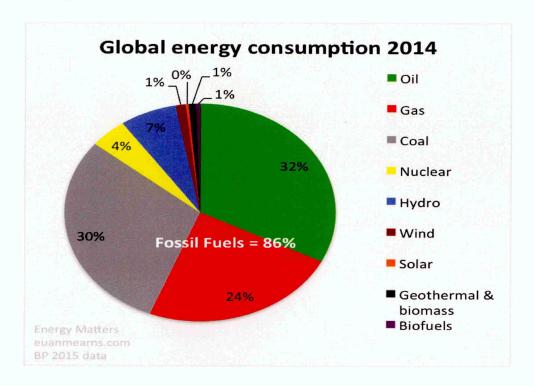

| Figure 1-1: BP Statistical Review of World Energy consumption 2014 [3]2                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

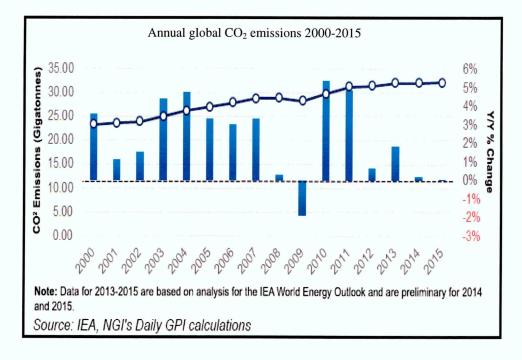

| Figure 1-2: Annual Global CO <sub>2</sub> Emission 2000-2015 [5]                                                                                                                   |

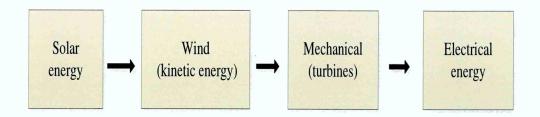

| Figure 1-3: Main stages of the electrical energy generation from wind energy [9]5                                                                                                  |

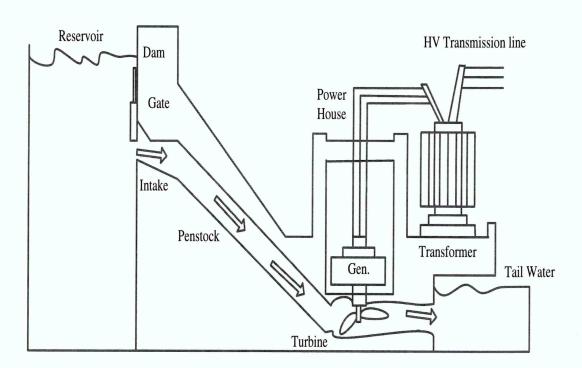

| Figure 1-4: Schematic diagram of hydroelectric power plant [Redrawn from [14]]6                                                                                                    |

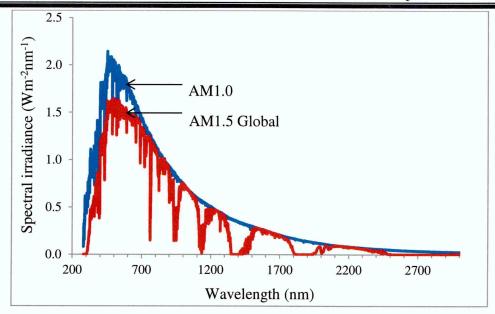

| Figure 1-5: The approximate solar radiation spectrum [22]                                                                                                                          |

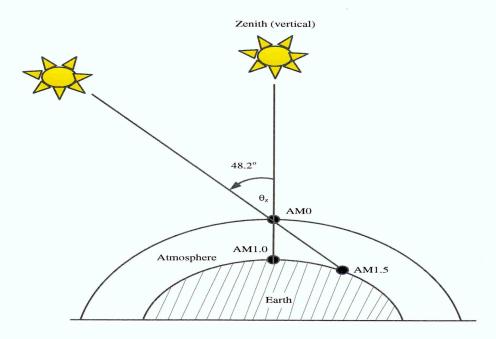

| Figure 1-6: Path length of the sunlight through the atmosphere [Redrawn from ref [24]]9                                                                                            |

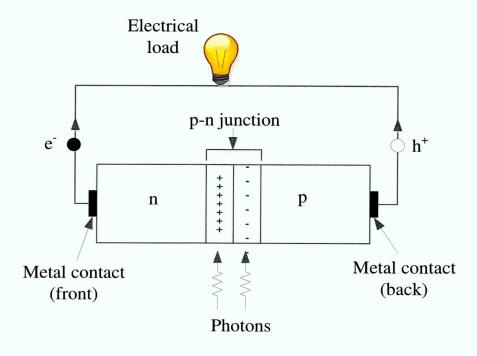

| Figure 1-7: p-n juction solar cell showing the absorption of photons, creation of electron-hole pairs, separation and transport them to external circuit to produce useful energy. |

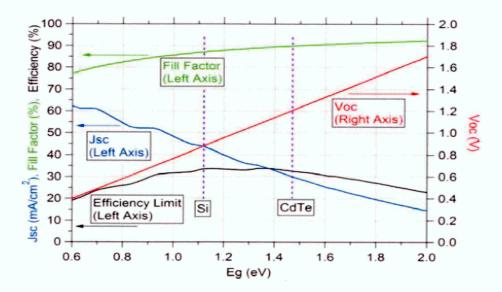

| Figure 1-8: Ideal values for <i>Voc, Jsc, FF</i> and efficiency with changes in bandgap under standard test conditions [adapted from ref.[34]]                                     |

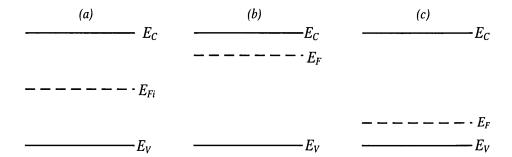

| Figure 2-1: Energy level diagrams showing different conductivity types of (a) pure (intrinsic), (b) n-type and (c) p-type semiconductors20                                         |

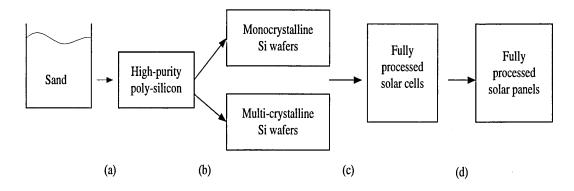

| Figure 2-2: Industrial production lines required for manufacturing panels based on crystalline and polycrystalline Si [Redrawn from [2]]                                           |

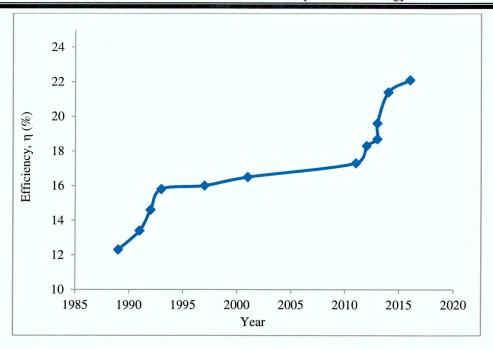

| Figure 2-3: Plot of efficiency vs. year for the evolution of the CdS/CdTe solar cell efficiency                                                                                    |

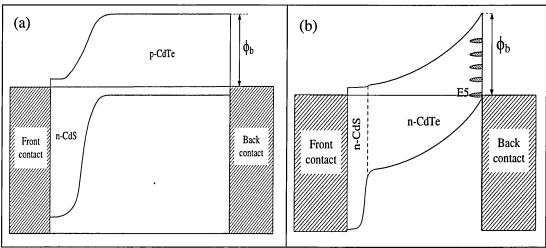

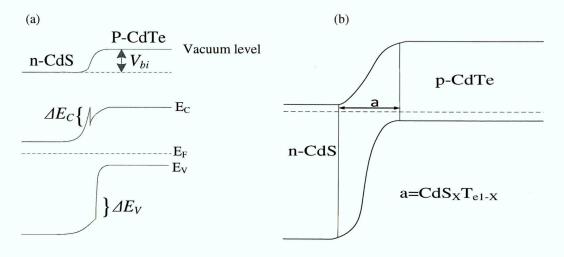

| Figure 2-4: Two possible CdS/CdTe device structures based on (a) p-n junction and (b) n-n+Schottky barrier at the back metal contact                                               |

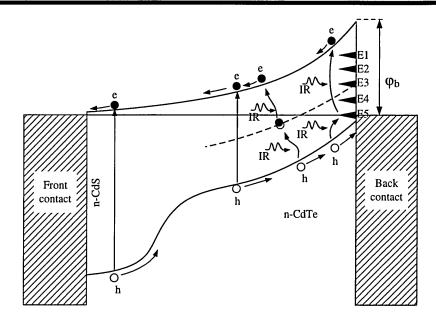

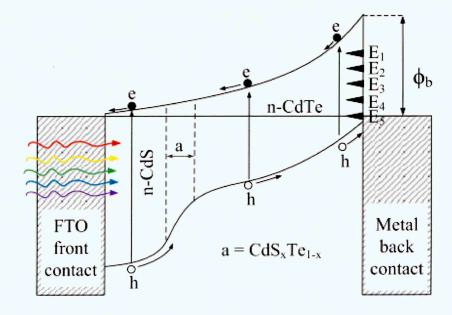

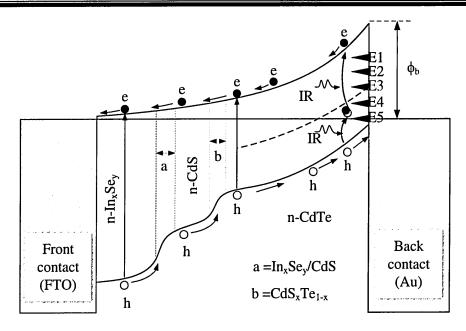

| Figure 2-5: The energy band diagram of CdS/CdTe based on the new model of n-n+large Schottky barrier with strong Fermi level pinning at the metal/n-CdTe interface.                |

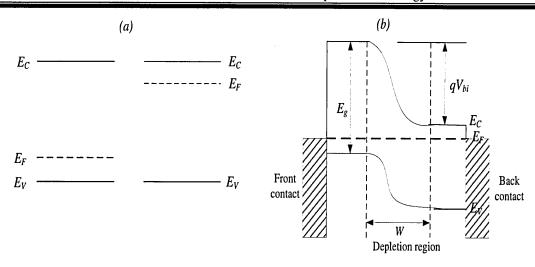

| Figure 2-6: Energy band diagram for the formation of p-n junction (a) before junction formation and (b) after junction formation                                                   |

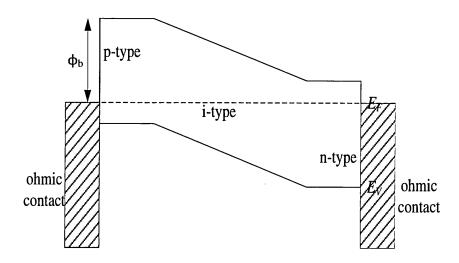

| Figure 2-7: Energy band diagram of p-i-n junction device [Redrawn from ref.[2]]32                                                                                                  |

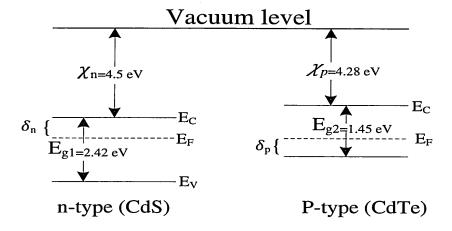

| Figure 2-8: Energy band diagram of <i>n</i> -CdS and <i>p</i> -CdTe before junction formation                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| [diagram redrawn from [50]]34                                                                                                                         |

| Figure 2-9: Energy band diagram of n-CdS/P-CdTe for (a) not activated and (b)  Cl activated junction                                                  |

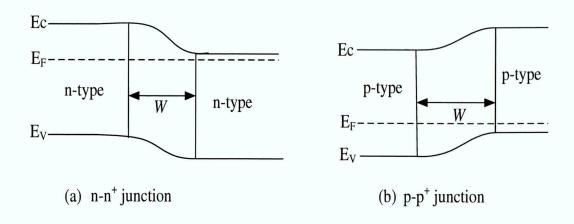

| Figure 2-10: Hetero-junction interfaces based on n-n <sup>+</sup> and p-p <sup>+</sup> junctions with small steps potential barriers.                 |

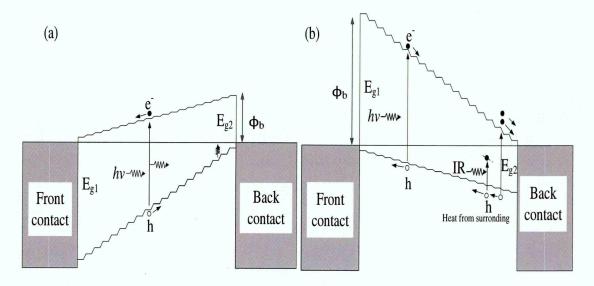

| Figure 2-11: Energy band diagrams of multi-layer graded bandgap solar cell with  (a) n-type window and (b) p-type window layers                       |

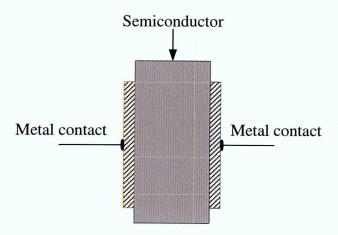

| Figure 2-12: Schematic of semiconductor device showing two metal contacts semiconductor device structure                                              |

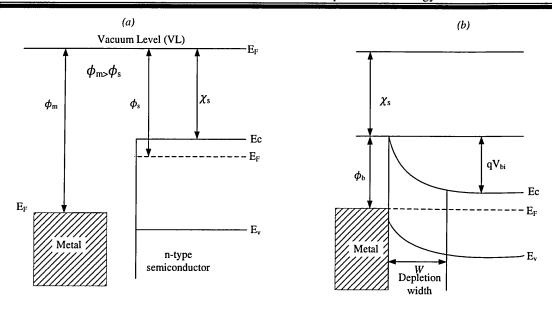

| Figure 2-13: Energy band diagram showing the formation of potential barrier at metal/n-type semiconductor interface                                   |

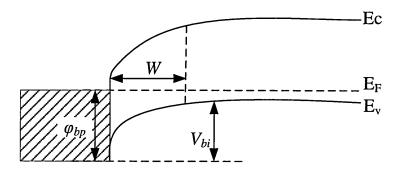

| Figure 2-14: Rectifying (Schottky) contact formed between a metal and a p-type semiconductor                                                          |

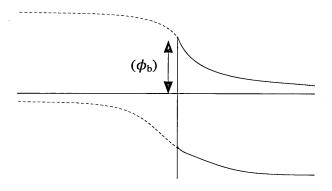

| Figure 2-15: Schematic diagram showing that Schottky barrier is only a half of a p-n junction for an ideal interface                                  |

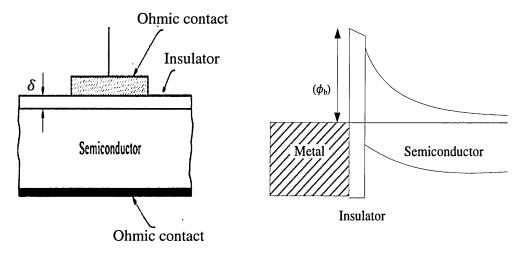

| Figure 2-16: Schematic diagram of MIS structure incorporating an insulating layer between a metal and semiconductor to increase the potential barrier |

| height43                                                                                                                                              |

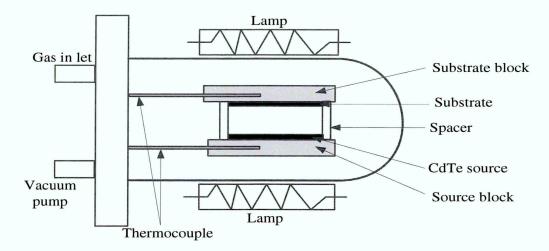

| Figure 3-1: Schematic diagram of CSS deposition system. Redrawn from [8]53                                                                            |

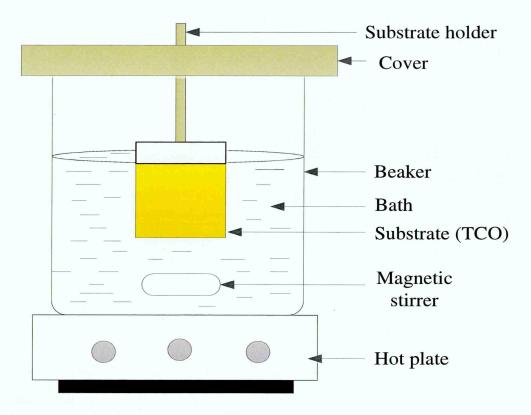

| Figure 3-2: Schematic diagram of chemical bath deposition (CBD) set-up55                                                                              |

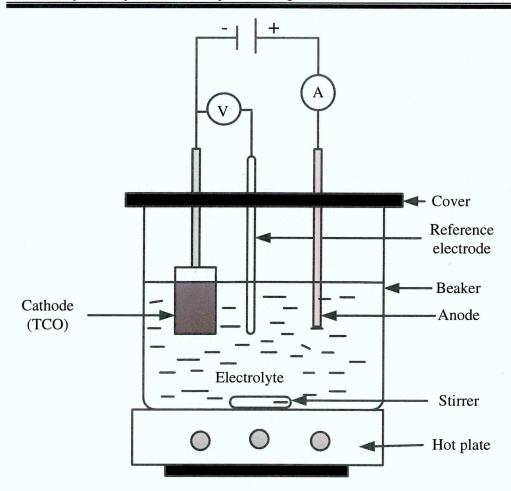

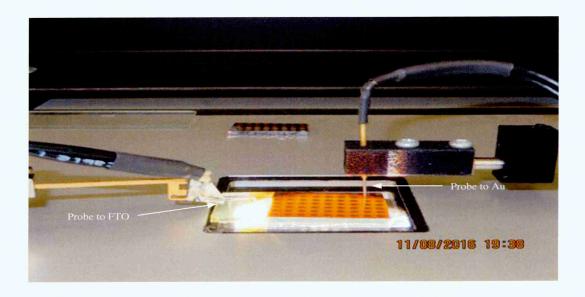

| Figure 3-3: Three-electrode (3E) electroplating system set-up                                                                                         |

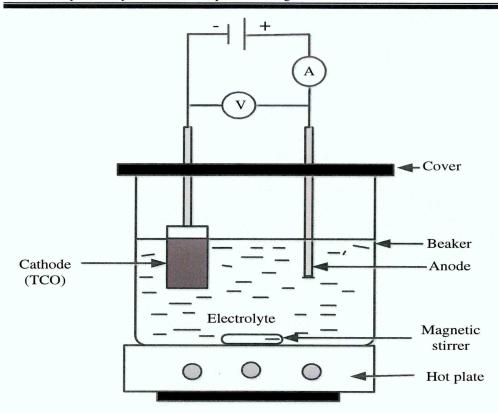

| Figure 3-4: Two- electrode (2E) electroplating system set-up                                                                                          |

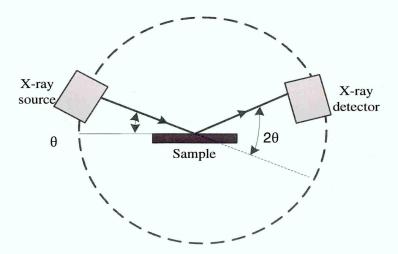

| Figure 3-5: X-ray diffraction set-up to determine the structural properties of layers.                                                                |

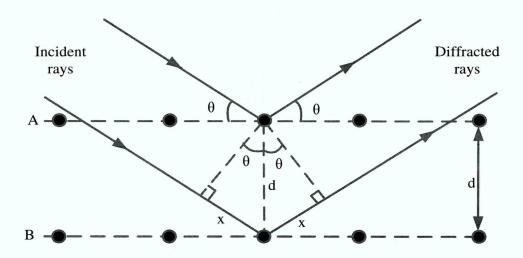

| Figure 3-6: The principle of X-ray diffraction showing the reflection from two atomic planes in a crystal lattice                                     |

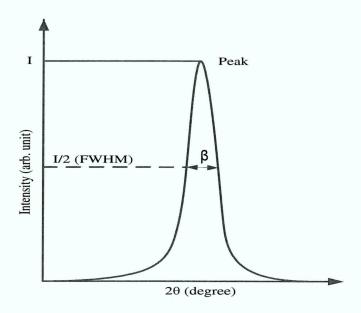

| Figure 3-7: Typical XRD peak showing full width at half maximum (FWHM)61                                                                              |

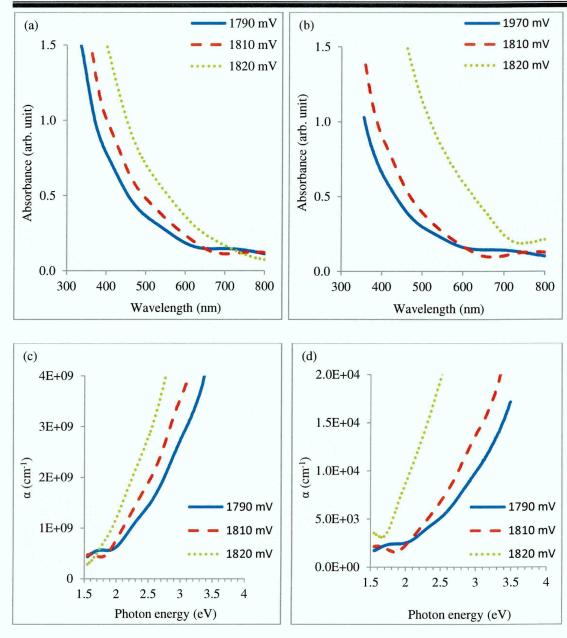

| Figure 4-3: Optical absorbance spectra (A vs $\lambda$ ) for (a) as-deposited and (b) annealed $In_xSe_y$ layers while (c) and (d) are their corresponding $\alpha$ vs hv graphs. Annealing was carried out at 300°C for 10 minutes in air94                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

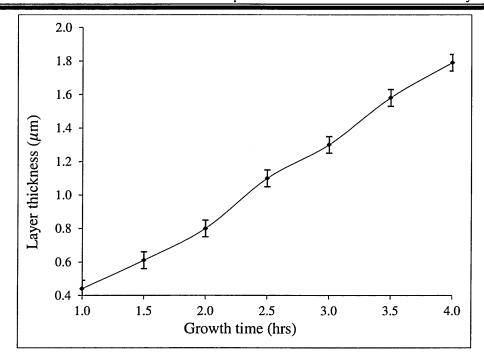

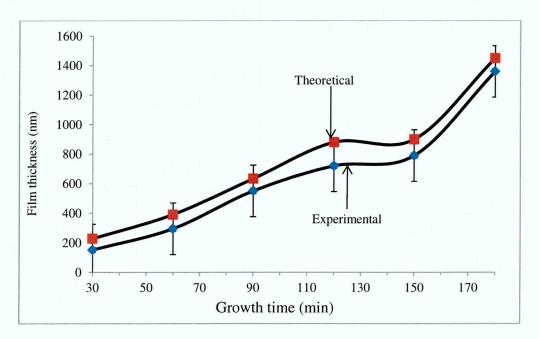

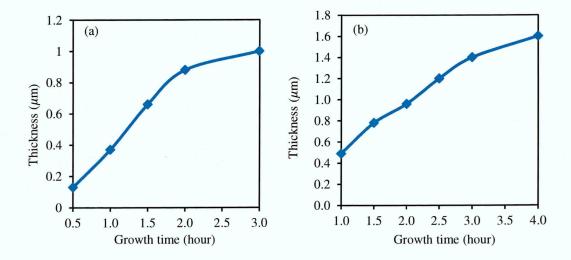

| Figure 4-4: Plot of experimentally measured thicknesses vs. growth time for as-<br>deposited In <sub>x</sub> Se <sub>y</sub> layers. All other parameters; growth voltage, growth<br>temperature and pH were kept constant                                           |

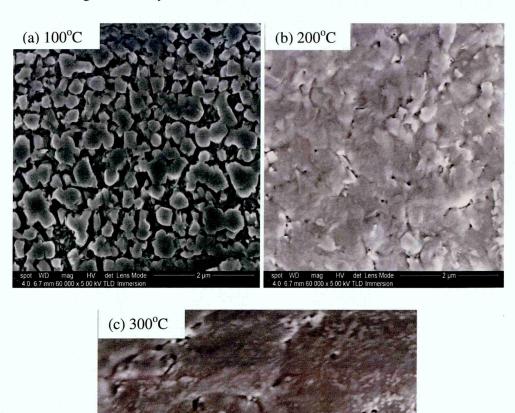

| Figure 4-5: SEM images of In <sub>x</sub> Se <sub>y</sub> layers annealed at (a) 100°C, (b) 200°C and (c) 300°C, for 10 minutes in air.                                                                                                                              |

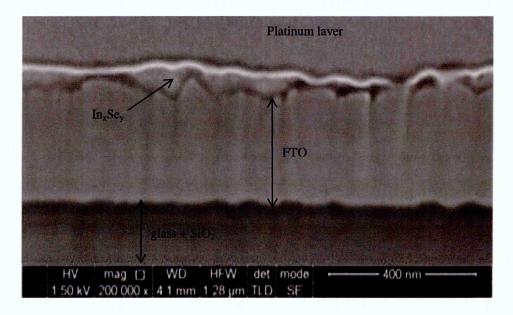

| Figure 4-6: A typical SEM cross-section image of a glass/FTO/In <sub>x</sub> Se <sub>y</sub> structure indicating smoothening effect on the FTO rough surface                                                                                                        |

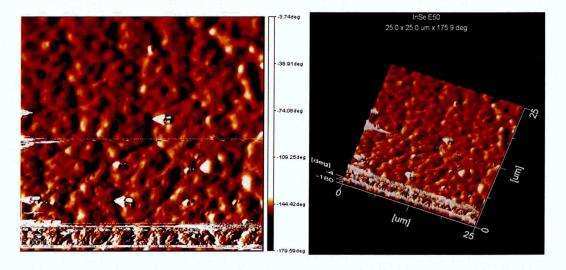

| Figure 4-7: 2D AFM images of annealed In <sub>x</sub> Se <sub>y</sub> layer grown for 60 minutes and annealed at 300°C for 10 minutes in air                                                                                                                         |

| Figure 4-8: PEC signal vs. growth voltage for In <sub>x</sub> Se <sub>y</sub> layers grown at different growth voltages.                                                                                                                                             |

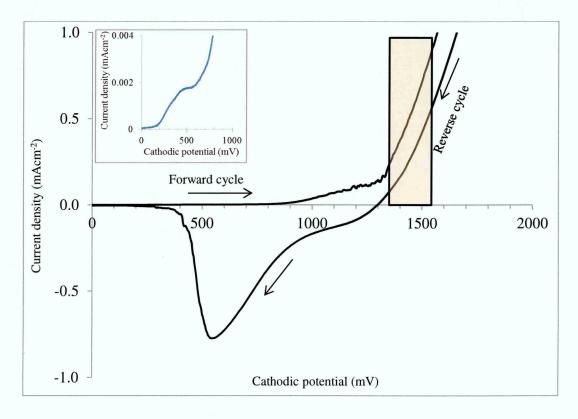

| Figure 5-1: Cyclic voltammogram of aqueous solution containing $0.15M \ ZnSO_4 + 0.15 \ M \ (NH_4)_2S_2O_3$ in 400 ml of de-ionised water. Both the growth temperature and the pH were set to $\sim 30^{\circ}C$ and $4.00 \pm 0.02$ respectively107                 |

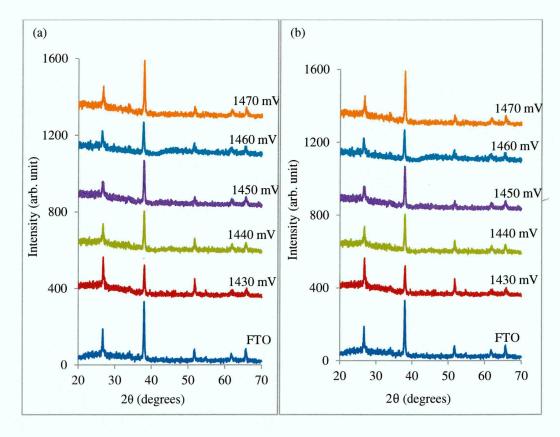

| Figure 5-2: XRD patterns of ZnS layers grown on glass/FTO substrate at different cathodic potentials for (a) as-deposited and (b) heat-treated (at 350°C for 15 minutes in air) layers.                                                                              |

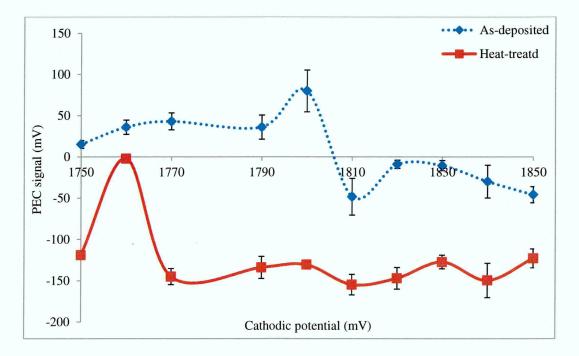

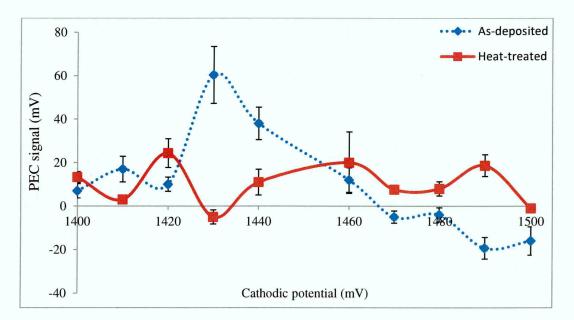

| Figure 5-3: PEC signal measurements as a function of growth voltage for both as-<br>deposited and heat-treated ZnS layers                                                                                                                                            |

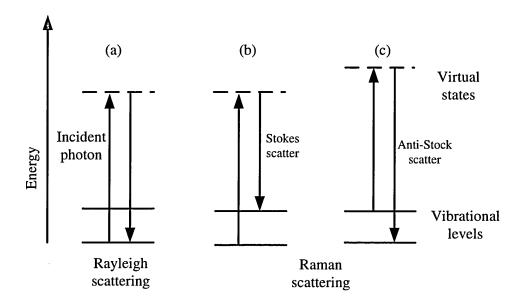

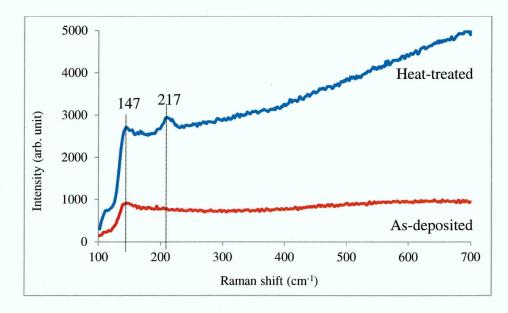

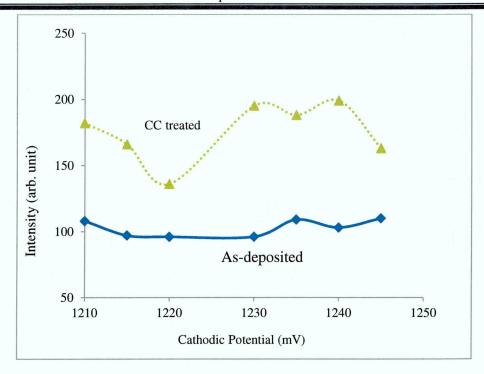

| Figure 5-4: Raman scattering spectra recorded on glass/FTO/ZnS thin films of as-<br>deposited and heat-treated (at 350°C for 15 min in air) samples                                                                                                                  |

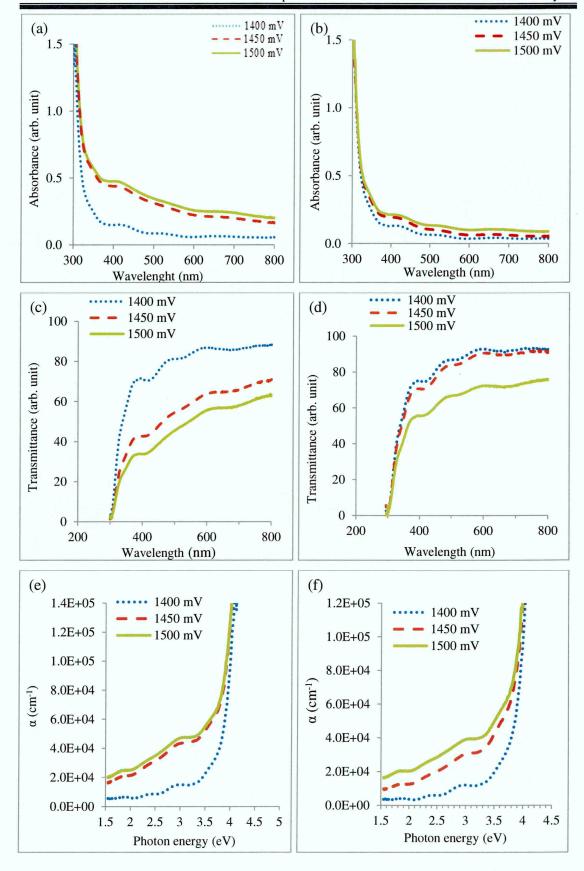

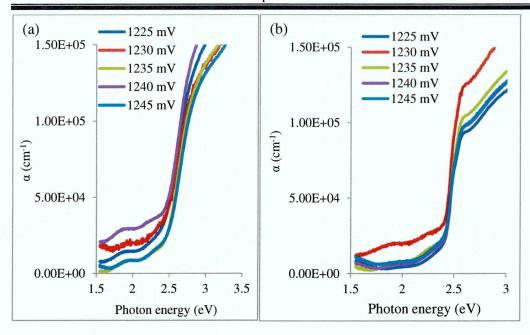

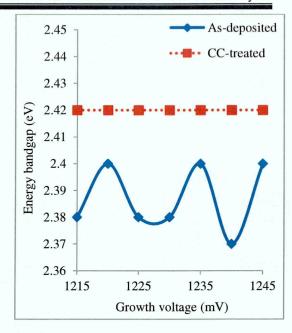

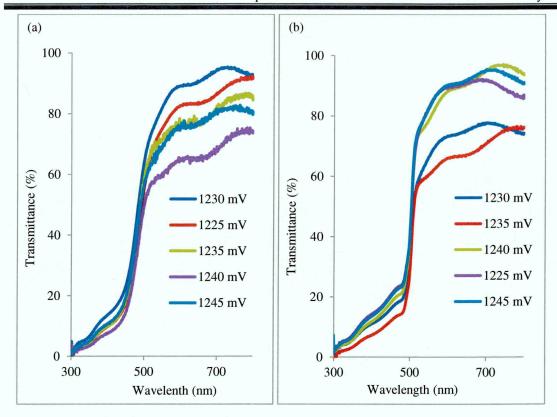

| Figure 5-5: (a,c,e) are the optical absorbance (A), transmittance and absorption coefficient, $\alpha$ versus hv for as-deposited and (b,d,f) are the optical absorbance, transmittance and $A^2$ versus hv for the annealed ZnS layers grown at different voltages. |

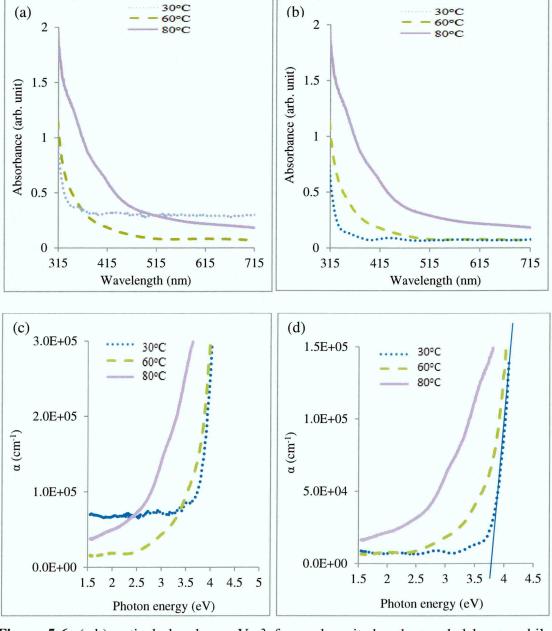

| Figure 5-6: Optical absorbance Vs $\lambda$ for as-deposited (a) and (b) annealed layers while (c) and (d) are their respective absorption coefficient versus hv plots for samples grown at different temperatures.                                                  |

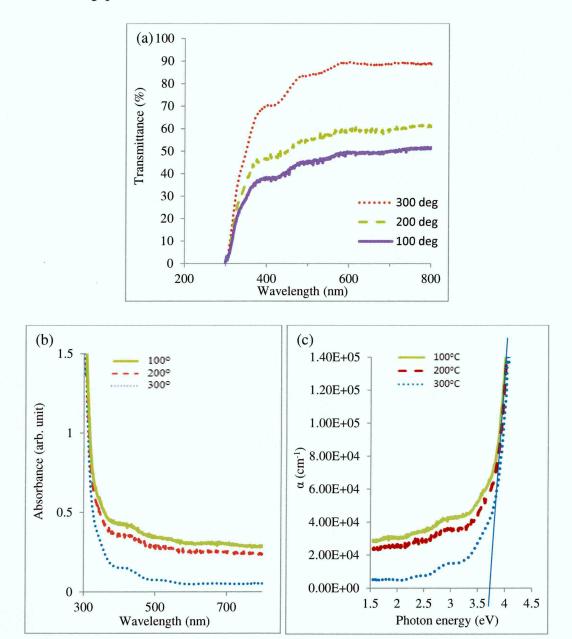

| Figure 5-7: The plots of (a) transmittance, (b) absorbance (c) optical bandgap spectra for ZnS layers heat treated at different temperatures for 15 minutes in air.                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

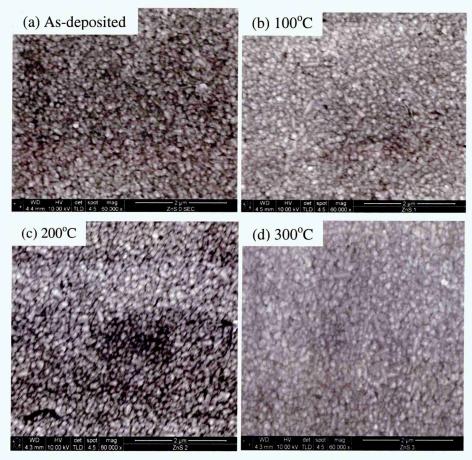

| Figure 5-8: SEM images for (a) as-deposited and (b), (c), and (d) are heat-treated glass/FTO/ZnS layers at 100, 200 and 300°C respectively for 15 min in air117                                                                                                 |

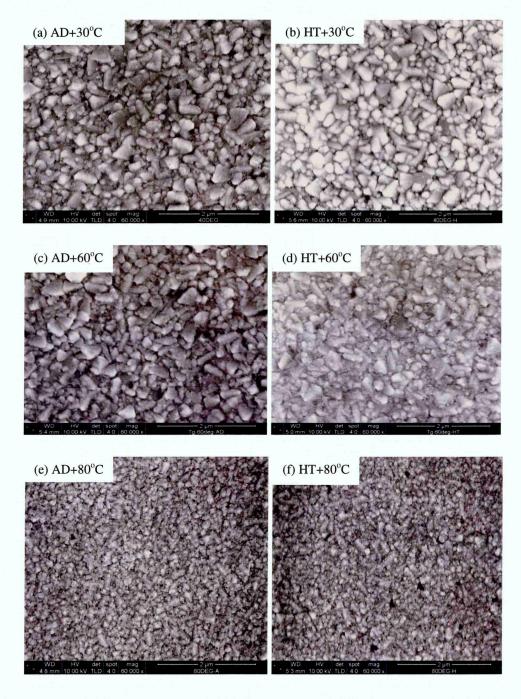

| Figure 5-9: SEM images of glass/FTO/ZnS layers grown at different growth temperature (a,c,e) as-deposited and (b,d,f) annealed samples                                                                                                                          |

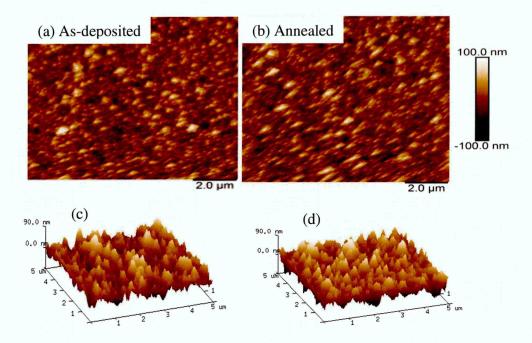

| Figure 5-10: 2D and 3D AFM images of (a) as-deposited and (b) heat-treated ZnS layers grown on glass/FTO substrate.                                                                                                                                             |

| Figure 5-11: Plot of theoretical and experimental thickness estimated for electroplated ZnS films                                                                                                                                                               |

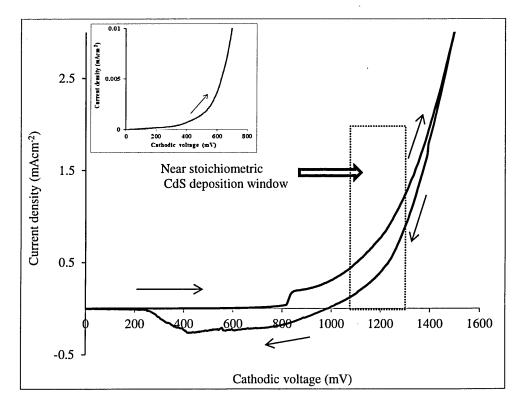

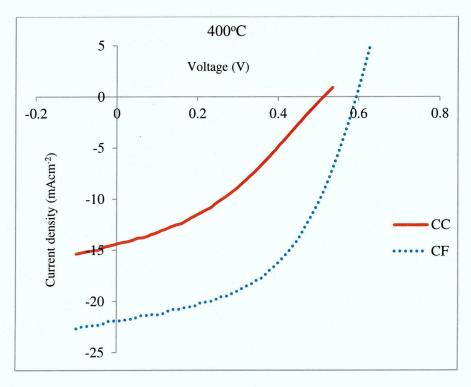

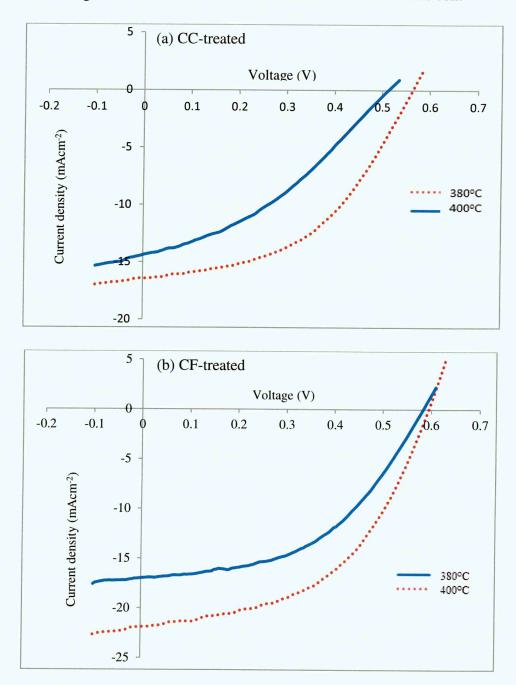

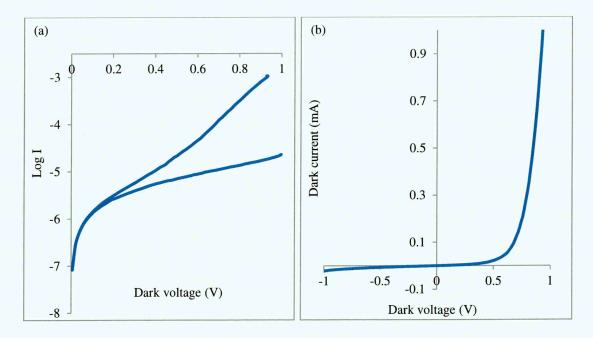

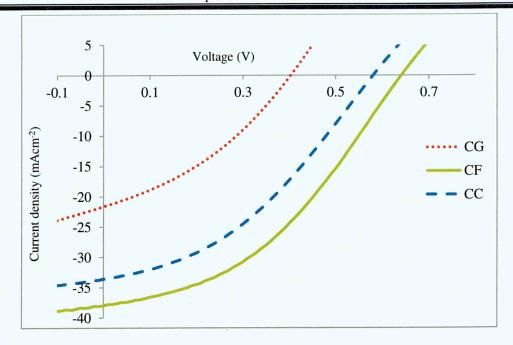

| Figure 6-1: Cyclic voltammogram for an electrolyte consisting of $0.075 \text{ M CdCl}_2$ and $0.15 \text{ M } (\text{NH}_4)_2\text{S}_2\text{O}_3$ . The pH and temperature of the electrolyte were $2.50\pm0.02$ and $\sim\!85^{\circ}\text{C}$ respectively. |