Fabrication and characterisation of porous silicon.

MABROOK, Mohammed F.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/19990/

#### A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/19990/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

101 657 572 6

# REFERENCE

nes are charged at 50n mo

ProQuest Number: 10697297

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10697297

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

# FABRICATION AND CHARACTERISATION OF POROUS SILICON

### MOHAMMED FADHIL MABROOK

B.Sc., M.Sc.

A thesis submitted in partial fulfilment of the requirements of

Sheffield Hallam University

for the degree of Doctor of Philosophy

November, 2000

**School of Engineering**

#### **Declaration**

I certify that this thesis submitted for the degree of Ph.D. is the result of my own research, except where otherwise acknowledged, and that this thesis has not been submitted for a higher degree to any other university or institution.

Signed:....

MOHAMMED FADHIL MABROOK

Date:..../..../....

# **Dedication**

This thesis is dedicated to my beloved parents, brothers, sisters, my wife and my coming child.

#### **ABSTRACT**

A systematic study has been made of the electrical conduction processes through electrically etched porous silicon (PS) films sandwiched between two metal electrodes. The PS layers were formed by anodisation of p-type silicon wafers in a hydrofluoric (HF) acid solution. The effect of fabrication conditions on the structural and electrical properties of PS have been investigated. The thickness of PS layers was found to depend on the anodisation time, whereas porosity was regarded to be controlled by the current density and HF acid concentration.

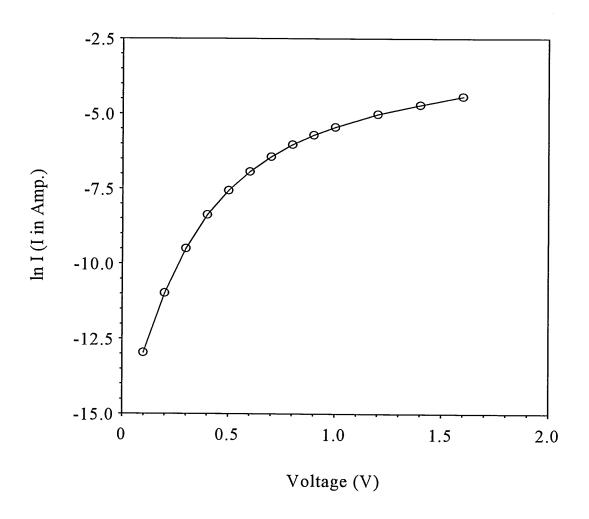

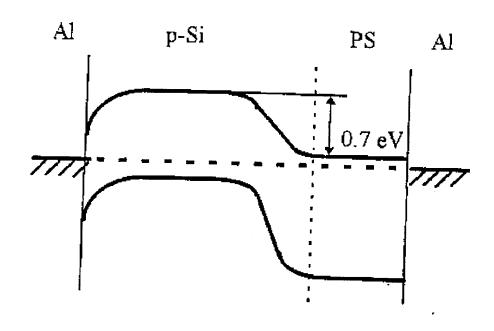

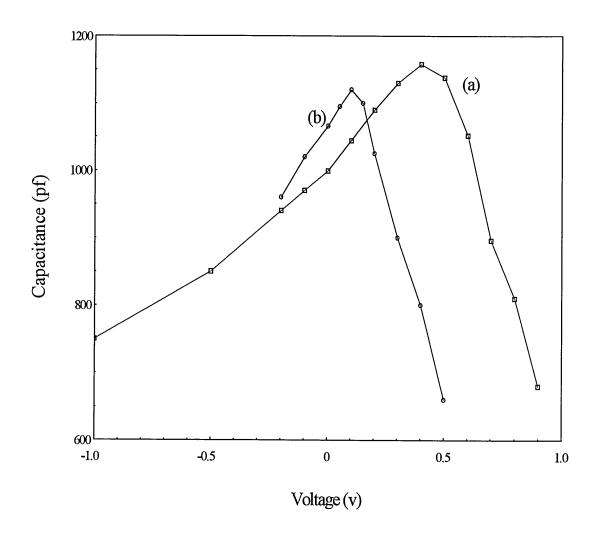

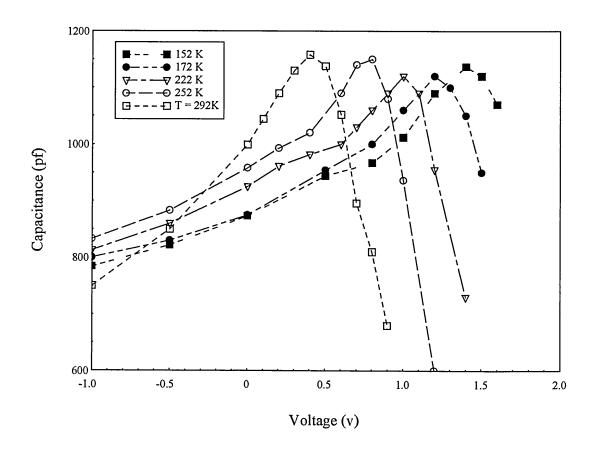

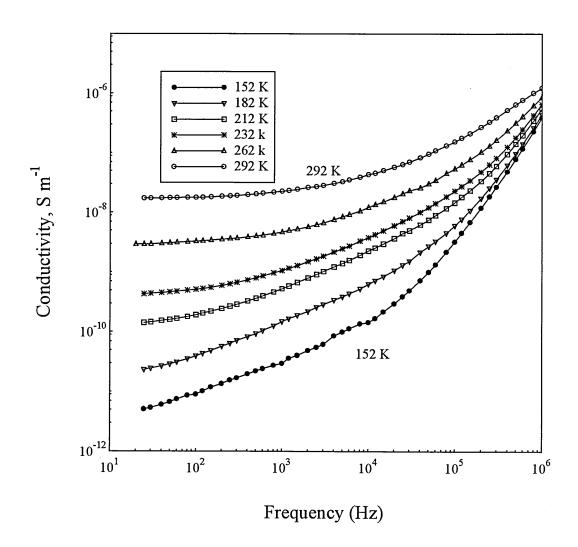

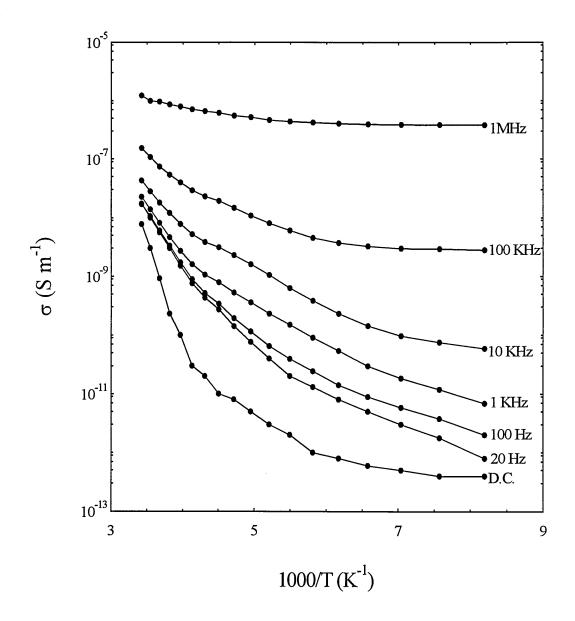

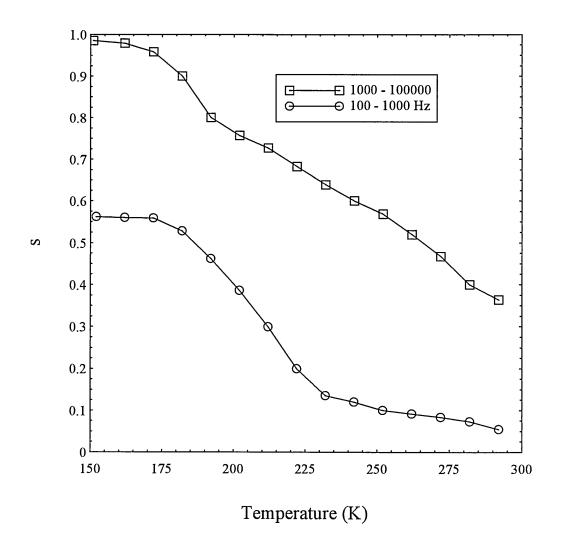

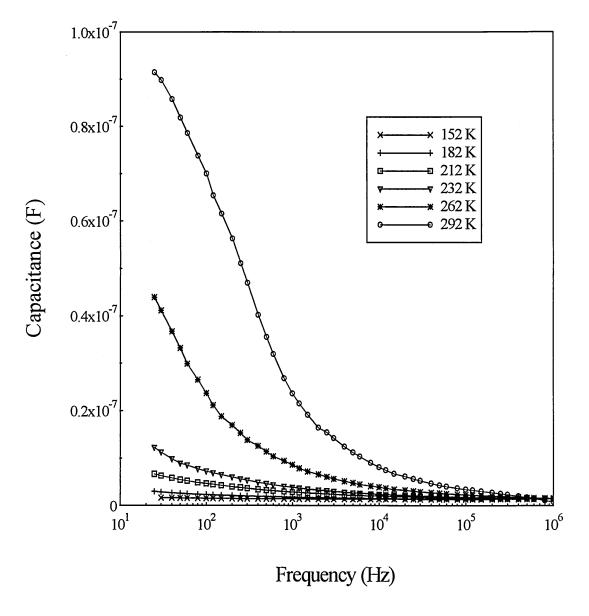

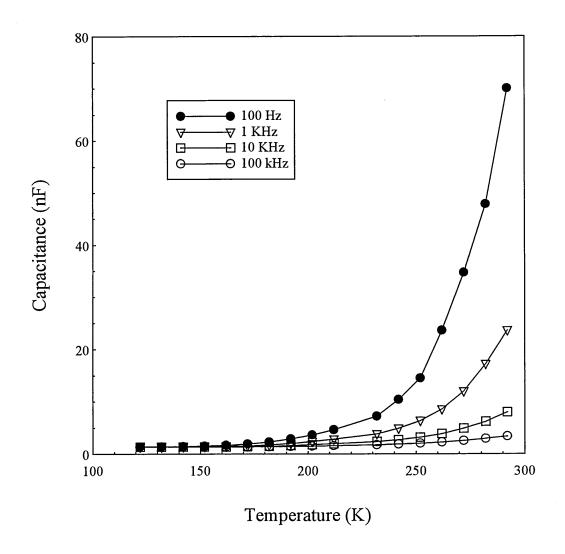

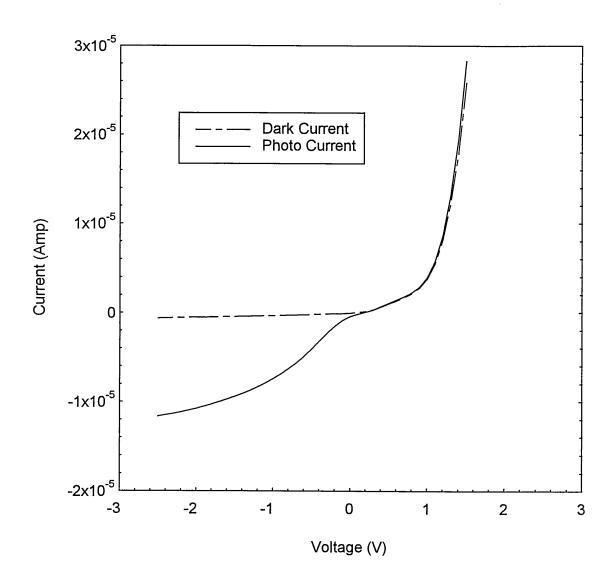

The dark current-voltage I(V) characteristics at fixed temperature and the variation of current as a function of temperature have been established. The characteristics for all devices, regardless the metal contact, show a rectifying behaviour with ideality factor close to unity. It was found that PS films fabricated from p-type silicon substrates behave like n-type silicon due to the depletion of electronic holes. The results suggest that a pn heterojunction between PS and p-Si is responsible for the rectifying behaviour. A value of 0.7 eV was obtained for the barrier height at the interface between PS and p-Si at room temperature. The barrier height was found to increase with rising temperature. Recombination conduction process was found to be dominant at low temperatures as the activation energy did not exceed 0.22 eV. At high temperatures, thermionic emission diffusion process was found to be responsible for the current transport in the PS structures. A band model was proposed for metal/PS/p-Si/metal structures in order to explain the observed characteristics. A.c. dark current measurements revealed that the a.c. conductivity varies as  $\omega$  where  $\omega$  is the angular frequency and s is an index which depends on temperature and having a value less than unity. A.c. activation energy was interpreted in terms of hopping conduction at low temperatures (less than 200 K) and diffusion transport of charge carriers through PS layers at higher temperatures. Measurements of capacitance as a function of frequency and temperature showed a decrease with increasing frequency and increase with increasing temperature. The photoconduction behaviour of PS was characterised by high dark resistivity, a clear photosensitivity for visible light, and a bias voltage dependence of the spectral response.

#### **ACKNOWLEDGEMENTS**

I am deeply indebted to my director of studies Professor A. K. Ray for initially giving me the opportunity to undertake a Ph.D. study in the School of Engineering, Sheffield Hallam University, and for his kindness, support and supervision throughout my studies.

My special appreciation to Professor Z. Ghassemlooy and Dr. S. Brown, School of Science, Sheffield Hallam University, for their interest, help and guidance.

I would like to express my gratitude and thanks to Dr. A. K. Hassan and Dr. A. V. Nabok for their continuous encouragement, advice, and valuable suggestions.

I extend my appreciation to all the technical staff of the School of Engineering, in particular Mr. K. Duty for his special help. My sincere thanks to Mr. P. Slingsby from the Material Research Institute, Sheffield Hallam University, for performing the scanning electron microscopy.

I would like also to thank all my fellow Ph.D. colleagues for their help and friendship during the course of my study and wish them all the best for their future.

I also wish to express my special thank to my brother Abass Mabrook and his wife Mrs. Jacqueline Mabrook for their continuous encouragement and without them I could not be here from the beginning.

Finally I would like to thank my special friend and my wife Dr Salma Al-Harran for her kindness patience and support all the way through my study.

# TABLE OF CONTENTS

| ABS                                                                                                                                                                                                                                                                                                                                                                                                                                | j                                              |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------|

| ACF                                                                                                                                                                                                                                                                                                                                                                                                                                | KNOWLEDGMENTS                                  | i    |

| TAB                                                                                                                                                                                                                                                                                                                                                                                                                                | BLE OF CONTENTS                                | ii   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |      |

| TABLE OF CONTENTS  CHAPTER ONE  Introduction and aims of the work  CHAPTER TWO  2.1 Introduction  2.2 Band structure of semiconductors  2.3 Nanostructured silicon (porous silicon)  2.4 Formation of porous silicon  2.5 Porosity and pore size  2.6 Porous silicon for optical measurements  2.7 Photoluminescence in porous silicon  2.8 Electroluminescence in porous silicon  2.9 Electrical properties of porous silicon  21 |                                                |      |

| Intro                                                                                                                                                                                                                                                                                                                                                                                                                              | oduction and aims of the work                  | 1    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    | Introduction                                   | 6    |

| 2.2                                                                                                                                                                                                                                                                                                                                                                                                                                | Band structure of semiconductors               | 6    |

| 2.3                                                                                                                                                                                                                                                                                                                                                                                                                                | Nanostructured silicon (porous silicon)        | 7    |

| 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                | Formation of porous silicon                    | . 11 |

| 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                | Porosity and pore size                         | 14   |

| 2.6                                                                                                                                                                                                                                                                                                                                                                                                                                | Porous silicon for optical measurements        | 16   |

| 2.7                                                                                                                                                                                                                                                                                                                                                                                                                                | Photoluminescence in porous silicon            | 17   |

| 2.8                                                                                                                                                                                                                                                                                                                                                                                                                                | Electroluminescernce in porous silicon         | 20   |

| 2.9                                                                                                                                                                                                                                                                                                                                                                                                                                | Electrical properties of porous silicon        | 21   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.9.1 D.C. conductivity in porous silicon      | 22   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.9.3 Photoconduction properties of PS         | 30   |

| 2.10                                                                                                                                                                                                                                                                                                                                                                                                                               | Practical application of porous silicon        | 31   |

| СНА                                                                                                                                                                                                                                                                                                                                                                                                                                | PTER THREE                                     |      |

| Expe                                                                                                                                                                                                                                                                                                                                                                                                                               | rimental apparatus and measurements techniques | 34   |

| 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                | Introduction                                   | 34   |

| 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                | Porous silicon formation                       | 34   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.2.1 Design the fabrication setup             | 34   |

|      | 3.2.2 Porous silicon formation process                   | 36 |  |  |

|------|----------------------------------------------------------|----|--|--|

| 3.3  | Electrical contacts                                      |    |  |  |

|      | 3.3.1 The evaporation system                             | 40 |  |  |

|      | 3.3.2 The evaporation procedure                          | 43 |  |  |

| 3.4  | The measurements systems                                 | 45 |  |  |

|      | 3.4.1 Electrical measurements                            | 47 |  |  |

|      | 3.4.2 Photoelectrical measurements                       | 48 |  |  |

| CHA  | APTER FOUR                                               |    |  |  |

| Mic  | rostructure and formation mechanism of porous silicon    | 52 |  |  |

| 4.1  | Introduction                                             | 52 |  |  |

| 4.2  | The principles of anodic oxidation                       | 52 |  |  |

| 4.3  | Porous silicon formation mechanism                       |    |  |  |

| 4.4  | Silicon surface dissolution chemistry                    |    |  |  |

| 4.5  | Structure study of the porous silicon surface            |    |  |  |

| CHA  | APTER FIVE                                               |    |  |  |

| DC 1 | Electrical properties of porous silicon                  | 72 |  |  |

| 5.1  | Introduction                                             | 72 |  |  |

| 5.2  | Theoretical aspects                                      | 72 |  |  |

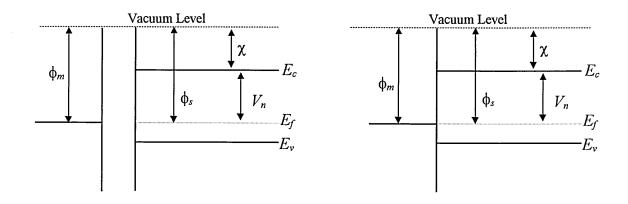

|      | 5.2.1 Electrical contacts (metal-semiconductor contacts) | 72 |  |  |

|      | 5.2.1.1 Ohmic contacts                                   | 74 |  |  |

|      | 5.2.1.2 Blocking contacts                                | 76 |  |  |

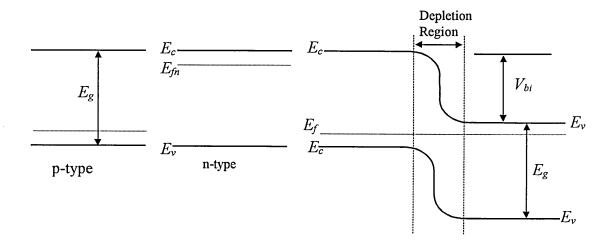

|      | 5.2.2 The p-n junction                                   | 80 |  |  |

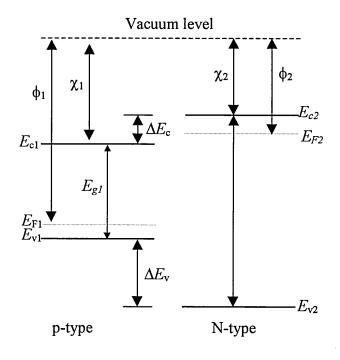

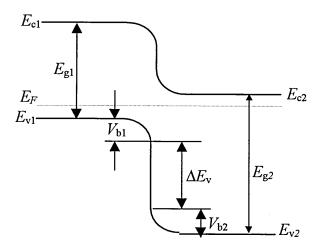

|      | 5.2.3 Heterojunctions                                    | 84 |  |  |

|      | 5.2.4 Current transport models in semiconductors         | 87 |  |  |

|      | 5.2.5 Temperature dependence and activation energy       | 89 |  |  |

| 5.3  | Experimental results and discussion                      |    |  |  |

|      | 5.3.1 Current-voltage characteristics of porous silicon     | 90  |   |

|------|-------------------------------------------------------------|-----|---|

|      | 5.3.2 The band structure of porous silicon                  | 106 |   |

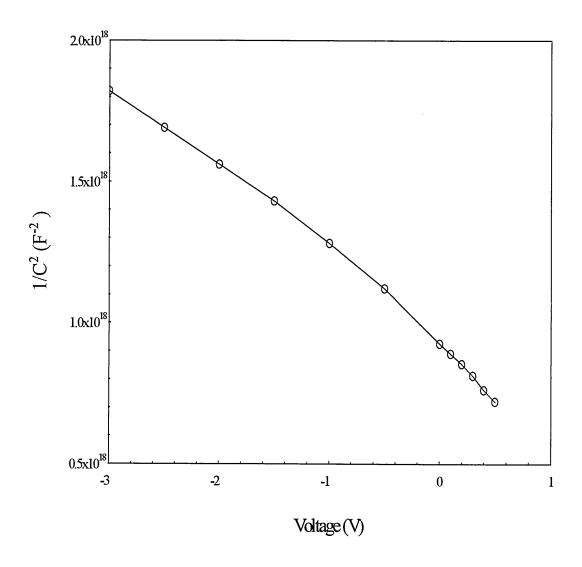

|      | 5.3.3 Capacitance-voltage characteristics of porous silicon | 109 |   |

| СНА  | APTER SIX                                                   |     |   |

| AC   | Electrical properties of porous silicon                     | 114 |   |

| 6.1  | Introduction                                                | 114 |   |

| 6.2  | Theoretical background                                      | 114 |   |

|      | 6.2.1 A.c. conduction                                       | 114 | 1 |

|      | 6.2.2 Capacitance and Loss Tangent                          | 117 |   |

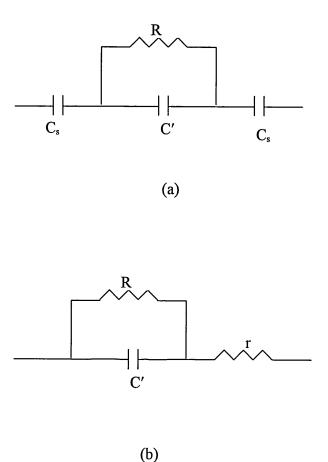

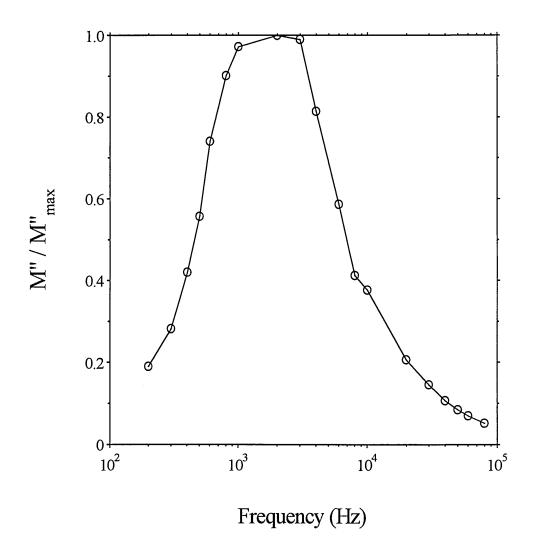

|      | 6.2.3 Impedance spectroscopy                                | 120 |   |

| 6.3  | Experimental results and discussions                        | 122 |   |

|      | 6.3.1 A.c. conduction of porous silicon                     | 122 |   |

|      | 6.3.2. Capacitance and loss tangent                         |     |   |

|      | measurements of porous silicon                              | 128 |   |

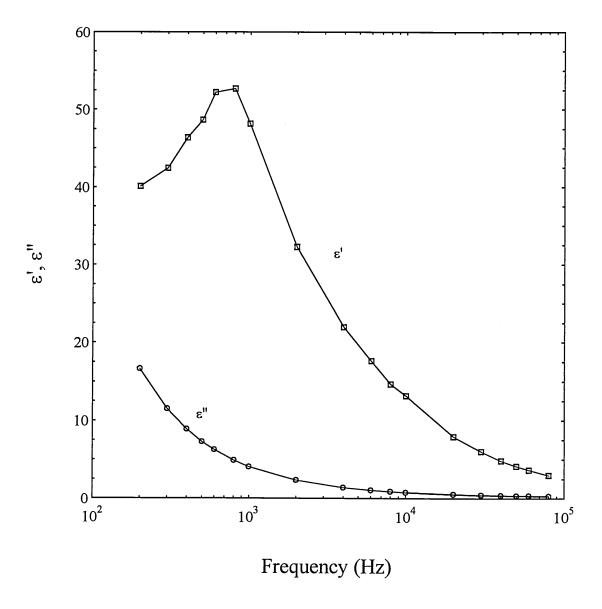

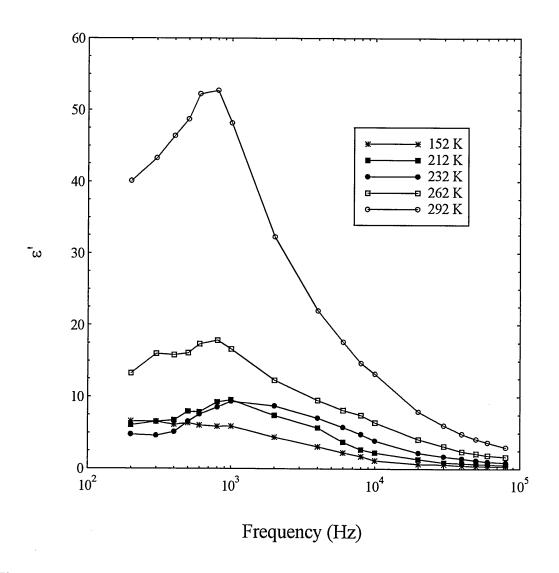

|      | 6.3.3 Dielectric properties of porous silicon               | 131 |   |

| СНА  | APTER SEVEN                                                 |     |   |

| Phot | toelectronic properties of porous silicon                   | 142 |   |

| 7.1  | Introduction                                                | 142 |   |

| 7.2  | Theoretical background                                      | 142 |   |

| 7.3  | Experimental results and discussions                        | 146 |   |

|      | 7.3.1 Photoconduction spectra                               | 146 |   |

|      | 7.3.2 Photocurrent-voltage characteristics of PS            | 152 |   |

| CHA  | APTER EIGHT                                                 |     |   |

| Con  | clusions and future work                                    | 160 |   |

| 8.1  | Fabrication characteristics of porous silicon               | 160 |   |

| 8.2      | Electrical measurements and conduction properties |            |

|----------|---------------------------------------------------|------------|

| 8.3      | Suggestion for future work                        | 164        |

| REF      | ERENCES                                           | 165        |

| APPENDIX |                                                   | <b>A</b> 1 |

#### **CHAPTER ONE**

#### INTRODUCTION AND AIMS OF THE WORK

Silicon is a material which accounts for over 98% of sales in the global semiconductor market. There are many reasons why silicon devices dominate the microelectronics market, but the main factor is their stability and low manufacturing cost. Millions of devices with identical properties can be fabricated across increasingly larger silicon wafers, reducing the cost per device. The fabrication processes and the performance of the devices relay mainly on a number of inherent properties of silicon. Insulating materials made from silicon substrates (like silicon dioxide and silicon nitride) have allowed silicon to dominate over the other materials such as gallium arsenate (gas) and III-V semiconductor compounds. Moreover, it is more expensive to fabricate devices from III-V materials than from silicon because different processing techniques must be used and these have not yet reached the remarkable yields of silicon chips [Paul 2000].

However, there are a number of areas where silicon devices cannot compete with other semiconductor devices. The band structure of silicon has an indirect band gap of 1.1 eV, which means there is no optical recombination of excited states in bulk silicon in the visible region. As a consequence, optoelectronic devices, such as light emitting diodes, have to be made with other substrates. GaAs proved to be leading in this kind of devices as the electrons in the conduction band can combine with the holes in the valence band much more easily in GaAs than in silicon. In recent years, it is found that light emission out of silicon becomes achievable by using nanocrystalline silicon

structure. The way of obtaining this type of structure is by the formation of porous silicon (PS) [Richter et al 1992].

The principle feature of PS is a fine structure consist of pores separated by very small size columns of silicon. It may be fabricated by electrochemical desolution of silicon in a concentrated hydrofluoric (HF) acid solution. The pore size and hence the porosity of PS can vary over wide range depending upon the type and resistivity of the silicon substrate, the current density during anodisation, and the concentration of HF acid [Bomchil and Halimaoui 1988, Herino et al 1992, Badoz et al 1993]. Under the right conditions, more than 85% of the silicon is etched off leaving very thin silicon rods separated by large pores. The thickness of the PS layer can be controlled by the anodisation time, which usually does not exceed 30 minutes [Halimaoui et al 1992, Filippove et al 1994].

PS with high porosity can produce photoluminescence and electroluminescence in the visible range [ Canham 1990, Koshida and Koyama 1992]. PS shows an increase in the band gap shifting the absorption edge to higher energies. The band gap energy and the peak of the luminescence spectrum are mainly depending on the fabrication conditions of the PS layer. However, the electrical properties of PS have recently attracted considerable attention owing to its potential applications in optoelectronic devices and sensor systems. Furthermore, the significant increase in the surface to volume ratio made from PS a promising layer for chemical sensing technology. This phenomenon has stimulated investigations into potential applications of PS in the field of gas sensing. Adsorbed species, such as alcohol, benzene, and other gases have profound effects on the PS film electronic properties [Angelucci et al 2000, Bilenko et al 2000, Bogue 1997, Thust et al 1999].

Al, Au, and ITO electrodes have been found to behave as injecting contacts to PS, where ohmic and rectifying behaviours have been observed. Sandwich thin film structures of PS were investigated with reasonable thicknesses of PS layers. The conduction mechanism of PS is somewhat complex and numbers of theories have been developed based on various experimental data. Two junctions could be responsible for the conduction in PS sandwich structures. Schottky junction between the metal and the PS layer was firstly reported as the main blocking contact responsible for the rectifying behaviour of the structure [Kosida and Koyama 1992, Dimitrov 1995, Simons et al 1995]. In the last few years it was reported that a pn heterojunction between the PS layer and the silicon substrate is behind the rectifying behaviour of PS [Pulsford et al 1994, Ray et al 1998].

Under a.c. fields, the conductivity of PS is higher by several orders of magnitude than that under d.c. conditions [Cruze et al 1998]. In general, the conductivity decreases with increasing frequency in the case of band conduction process, while it increases with increasing frequency in the case of hopping conduction process. Ben-Chorin et al (1993) reported that band conduction occurs at high temperatures and hopping transport become dominant at low temperatures in the PS devices made from n-type silicon substrates.

Our knowledge of the electrical and photoelectrical properties of PS is generally rather limited. The aim of this work is to investigate the fabrication and the electrical characterisation of PS. It is hoped that the results obtained should also be of assistance in any future work made on similar structures. To achieve this, a variety of experimental techniques have been utilised to study PS thin film for material

characterisation. These techniques include electrical and photoelectrical studies of metal/PS/p-Si/Al sandwich structure and the microstructure study of PS thin film using SEM technique. The major part of the experimental work can be summarised as fellows:

- I. The first stage of the study was to design and build a PS fabrication set-up and prepare suitable homogenous and reproducible samples. Different samples with different fabrication conditions were produced for electrical and photoelectrical studies.

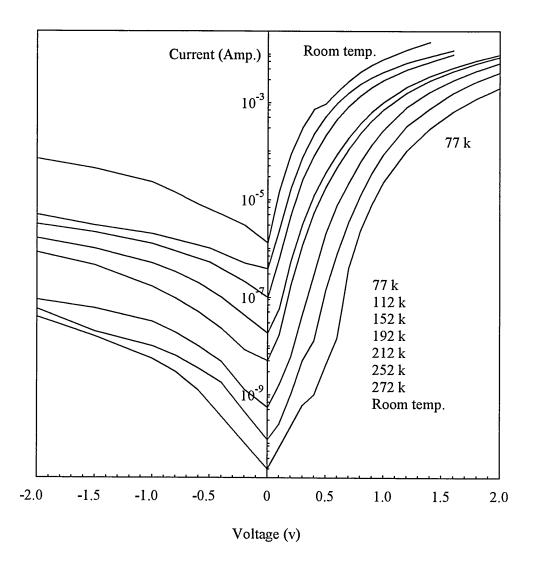

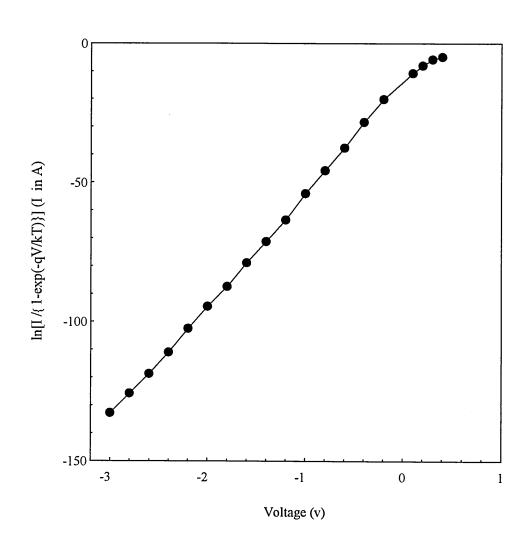

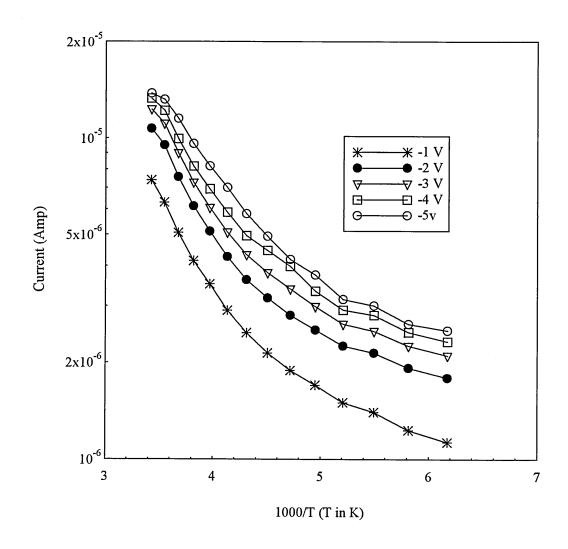

- II. D. c. current-voltage characteristics within the temperature range 152 300 K were measured in order to determine the activation energy, barrier height, and the type of conduction mechanism in PS.

- III. A.c measurements in the frequency range 20 Hz to 1 MHz and the temperature range of 152 - 300 K have also been carried out to gain further information on the conduction mechanisms in PS.

- IV. Spectral responses of PS samples in different thicknesses were measured in the UV, visible, and IR regions. The photocurrent effect was also investigated for the same samples.

The thesis is presented in eight chapters. A general review of PS and its properties, in particular electrical properties, is given in chapter two. Details of the methods of fabrication, deposition, and measurement techniques are discussed in chapter three. Chapter four reports the structural properties and the electrochemistry

of pore formation of PS. Theoretical aspects concerning conduction mechanisms in semiconductors are introduced at the first parts of chapters five, six, and seven. The other parts of these chapters are devoted to a detailed account of the results obtained, data analysis, and discussion of the results. Finally, in chapter eight general conclusions concerning the results obtained and suggestions for further work are presented.

#### **CHAPTER TWO**

#### GENERAL REVIEW OF POROUS SILICON

#### 2.1 Introduction

This chapter is a general review of the formation and the structural, electrical and luminescence properties of porous silicon (PS). Special attention will be given to the formation and the electrical properties of PS, and in particular the mechanisms responsible for the current transport through PS structures. The remainder of the chapter is concerned with the electrical and industrial application of PS.

#### 2.2 Band structure of semiconductors

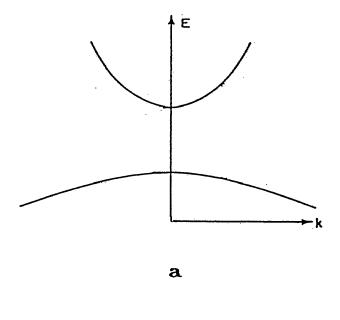

The basic property of a semiconductor is that it has an energy gap which separates the filled valence band from the empty conduction band. Conventionally, the band structure of a semiconductor is represented by a dispersion relation E(k) where E is the energy of an electron (or hole) at the band edge and k is the wave vector. Figure 2.1 shows the E versus k diagram for Si and GaAs. It could be noticed that the valence band structure for most semiconductors is similar especially at k=0. According to the band structure, semiconductors can be divided into two classes. The first class is called direct bandgap semiconductors in which the valence band maximum and the conduction band minimum occur at the same value of the wave vector. The other class of the semiconductors are those in which the conduction band minimum and the valence band maximum are separated in k space and known as indirect band gap

semiconductors. Figure 2.1(a) demonstrates the GaAs as a direct band gap semiconductor, with its conduction band minimum directly above the valence band maximum at the point where k = 0. In Fig. 2.1(b) the lowest minimum in the conduction band displaced from the point k = 0 resulting on indirect band gap in silicon. In the indirect band gap semiconductors, the electron moving from valence to conduction band must undergo a change in wave vector. The disadvantage of the indirect band gap semiconductors is that the optical absorption is allowed only with absorption of a phonon to conserve crystal momentum and it is much weaker process than in direct band gap materials [Chelikowsky and Cohen 1976, Ioffe 1960, Moss 1961, Perkowitz 1993, Rice 1977, Voos et al 1980]. An electron can be elevated from the valence to the conduction band if it absorbs a photon whose energy is at least equal to the band gap value. The reverse process, since momentum must be conserved, would result in photoluminescence process near the band gap which strongly affected by whether the material has a direct or indirect bandgap [Iyer and Xie 1995, Pankove 1971].

#### 2.3 Nanostructured silicon (porous silicon)

Although bulk silicon is intrinsically inefficient at radiative recombination process, silicon can however be produced in nanostructured forms which produce efficient photoluminescence (PL) in the visible range. During the studies of electropolishing of silicon (electrolytic smoothing of solid surfaces) Uhlir at Bell Labs, US, in 1956 discovered the first PS film (under certain conditions an unwanted black film appeared on the wafer surface). There was only little interest in this black film until Yoshio Watanabe and co-workers at NTT Japan realised, during the early

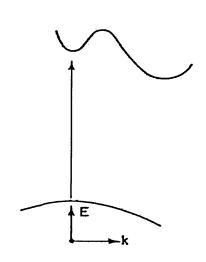

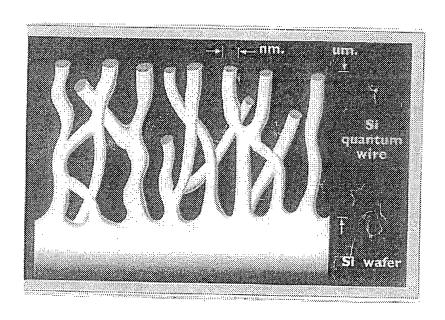

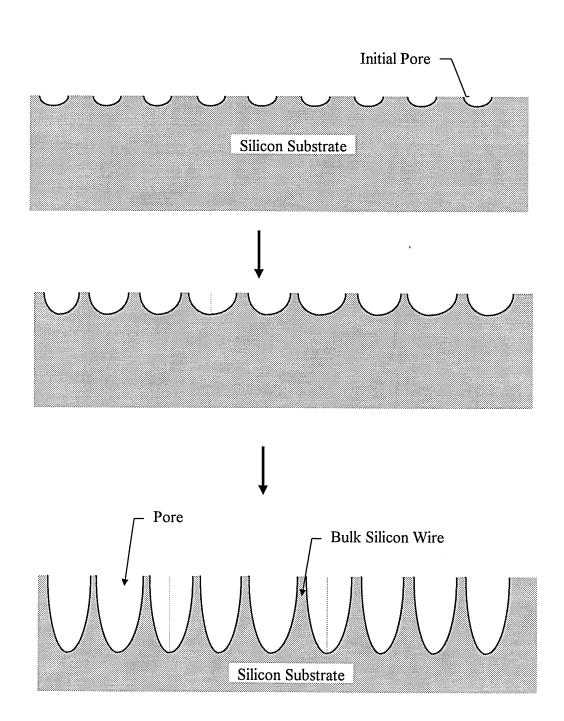

1970's, that these films were highly porous (and called porous silicon) and likely to be readily oxidised and of potential use in silicon-on insulator (SOI) technology. The formation mechanisms of this new material have been studied widely by a large number of scientists [Beale et al 1985, Bomchil et al 1989, Gee 1960, Memming and Schwartz 1966, Parkhutik et al 1983, Turner 1958, Unagami 1980]. In 1981, Kazou Imai at NTT, demonstrated that full isolation of silicon devices could be achieved by using PS (so called FIPOS technology). Ten years ago, Canham from the Defence Research Agency, UK, described the process of making porous layers on the surface of silicon wafers as a technique of fabricating silicon quantum wires of subnanometer size as shown in Fig.2.2 [Canham 1990]. It was found that the optical properties of PS are different from the those of bulk silicon. Moreover, PS exhibits PL at an energy that is large compared to the band gap of crystalline silicon [Canham 1990, Cullis and Canham 1991, Foll 1991, Herino et al 1992, Kalkhoran et al 1992, Koshida and Koyama 1991, Koshida and Koyama 1992, Lee and Peng 1993, Lehmann et al 1992, Maruyama and Ohtani 1994, Motohiro et al 1995, Read 1992, Rees 1991, Sanders and chang 1992, unal and Bayliss 1996]. The absorption edge of PS was found to be shifted to higher energies of about 1.5 eV compared to bulk crystalline silicon which has an absorption edge in the infrared region. The increase in the band gap and the emission energy suggested to be due to the quantum confinement effect, i.e. if the porosity of PS increases (leading to thinner wires) the band gap becomes greater and the PL emission will be at higher energy [Canham 1990]. Other possible mechanisms could be responsible for the light emitting in PS is the existence of luminescent molecules such as siloxene on the surface of the pores. The data on PS obtained so far support the quantum confinement mechanism suggested by Canham (1990).

b

Figure 2.1 The energy bands for direct (a) and indirect (b) bandgap materials [After Voos et al 1980].

Figure 2.2 Schematic diagram of porous silicon layer [After Canham 1990].

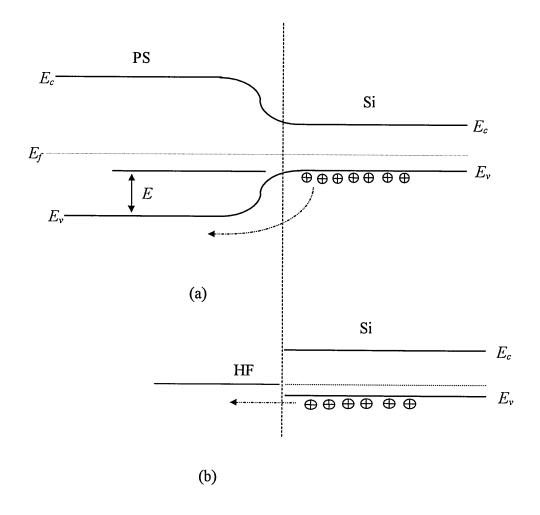

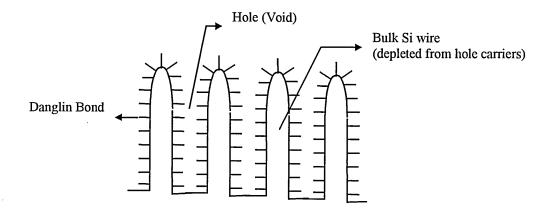

The increased band gap decreases the concentration of the mobile charges within the remaining silicon structure and create a depletion layer [Smith and Collins 1992]. These results were reproduced by workers in many laboratories around the world and intense investigations into this phenomenon resulted [Koshida and Gelloz 1999, Pulsfurd 1994]. Electroluminescence (EL) in the visible range has been also observed from Schottky diodes formed on PS [Halimaoui 1991, Koshida and Koyama 1992].

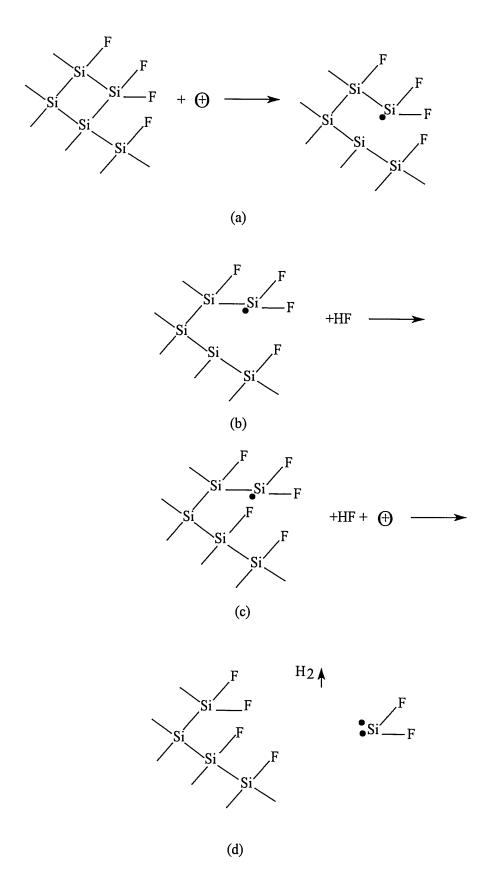

#### 2.4 Formation of porous silicon

Porous silicon is fabricated by an anodic dissolution process in hydrofluoric acid (HF) based electrolyte. Although the microscopic details of pore formation are complex and not completely understood, a complex grid of interconnected silicon skeleton is created. The microstructure of PS depends on the composition of the electrolyte, the type and resistivity of the starting silicon substrate, the current density during anodisation, and the anodisation time [Halimauoi et al 1991, Brandet et al 1992, Herino et al 1992]. Under the right conditions, a large pore structure created, in which as much as 85% of the silicon is etched off leaving silicon wires as thin as a few nanometers [Herino et al 1992, Zhang et al 1992].

The principal feature of PS is a very fine structure either wires or dots and the structural analysis of this material is quite difficult. In contrast, the formation of PS appears to be a self-adjusting process in which the quantum confinement effect governs the formation process. Using p-type substrates, the PS structure gets smaller until full depletion of the holes occurs on the surface of the PS layer. The electrochemical etching process stops at this stage if no extra holes are supplied to the surface by the

light. In n-type silicon substrates, there are no holes present and a depletion layer forms around the pores forcing the etching process to stop. To continue the etching until the production of nanoporous film, it is important to illuminate the samples during the fabrication to generate more holes on the surface [Steiner et al 1993]. In general, PS layers are fragile and by nature exhibit very high surface area. The resulting structure luminescence from red to blue when an UV radiation is applied to its surface.

The thickness of the PS layer can be controlled by the anodisation time only [Halimaoui et al 1991, Filippove et al 1994]. Depending on the type and resistivity of the silicon substrate, the diameter of electrochemically etched pores cover most of the PS layer. According to the pore size of PS layers, the material can be designated into three types [Cullis et al 1992]:

- 1. Microporous silicon, with pore diameter of less then 2 nm.

- 2. Mesoporous silicon, with pore diameter between 2 and 50 nm.

- 3. Macroporous silicon, with pore size of more than 50 nm.

The material with greatest interest is microporous silicon because of its luminescent properties. Although microporous silicon is found in all samples independently of the level of doping, only on moderately doped p-type substrate can pure microporous silicon be found. On p<sup>+</sup> and n<sup>+</sup> type substrates the PS structure is a mixture of microporous silicon and mesoporous silicon, while for low doped n-type substrates the microporous silicon is found to cover the wall of macropores [Gösele and Lehmann 1995, Lockwood et al 1992]. The inhomogeneous doping of the silicon substrate would make the structure even more complicated. Table 2.1 summarises the

fabrication conditions which lead to the creation of a layer of PS on top of the silicon substrate.

| Substrate resistivity | 0.01 - 250 Ω/cm               |

|-----------------------|-------------------------------|

| Current density       | 1 - 250 mAmp./cm <sup>2</sup> |

| HF acid concentration | 10 -50 %                      |

Table 2.1 Fabrication conditions of PS

The formation of microporous silicon can be understood in term of hole depletion in the porous structure due to its quantum size dimensions [Lehmann and Gösele 1991]. According to this model, using higher formation current density (Higher than 100 mAmp./cm²) leads to a smaller and mechanically less stable skeleton of microporous silicon. A microporous silicon layer of high porosity cracks during drying and the pieces shrink in size. This is could be due to the collapse of the pores under the attractive forces between the hydrogen atoms expected on the wall of the silicon wires. Microporous silicon layers formed at current densities below 100 mAmp./cm² were found to dry without cracking for a layer thickness of about 10 µm which attributed to the more stable silicon skeleton formed at low current densities [Filippove et al 1994, Lockwood et al 1992].

The relationship between the band gap widening and the size of the silicon wires in PS has been studied by many researchers. According to different experimental studies the photon energy of the PL from PS is about 1.6-2.2 eV, and thus the band

gap widening must be larger than this. The typical size range of the silicon wires in this type of PS layers is between a few nm and 10 nm [Bayliss et al 1994, Muller et al 1993]. Sanders and Chang (1992) give the wire thickness of about 1.5-3 nm for the fundamental bandgap of 1.5-2.7 eV. Other calculations by Buda et al (1992) estimated the thickness of the silicon wires to be between 0.83-1.45 nm, whereas 2.5-4.5 nm thicknesses were reported by Proot et al (1992) and Delerue et al (1995). From the study of Steigmeier et al (1992), it was found that the nanopartical diameters of PS reach more than 10 nm for energy bandgap range of 1.7-2.8 nm.

#### 2.5 Porosity and pore size

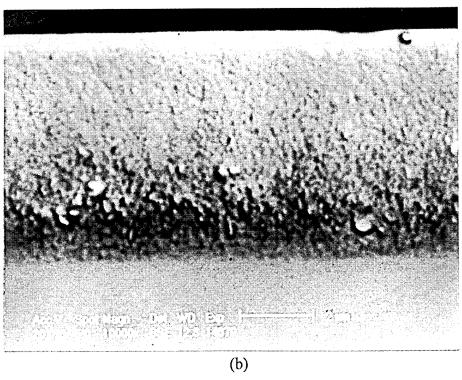

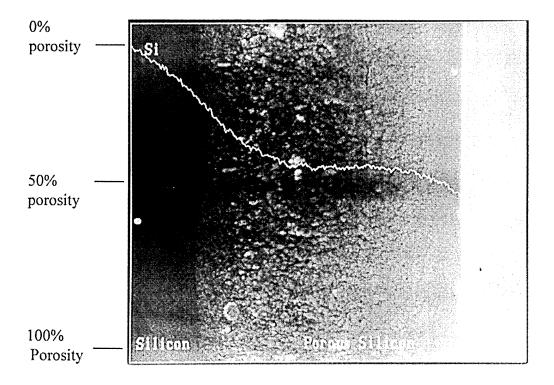

Although there is some divergence of the calculated values of the porosity and the pore size depending on the methods and researchers, its clear that the calculated values for silicon nanowires are too small to be consistent. It is not easy to measure the pore size or the silicon nanowires since the pore dimensions are usually below the resolution limit of the scanning electron microscopy (SEM) as will be clearly studied in chapter four. For clear images of the surface of the PS layer it is important to use transmission electron microscopy (TEM) which required removing the PS layer from it's substrate. The pore size increased with the formation current density and the formation time. It was also found that the pore size correlates with the HF concentration with non-linear increase with decreasing HF concentration [Herino et al 1987].

The other important parameter in PS characteristics is the porosity of the sample. Porosity (P) can be estimated if the sample is weighed, before anodic reaction  $(m_1)$ , after anodic reaction  $(m_2)$ , and after the removal of the PS layer from the

substrate  $(m_3)$ . The porosity then can be calculated with an accuracy of about 2% according to [Herino et al 1987]:

$$P = \frac{m_2 - m_3}{m_1 - m_3} \tag{2.1}$$

Matsuda et al (1990) used the optical properties of PS to estimate the porosity. According to their method, the porosity can be calculated using:

$$1 - \frac{P}{100} = \frac{n_c^2 - 1}{n^2 - 1} \tag{2.2}$$

Where n is the refractive index of the bulk silicon and  $n_c$  is the refractive index of the porous silicon. However, porosity can be estimated from the cross section SEM study of the PS layer profile (more details in chapter 4).

Bomechil and Halimaoui (1988) have investigated the relationship between the porosity and the fabrication conditions. For a given HF concentration, the average film porosity increases with the formation current density. For a heavily doped substrate in 25% HF concentration, the porosity increases regularly from about 25% to 70% when the formation current density rises from  $10 \text{ mA/cm}^2$  to  $250 \text{ mA/cm}^2$ . The current density was estimated from I/a, where I is the measured current and a is the surface area of the anode. At higher current densities, the porosity becomes very high and the material losses its mechanical cohesion and becomes like a powder. However, it is possible to create a PS layer with porosity of more than 70% by reducing the HF acid concentration and increasing the current density. If the current density further

increased, direct electropolishing of the anodised layer will take place and then no film formation [Bomchil and Halimaoui 1988].

For all kind of substrates, an increase in the HF acid concentration, keeping a constant current density, results in decreasing porosity of the PS layer. If the porosity reaches values more than 70%, again the layer losses its mechanical properties and behaves like a powder. It is possible to form PS layers with the same porosity and pore size using a different combination of fabrication conditions [Herino et al 1987].

#### 2.6 Porous silicon for optical measurements

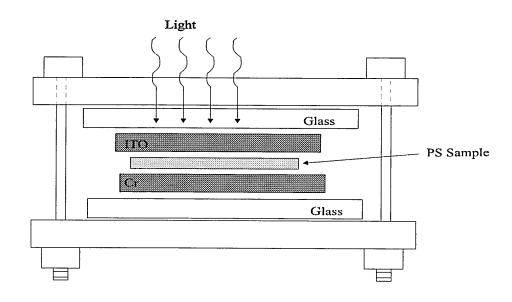

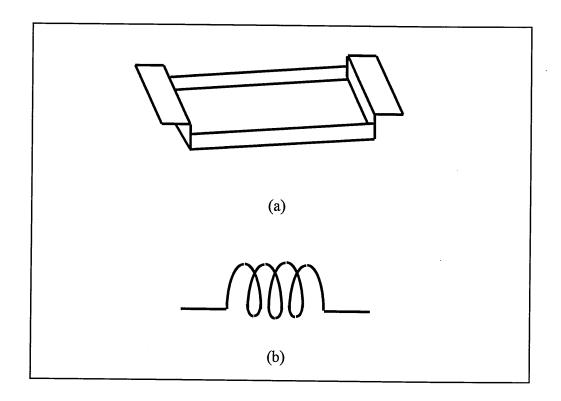

The study of PS is usually carried out with the PS layer attached to the silicon substrate. However, for the optoelectronic characterisation of PS it is necessary to evaluate the intrinsic nature of PS without the effect of the silicon substrate. Moreover, it is not possible to study the optical properties of PS without detaching the layer from it's substrate. Self-supporting PS layers can be prepared by electrochemical separation of the anodised PS layer. This is achieved by rapidly increasing the anodisation current density up to the values in the electropolishing region (> 400 mA/cm<sup>2</sup>) after the completion of the PS formation [Koshida and Koyama 1992b]. Badoz et al (1993) produced a self supported PS layer by reducing the HF acid concentration to a very low concentration (below 10%) and increasing the current density to a value of about 250 mA/cm2. The outcome from the electrochemical separation process is a very thin layer of PS (few micrometers) which proved to be very difficult to handle. In order to make an electronic contact to the self supported PS layer, Hlinomaz et al (1994) proposed a mechanical contact holder (Fig. 2.3) which could be used for electrical. photoelectrical and optical measurements of the self supporting PS layer. The sample

placed between two glass microscopic slides coated on the inner side by indium tin oxide (ITO) or Cr and mechanically gently pressed together. The advantage of this holder is that there is no risk of short circuit that may be caused by evaporating a metal to make the electrical contacts [Badoz et al 1993, Hlinomaz et al 1994].

Figure 2.3 Mechanical contact holder [After Hlinomaz et al 1994].

#### 2.7 Photoluminescence in porous silicon

Radiative recombination in semiconductors has been the subject of an enormous number of experimental and theoretical investigations that have proven very fruitful for the development of semiconductor physics. These fundamental studies have given rise to interesting applications in light emitting diodes and semiconductor lasers.

The simplest case of radiative recombination is when electrons in the conduction band recombine with the holes in the valence band giving up energy, which approximately corresponds to the energy bandgap, as electronic radiation which may be emitted from the semiconductor [Ellis 1973, Street 1991].

In the electronic excitations of a semiconductor which result in a nonequilibrium state of the semiconductor, radiative recombination represents one of the processes that can achieve a relaxation to the semiconductor ground state and regain the equilibrium state. Typically, excitation may be by photon absorption (photoluminescence) or current injection (Electroluminescence) [Voos et al 1980].

Photoluminescence (PL) is defined as the optical radiation emitted at different wavelengths by a physical system resulting from excitation to a nonequilibrium state by irradiation with light [Barry Bebb and Williams 1972]. PL emission is characteristic of material and involves radiative transitions between electronic energy levels in the material. The transition originates on some excited electronic levels, and after the emission of a photon a lower electronic level is occupied [Bar-Lev 1984]. The mechanism of PL can be divided into three stages, the first stage is the excitation of electron-hole pair. This occurs by photon absorption with energies close to the band gap energy. In the second stage, the excited carriers thermalise rapidly down to the band edge by emitting phonons until they are captured into localised states. The final stage is where the carriers can recombine either radiatively to give PL or non-radiatively [Bar-Lev 1984].

In bulk silicon, because of its indirect band gap, the emission of light is not possible due to the need of a change in the crystal momentum. Therefore the PL of bulk silicon is weak as nonradiative recombination becomes more efficient. But since

the discovery of the strong visible PL in PS by Canham (1990) many experimental and theoretical investigations have tried to identify the origin of this PL. However, the mechanism of the strong visible PL from PS still unclear. The main difficulty of this problem arises mainly from the large surface to volume ratio in nanostructures. Two main mechanisms have been invoked to explain PL in PS. The first one assumed that the visible light emission from PS layer is not an intrinsic property of crystalline silicon but depends on specific chemical reactions of silicon with hydrogen and oxygen [Brandt et al 1992, Fuchs et al 1992, Koch 1993, Stutzmann et al 1993]. The second mechanism proposed that PL in PS is intrinsic due to quantum confinement effects in small size silicon wires in the PS layer [Amato et al 1994, Canham 1990, Cullis and Canham 1990, Fauchet 1998, Filippov et al 1994, Gelloz 1997, Gole et al 1999, Korol and Kikkarin 2000, Koyama et al 1996, Lahmann and Gösele 1991, McGinnis et al 2000, Muller et al 1993, Rajaraman et al 1997, Skryshevsky 2000, Tsu et al 1992, Uosaki et al 1996, Wang 1995, Zhang 1995]. The second explanation is now more favoured as most works agree that the quantum size effect in the spongelike PS skeleton might play a key role in its optical properties as suggested originally by Canham (1990).

The most convincing results which support the quantum size effect is the blue shift of the PL peak with increasing the porosity of the PS layer which represents the average size of the PS nanostructures [Voos et al 1995]. The results is in qualitative agreement with the quantum size effect and indicates that the increase in the porosity results in a decrease in the size of the silicon wires in PS making the carrier confinement energy increase.

#### 2.8 Electroluminescence in porous silicon

Electroluminescence (EL) occurs when electrons in materials such as semiconductors, are excited by the application of an electric field to the material, resulting in an electric current passing through it. The electrons recombine with holes to emit light as a function of applied voltage. Most practical solid state devices for visible injection EL used III-V compounds such as GaAs and GaP. This is because this series of materials produces high efficiency LEDs due to their direct energy band gap.

Since the discovery of visible PL from PS by Canham (1990), the production of efficient visible EL from PS has become a goal of extreme practical importance, motivated by the potential application in optoelectronic devices [Araki et al 1996, Bsiesy and Vial 1996, Bsiesy et al 1995, Fauchet 1996, Goryachev et al 1997, Halimaoui et al 1991, Koshida and Koyama 1992, Koshida et al 1995, Lalic and Linnros 1996, Nishimura et al 1998, Riess et al 1994, Steiner 1995, Takasoka and Kamei 1994]. EL has been observed with either dry contacts obtained by metallisation of the sample surface [Koshida and Koyama 1992, Koyama et al 1993, Lopez and Fauchet 1999, Nyrup et al 2000, Ogasawara et al 1995, Riley et al 1996, Tsybeskov 1995] or wet contacts resulting from immersion of PS in an electrolyte [Gelloz et al 1998, Goryachev et al 2000, Halimaoui et al 1991, Kooij et al 1994, Peter and Wielgosz 1996, Sakai et al 1994]. EL has been induced by injection of a sufficient number of electrons into the porous silicon layer (where the radiative recombination occurs).

Just like PL, EL can be analysed in the framework of the quantum confinement model [Bsiesy et al 1996, Muller et al 1993, Kozlowski and Lang 1992]. Short lived

EL has been observed during anodic oxidation of PS fabricated from p-type silicon substrate [Halimaoui et al 1991]. Efficient EL has also been observed from PS layers fabricated from n-type silicon substrates [Astrove et al 1995, Canham et al 1992, Gelloz et al 1998, Goryachev et al 2000, Lopez and Fauchet 1999, Riley et al 1996].

EL has been obtained from PS by making Schottky diodes between PS and Au or ITO electrodes. Diodes made by evaporation of Au, however, have showed a very low efficiency because the evaporated contact does not penetrate into the nanoporous layer and involves high applied bias voltages [Bsiesy et al 1996, Koshida and Koyama 1992]. Using indium tin oxide (ITO), generally, as the top electrode in LEDs provide better contacts and less light absorption.

#### 2.9 Electrical properties of porous silicon

The discovery of electroluminescence behaviour in PS has stimulated many researchers to make further d.c. and a.c. electrical measurements on the material over a wide range of temperature and frequency. Wide range of theoretical and experimental studies have been carried out in an attempt to understand the electronic conduction mechanism of this material. The electrical conductivity is affected by the fabrication conditions of PS, especially the formation time as it controls the thickness of the PS layer and then the resistivity of the PS layer. Disagreements reported between the experimental and theoretical results obtained by different workers from measurements on PS are mainly due to this effect. Other factors like the humidity of the device and residual HF acid inside the PS pores reported to have important influence on the electrical properties of PS.

#### 2.9.1 D.C. conductivity in porous silicon

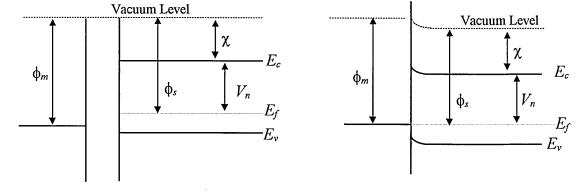

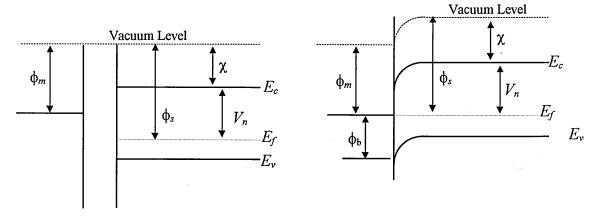

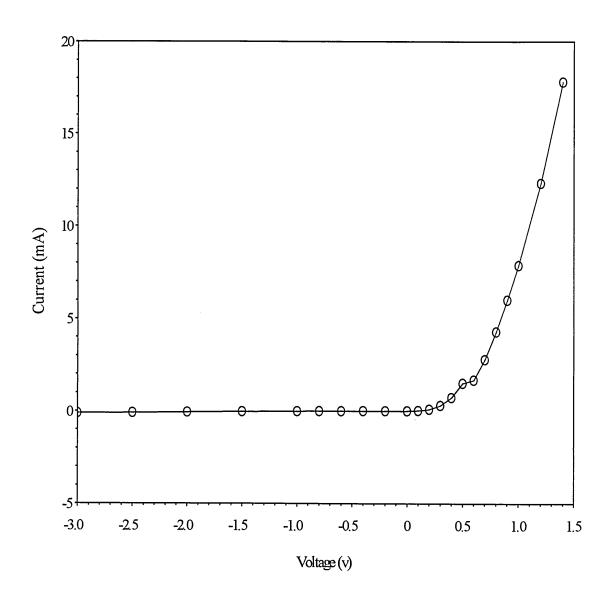

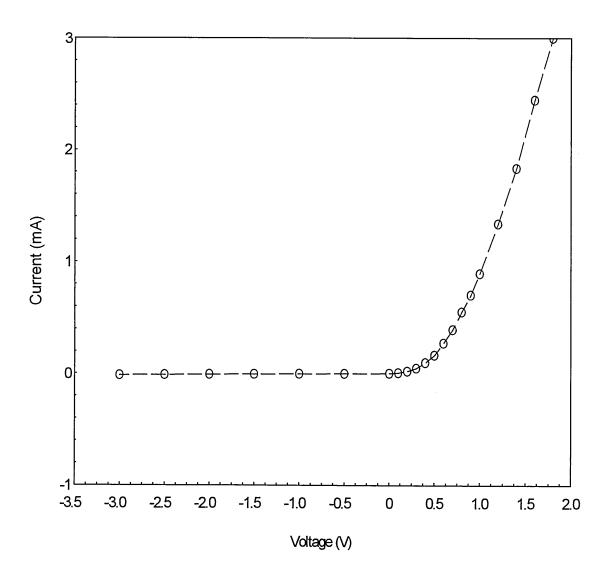

The first experimental evidence for rectifying behaviour in luminescent PS was reported in 1992 during EL study of the PS structure [Koshida and Koyama 1992. Namavar et al 1992]. Later, many researchers studied the electrical properties of metal/PS/Si/metal structures at room temperature [Lazarouk et al 1996, Maruska et al 1993, Namavar et al 1992, Simons et al 1995] and as a function of temperature [Dittrich et al 1996, Mares et al 1993, Mathur 1998]. In semiconductor device technology the electrode material is of great importance in determining the type of conductivity observed. Therefore, the electrical properties of PS devices in terms of current-voltage response have been studied using different types of contact. In general, Al [Ben-Chorin et al 1994, Deresmes et al 1995, Lazarouk et al 1996, Ray et al 1998], Au [Ozaki et al 1994, Ke et al 1998] and ITO [Namavar et al 1992, Pacebutas et al 1995] electrodes were used in most of the studies. The results indicate rectifying behaviour in all structures, except in some studies were they found that the behaviour of the device depends on the top electrode work function [Simons et al 1995, Oguro et al 1996].

Molnar et al (1999) have also investigated the current-voltage behaviour of ITO/PS/Si/Al structures for n-type and p-type substrates. They found ohmic behaviour for the n-type PS samples at low voltages (V>5V) and then the current increasing exponentially at higher voltages. In the p-type PS structures, however, the space charge region is confined to a much lower voltage (V<1V). At the same time, light emission from the p-type PS structures was found to take place under forward conditions, while in the n-type PS structures the luminescence appears in the reverse bias only.

There are two different opinions on the reason for the rectification effects in PS devices. In the majority of the work, the rectification in current-voltage characteristics is believed to be due to the existence of a Schottky barrier between the metal and PS interface. However, the interpretation of rectifying characteristics due to the junction between the PS and its silicon substrate is also reported. Ke et al (1998) have studied the contact barrier at Au/p-PS interface using ballistic electron emission microscopy (BEEM). This technique is more accurate than the conventional techniques, such as current-voltage and capacitance-voltage, in measuring the barrier height at metal/semiconductor interface. As the PS surface consists of wires and pores with dimensions of few nanometers, the contact barriers are expected to vary in a similar scale [Lavine et al 1993]. Therefore, extremely high resolution BEEM technique should be applied to gain reasonable information on this type of surface. The barrier heights measured from the current-voltage characteristics at different points of the PS surface were reported to be between 0.89-1.1 eV. In fact most of the barrier heights reported in the literature are much larger than that for the Au/p-Si interface (0.34 eV, Sze (1981)). However, there are some conflicting values for the barrier heights in the range of 0.8 eV, reported for a similar structure [Tung 1991]. These values are very close to that of Au/n-Si indicating that these contacts are likely to occure at the centre of wires in the PS layer. Ke et al (1996) concluded that PS could behave like n-type silicon at some points of the surface.

Deresmes et al (1995) have characterised Al/PS/p-Si/Al structures using electrical measurements. They conclude that the Schottky junction between Al and PS is responsible for the rectifying behaviour with a barrier height ranged between 0.1-0.3 eV. Schottky diode behaviours with anideality factor of 1.8 and barrier height of 0.75

eV were also reported for Au/PS/n-Si/Al structures [Dittrich et al 1996]. Similar results with even higher ideality factors were also observed for PS structures with different top electrodes [Bogue 1997, Koshida and Gelloz 1999, Koshida and Koyama 1992, Lazarouk et al 1996, Namavar et al 1992, Tsai et al 1993, Yu and Wie 1992, Zheng et al 1992]. Simons et al 1995 have proved that PS is n-type in nature by comparing the current-voltage characteristics of different metal/PS/n-Si/Al structures. They noticed that if Al were used as the top electrode, the structure would show ohmic behaviour. However, using Au as a top electrode results in a rectifying Schottky barrier of height 0.74 eV. Moreover, they observed similar behaviours for metal/PS/Al structures. Hence, they conclude that there is no effect of the silicon substrate on the device behaviour. Same conclusions were reported by Mares et al (1993) as they observed a linear current-voltage behaviour from Au/PS/p-Si/Al structure. The exponential increase in dark conductivity with temperature of the structure was ascribed to the tunnelling between thermally vibrating sites placed on the surface of PS. PS layers consist of several sublayers with different structural characteristics were reported by Pacebutas et al (1995). 1-3 µm thick nanostructured top layer was observed on top of a microstructured layer connected to the silicon substrate. Improved electrical and photoelectrical diode performances were observed for the samples with the top layer being removed [ Krotkus and Pasiskevicus 1992, Maruska et al 1993]. All the above reported evidence indicates that the interface between metal and PS plays a major role in the conduction mechanism in PS.

On the other hand, many workers have observed n-type material behaviour in PS. A study by Simons et al (1995) showed that PS fabricated from n-type substrates is n-type in nature. Furthermore, the electrical properties of PS films fabricated from p-type substrates have shown the same results [Mabrook et al 1995, Ozaki et al 1994].

This behaviour was ascribed to the depletion of holes in PS films and the fact that the depletion width is at least two orders of magnitude longer than the thickness of the silicon rods in PS film [Amisola et al 1992]. Also Pulseford et al (1993) have made a systematic study of the effect of various electrodes and the thickness of PS layers on the electrical properties of PS. They rolled out the effect of the metal/PS interface on the electrical properties of the material as they found that the device turn on is similar for all electrodes. Moreover, they reported that photoexcitation at the interface between the metal and the PS and across the PS layer produces no response. However, a sharp increase in the photocurrent is found to occur when the region just inside the silicon substrate is illuminated. This area of the device represents the interface between the PS layer and the silicon substrate, where the silicon is not completely etched.

Estimated values of the PS band gap were calculated from the luminescence and optical properties of the material. The photolominescence spectra of various devices show a peak at 650-700 nm at room temperature. This indicates that the band gap of the device is about 1.7-1.8 eV [Lang et al 1993, Pavesi et al 1997, Roy et al 1992, Vial et al 1992]. Furthermore, the peak of the photoluminescence spectra mainly depends on the thickness of the PS layer. Hence, the band gap of a PS layer depends essentially on the fabrication time. Cullis et al (1994) have observed a 1.5-1.7 eV band gap for PS layers depend on the postanodisation treatments. Optical studies of PS also shows an energy band gap of about 1.6-1.8 eV [Balagurov et al 2000, Buda et al 1992, Palsule et al 1997, Proot et al 1992]. Photoelectronic properties of PS show that PS layers have much wider band gap than silicon [Stievenard and Deresmes 1995]. Therefore, a heterojunction is expected to build up between PS and the silicon substrate resulting in the rectifying behaviour of the device [Pulsford et al 1994, Zimin 2000, Vikulov et al 2000]. The junction is either isotype heterojunction when n-type

silicon substrate is used, or anisotype heterojunction in case of using p-type silicon substrate.

Values of the barrier height reported heretofore range from 0-7-0.8 eV [Simons et al 1995, Dittrich et al 1996, Ray et al 1998]. These values of barrier heights are reported for PS samples made from both p-type and n-type substrates. However, higher values of barrier heights were reported for Au/PS/n-Si/Au structures [Laiho and Pavlov 1995]. Lower values of barrier heights were also observed for Al/PS/p-Si/Al structures at room temperature [Deresmes et al 1995, Pulsford et al 1994].

A very wide range of ideality factors were reported for different PS structures. Namavar et al (1992) have observed diode ideality factors of about 10 for a ITO/PS/p-Si/Al structure. Ideality factors of about 3-5 were also reported for Au/PS/n-Si/Al structures [ Simons et al 1995, Pacebutas et al 1995 ]. However values of less than 2 were also reported for different PS structures [ Dittrich et al 1996, Ray et al 1998 ].

The age of the PS samples were reported to have a considerable influence on their semiconducting properties. Ciurea et al (1998) have reported a stabilisation in the electrical properties of stored PS films compared to fresh samples. They observed a stronger rectifying behaviour for the PS films stored for 18 months in ambient conditions. In addition, the activation energy of the stored samples was estimated to be 0.6 eV at low temperatures and 1.8 eV at higher temperatures in contrast to the value of 0.55 eV calculated for fresh samples at all temperatures. This variation in conduction behaviour was ascribed to oxidation of the surface of the PS layer. These results are supported by the fact that PL properties (the shape of the spectral response and the position of the maximum) are changed with the age of the PS film [Ciurea et al 1996].

The thickness of the PS layer also plays a vital role in the electrical properties of the film. The value of the serial resistance of the device depends on the thickness of the PS layer. Values of few  $K\Omega$  to a few tens of  $M\Omega$  are reported for different PS samples [Yeh et al 1993, Mares et al 1993]. Ohmic behaviour was observed for thick PS samples, whereas rectifying conduction was found for thin layers. PS layers with thicknesses greater than 28  $\mu$ m were found to show linear current-voltage characteristics in the range of -100 V to 100 V. However, thinner samples appear to show rectifying behaviour at threshold voltages dependent on the PS layer thickness [Balagurov et al 2000]. At the same time they found the activation energy for all samples to be 0.55 eV at room temperature. The significant increase of resistivity was attributed the existence of hydrogen on the surface of the PS wires which passivate the dopant atoms. Mathur et al (1998) have observed symmetrical current-voltage characteristics only in the samples with thickness greater than 2  $\mu$ m. Similar results were reported by Ben-Chorin et al (1994) for PS layers of 10  $\mu$ m thickness.

It is well known that the electrical properties of a semiconductor could change drastically when adsorbing pollutant gas. PS is found to behave like a semiconductor in response to gases, humidity and oxygen [Bilenko et al 200, Koshida and Gelloz 1999]. Furthermore, various ambients have an influence on PS surfaces, and therefore, PS films have potential for the coming generation of gas sensing devices [Bilenko et al 2000, Kelly and Bocarsly 1998]. For the PS fabricated from p-type substrates, the conductivity was found to increase many orders of magnitude in response to vapour pressure change from 0 to 100% [Schechter et al 1995]. More about the PS response to the ambient environment is are reported in section 2.10.

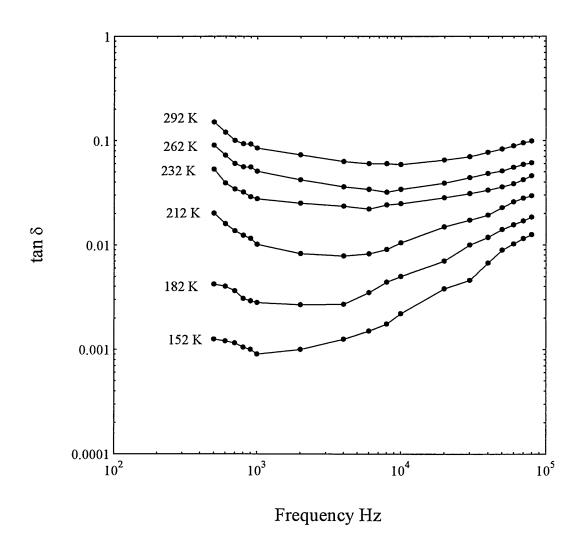

## 2.9.2 A.c. conductivity and capacitance

The d.c. electrical properties of PS have been widely studied, however much less data on the a.c. electrical properties is known. The a.c. conductivity of PS studied up to date has generally shown a power law dependence on angular frequency  $\omega$  of the form  $\omega^{S}$ . The index s was found to be variable, increasing with increasing frequency and decreasing with increasing temperature. This type of dependence represents a universal law [Mott and Davis 1971]. Such behaviour was observed over a frequency range of up to 10<sup>6</sup> Hz and a temperature range of 77-360 K. Ben-Chorin et al (1993) investigated the a.c. conductivity of a 10 µm thick PS layer at a wide range of frequencies and at different temperatures. The band gap energy of the sample was estimated to be around 1.7 eV. They observed power law conduction properties with an exponent s = 0.95 at frequencies below 10 kHz. At higher frequencies they reported higher values of s and they found no temperature dependence of the a.c. conductivity. Popkirov and Ottow (1997) have made a.c. measurements on Au/PS/n-Si/Al structure at room temperature and over a frequency range of 10-10<sup>6</sup> Hz. They claimed that the a.c. conductivity was almost constant at low frequencies whilst it was frequency dependent with s = 0.85 at higher frequencies. They concluded that this conduction was mainly due to the diffusion of charge carriers through the PS layers at low frequencies, whereas at high frequencies it is due to hoping of charge carriers. Higher values of s were also observed in different PS structures. Values of more than unity are observed for the exponent s by many researchers [Dimova-Malinovska et al 1997, Geloz and Bslesy 1998, Lysenko et al 1999, Yeh et al 1998].

The a.c. conductivity of Al/PS/p-Si/Al structures were studied by Parkhutik (1996) in the ranges 0.2-10<sup>5</sup> HZ and -100 to 200 <sup>0</sup>C. He observed a wide range of

activation energies (from 0.08 to 0.3 eV) directly influenced by the state of the surface layer at the pores walls (heated, wet or dry, etc.). Therefore, he claimed that it is very important to control all factors of PS formation and post-anodisation treatments to insure the necessary electrical and optical properties of PS. Parkhutik et al (1996) have also studied the electrical properties of PS at different post-anodisation treatments. They observed a linear growth of conductivity with increasing frequency for dry samples, whereas the as anodised samples are characterised by a power low with s changes between 0.2 to 1. They conclude that the frequency dependencies of the a.c. electrical conductivity of PS are sensitive to the presence of the residuals of electrolyte inside the pores.

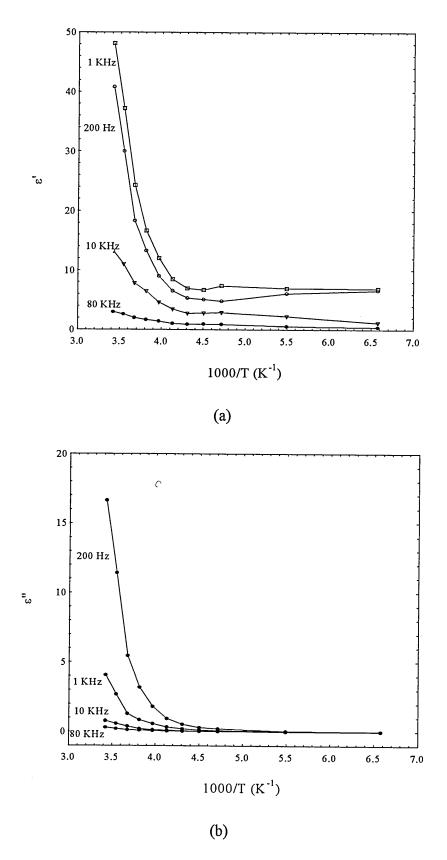

Measurements of capacitance and loss tangent (tan  $\delta$ ) as a function of temperature and frequency are also of interest. Generally, it has been observed that the capacitance decreases with increasing frequency, and increases with increasing temperature. This behaviour was observed in Ag/PS/p-Si/Al [Lebedev et al 1995] and Al/PS/p-Si/Al [Arita and Kuranari 1997] structures. Linearly decreased capacitance with log(f) was also observed over a wide range of frequencies [Averkiev et al 1996]. They reported a low frequency dispersion of the electrical capacitance at room temperature, and no frequency dependence at low temperatures. Such data may be interpreted using existing theory, for the case of a thermally activated process when using ohmic contact [Gaswami and Gaswami 1973].

The loss tangent, which relates the conductance and the capacitance, is also influenced by both frequency and temperature. A decrease in  $\tan \delta$  with increasing frequency has been observed in Al/PS/p-Si/Al structures [Arita and Kuranari 1997]. However, this parameter has received very little attention in PS studies.

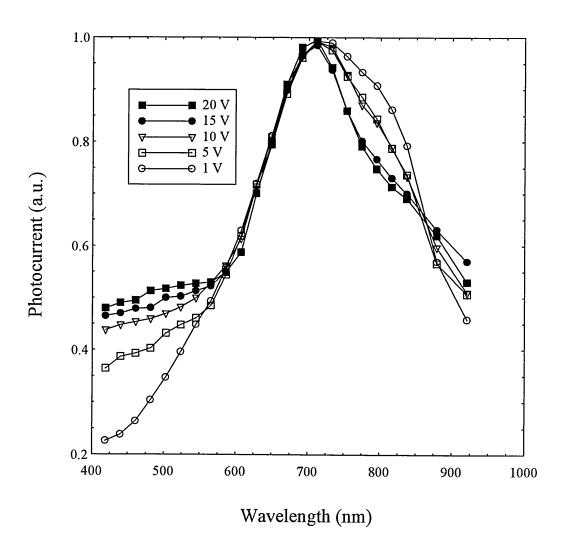

# 2.9.3 Photoconduction properties of PS

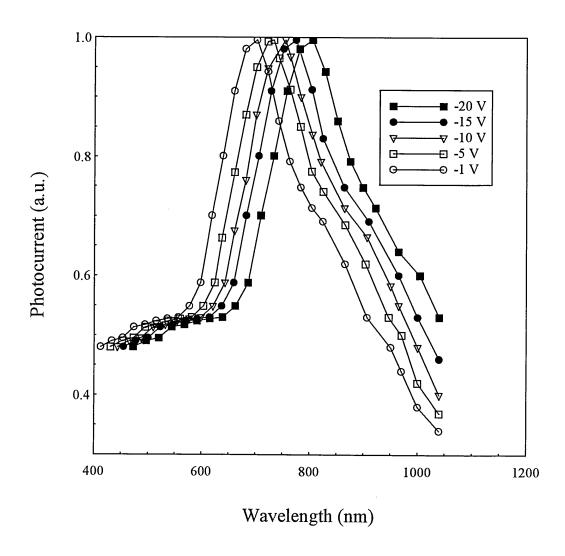

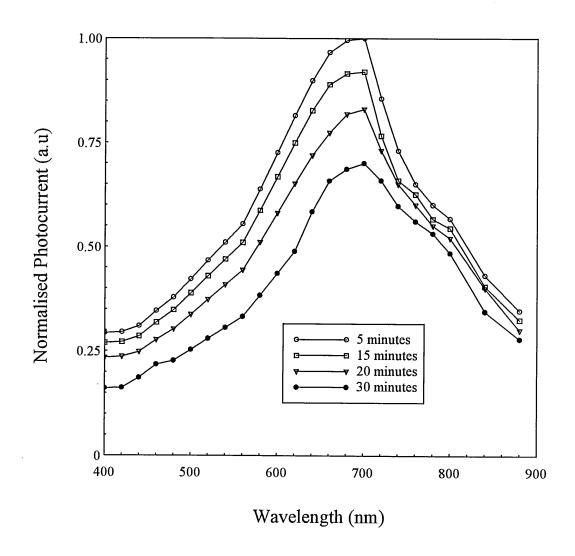

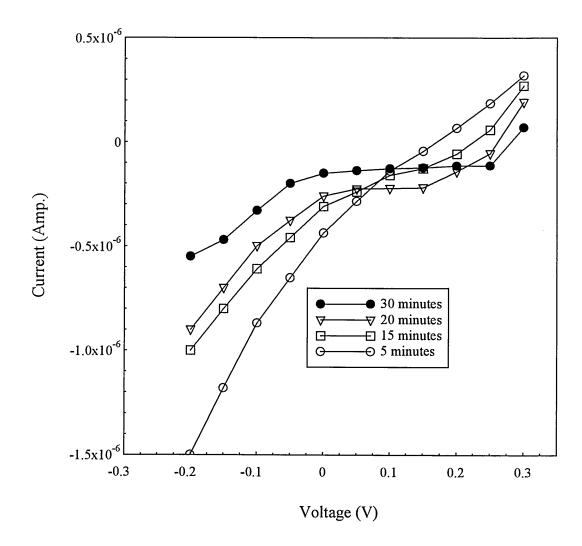

The dark d.c. electrical properties of PS have been widely studied, however much less data on the photoelectric properties are available. The photoconduction in PS layers studied to date has generally shown a clear widening in the energy band gap compared to crystalline silicon. Under negative bias, normalised photoconduction spectra at room temperature of a Au/PS/p-Si/Al structure shows that the peak wavelength shifts toward the lower energy side with increasing bias voltage. In contrast, the peak wavelength was found independent of the applied voltage for positive bias (Positive or negative bias voltage was applied to the Al contact with respect to the Au electrode) [Ozaki et al 1994]. Photoresponse spectra with a peak wavelength at 750 nm was observed by Pacebutas et al (1995). They also showed that the peak wavelength was independent on the resistivity of the silicon substrate. Similar results were also reported by Dinova-Malinovska et al (1997) for Zno/PS/p-Si/Al structure. Dafinei and Dafinei (1999) have also studied the electrical conductivity in PS under light at room temperature. They reported a red shift of the spectral response as the reverse bias increases. This behaviour was interpreted as a result of the increase of the band gap of PS and the existence of a heterojunction structure between PS and the silicon substrate. Also, Palsule et al (1997) found that the value of the peak of the photocurrent spectra depends mainly on the thickness of the PS layer, and the peak was observed at about 850 nm. On the other hand, Wang et al (1997) have reported a red shift in the photocurrent spectra as the anodisation current of the PS decreases. Peaks at 500nm were also reported for the photoconduction spectra of Au/PS/p-Si/Au structures.

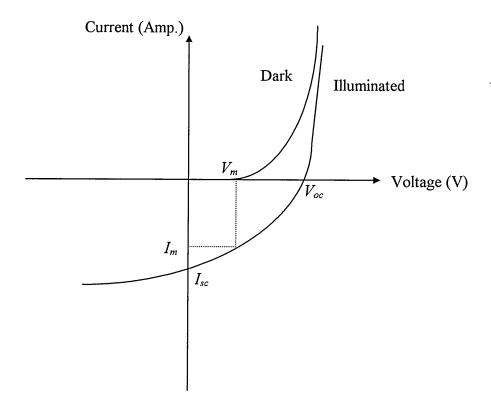

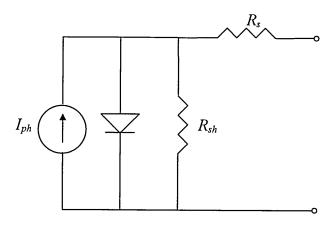

Photocurrent-voltage characteristics have been studied by different researchers. For all PS structures it was found that the short circuit current ( $I_{sc}$ ) and the open circuit voltage ( $V_{oc}$ ) increases with increasing illumination intensity. Under the optimum preparation conditions, Lee et al (1999) have found a short circuit current of about 4  $\mu$ A, and an open circuit voltage of about 0.52 V under tungsten lamp illumination of 24.4 mW/cm<sup>2</sup>. Similar values of  $I_{sc}$  and  $V_{oc}$  were also reported for different PS structures [Parkhutik 1999].

## 2.10 Practical applications of porous silicon

The stability and high resistivity of PS indicates its potential usefulness as an insulator. However, since the initial exploration of the PL and EL properties of PS at room temperature, there have been continuous interest in the technical development of the material in the field of optoelectronic devices [Balagurov et al 2000, Ciurea et al 1998, Gaburro et al 2000, Herino et al 1992, Koshida and Gelloz 1999, Martin-Palma et al 2000, Mikrajuddin et al 2000, Molnar et al 1999]. To date, PS in general is not utilised commercially as a light emitting device due to technical difficulties involved in the fabrication of the device. Lack of reproducibility, very short life time and low efficiency of the luminescence properties of PS are the difficulties faced by most of the groups engaged in the study of PL and EL properties of the material [Koshida and Koyama 1992].

However, the electrical and optical properties of PS were found to be changed by the presence of many gases such as methanol, ethanol, propanol, acetone, benzene, CO, and NO<sub>2</sub> [Angelucci et al 2000, Bilenko et al 2000, Boarino et al 200, Bogue

1997, Luth et al 2000, Schechter et al 1995, Thust et al 1999]. This phenomenon has been exploited to develop gas sensors for such gases. Schechter et al (1995) have used the PS conduction properties for organic vapour sensing (methanol and benzene vapours) and they found that the forward current amplitude rose with increasing vapour concentration for various thicknesses of PS layers. The increase in current was ascribed to the reduction of the PS layer resistance with increase of vapour concentration. Anderson et al (1990) and Schwarz et al (1995) have argued that the change in the electrical properties of PS is due to liquid condensation inside the microcapillaries of the PS. This leads to an extra current flowing through the liquid enhancing of conductivity. The activation energy was found to decrease due to the introduction of an organic vapour to the sample, but the conductivity pre-factor  $(\sigma_0)$  is not affected [Schechter et al 1995]. Under vacuum condition, a constant activation energy of (0.49 eV) was found over the temperature range of (200-300 K) indicating that the Fermi level is pinned at a fixed point with respect to the band edge. The exposure of the sample to organic vapours injects extra carriers into the PS and shifts the Fermi level to a new position closer to the band edge. Other researchers used the electronic properties of meso-PS samples for gas sensing [Ben-chorin et al 1994, Mares et al 1995]. The silicon structure in these samples are larger (mesoporous silicon) and therefore quantum size effects are negligable and allow the use of PS as a usual semiconductor [Goudeau et al 1989, Lehmann and Gösele 1991]. The main difference between mesoporous silicon and a crystalline silicon is the large surface area of the PS (more details will be discussed in chapter 4). Ben-chorin et al (1994) reported that the current-voltage profile of all PS samples is approximately symmetrical with respect to zero voltage for a vacuum or nitrogen atmosphere. For low benzene or methanol concentrations the behaviour remains ohmic with an increase

in current amplitude. Exposure of a PS device to a high concentration of an organic vapor makes the current-voltage characteristic tend to a rectifying behaviour. The change of the behaviour from ohmic to rectifying one was imputed to the electrical structure of the device which is described as a serial combination of a resistor (PS layer) with a pn junction (between PS and the silicon substrate). At low vapor concentrations, the PS resistance remains very high that it limits the current flow, resulting in ohmic current-voltage behaviour. At higher concentrations, the PS resistance is much reduced and the current in the reverse bias is limited by the pn junction, giving rise to rectifying current-voltage response. However, under forward bias, the limiting element is the PS resistance, and thus, the sensing characteristics should be measured with a forward bias.

Gas sensors for water vapour using PS have been also investigated [Anderson et al 1990, Foucaran et al 2000, Mares et al 1995, Motohashi et al 1995]. In all humidity sensors, the capacitance of the sensors was measured against humidity and found to increase with increasing humidity. This variation of capacitance with increasing humidity was related to the modification of the dielectric constant of the PS sample in the presence of water (as the dielectric constant of water is 80).

## **CHAPTER THREE**

# EXPERIMENTAL APPARATUS AND MEASUREMENTS TECHNIQUES

## 3.1 Introduction

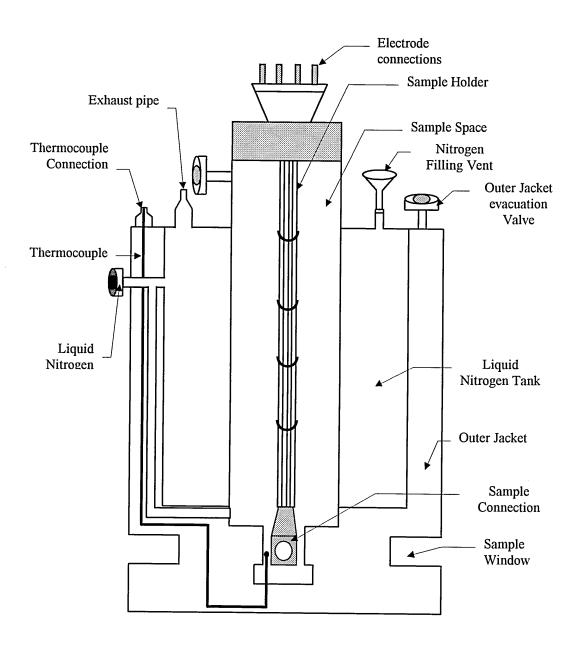

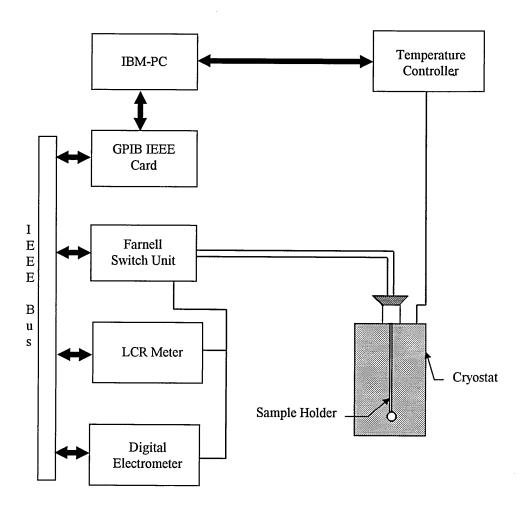

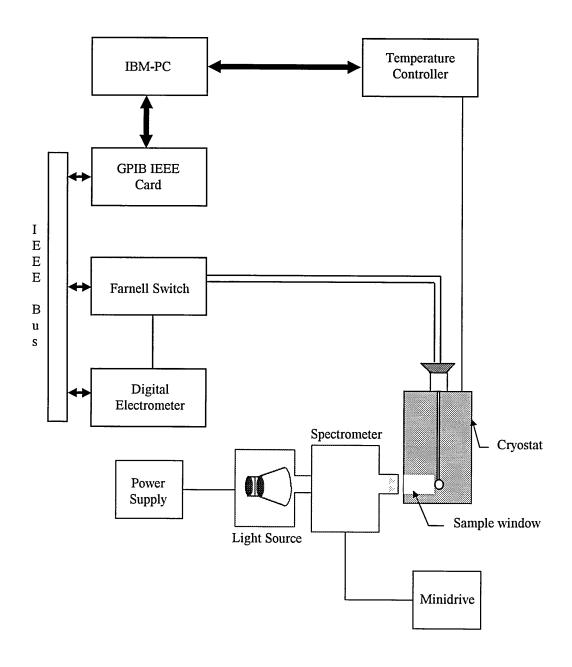

This chapter describes all the experimental work involved in this project. The first part of the chapter deals with the formation process of porous silicon (PS) including the fabrication setup for use in a clean room environment and the evaporation process used to deposit metal contacts on the PS layers and on the back side of the silicon substrates. Finally, the electrical and photoelectrical characterisation system is discussed briefly.

#### 3.2 Porous silicon formation

# 3.2.1 Design the fabrication setup

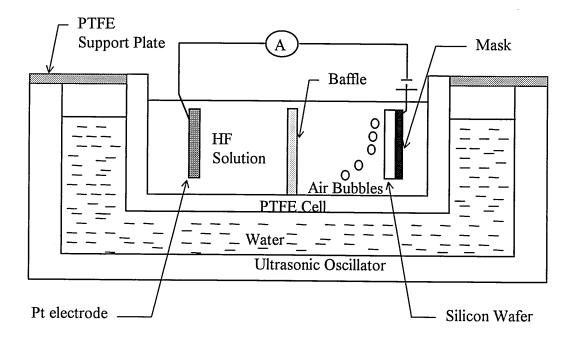

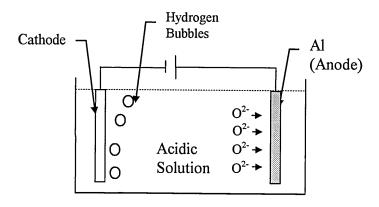

PS is made by anodic etching of silicon in hydrofluoric acid (HF). As silicon is not normally attacked by HF acid, it is necessary to apply an electrical voltage to achieve electrochemical desolution on the silicon surface. An electrochemical cell has been designed (by the author) for this purpose to accumulate silicon samples in the range up to 2 inch diameter. The cell is made from Teflon (PTFE) to be chemically resistant to the HF acid. The size of the cell is (85 mm (L) x 85 mm (W) x 70 mm (H)) which is attached from the upper edges to PTFE shoulders to provide support to the cell to be mounted inside an ultrasonic oscillator. The cell contains two electrodes (anode and cathode) each immersed in the HF acid and connected to an external current supply to

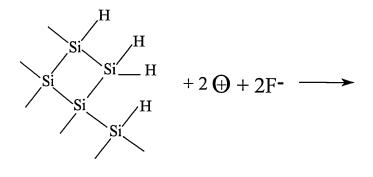

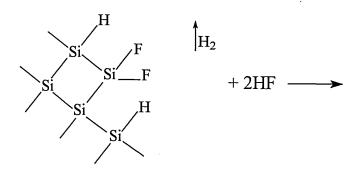

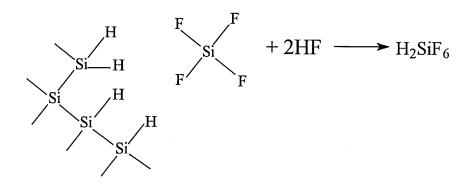

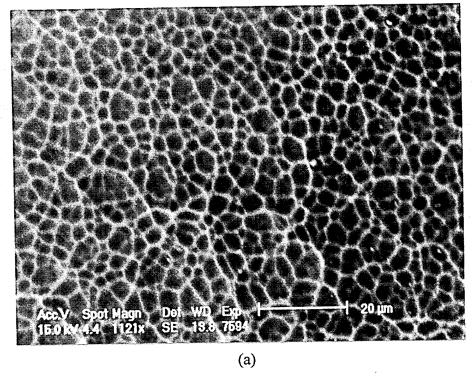

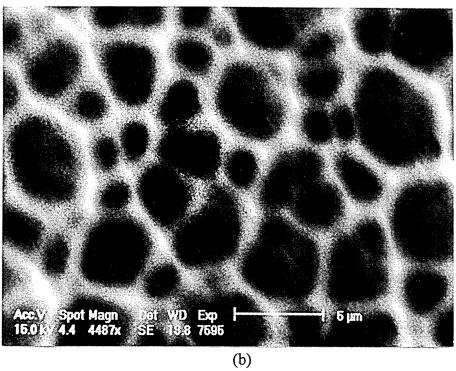

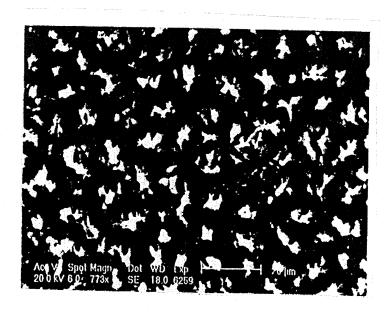

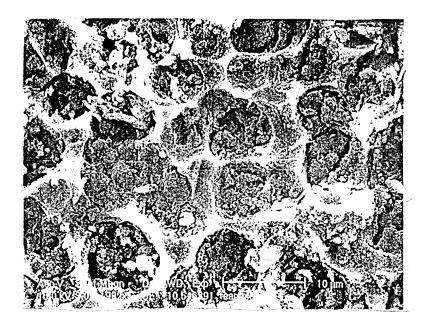

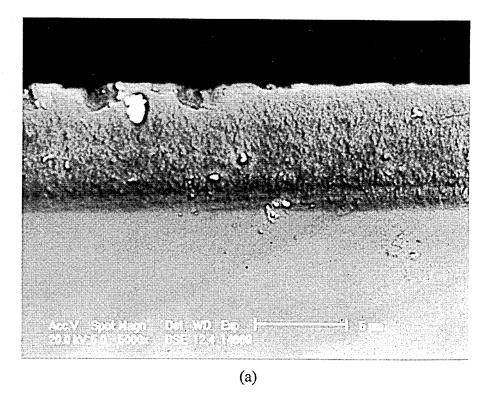

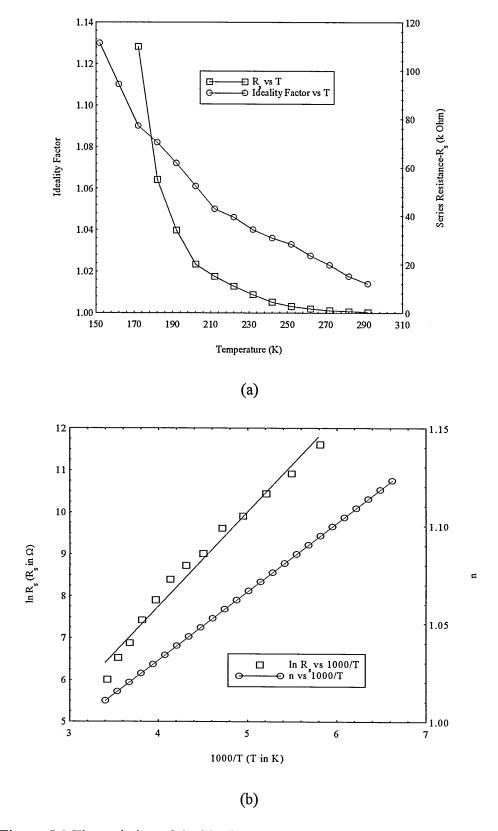

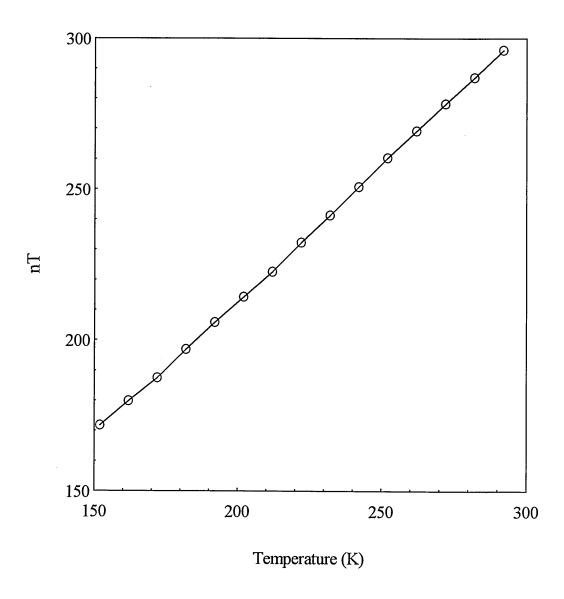

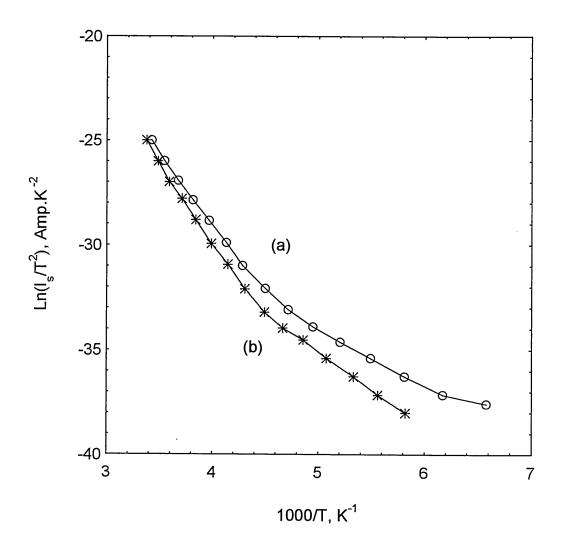

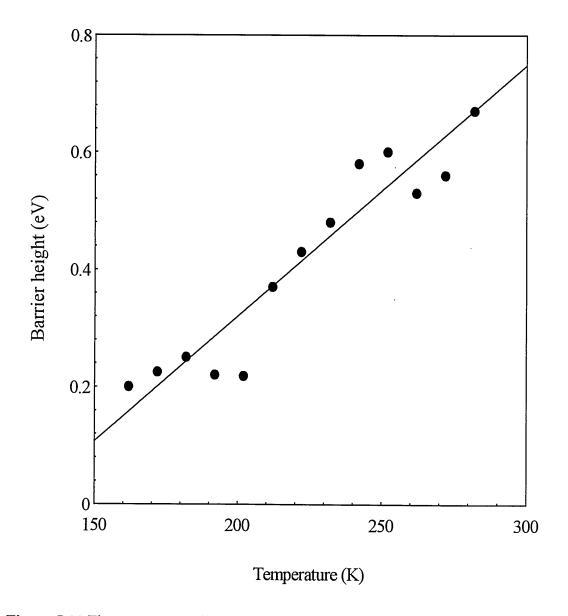

provide the current density required for the anodisation. Coiled platinum wire 200 mm in length and 0.5 mm in diameter is used as a cathode whilst the silicon wafer acts as an anode. The area of the platinum coil was chosen to be larger than the silicon wafer area (more than double) in order to give enough ionic exchange during the anodisation. A baffle plate (porous PTFE sheet) is fitted in the middle of the cell in order to control the speed of the ionic exchange between the electrodes which increases the electrochemical etching efficiency. This porous plate is usually used for etching with high current density and /or low HF acid concentration [Jung et al 1992, Richter et al 1992, Sugiyama and Nittono 1989, Takasha and Seki 1978,]. Figure 3.1 shows the schematic diagram of the fabrication setup designed and operated in the clean room.