A transputer based parallel database system.

GRAY, Jonathan Patrick.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/19717/

## A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/19717/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

100 312 436 4

13305

**Sheffield City Polytechnic Library**

# REFERENCE ONLY

Fines are charged at 50p per hour

28 1111 2004 4: 14ph ProQuest Number: 10697019

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10697019

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code

Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

## A Transputer Based Parallel Database System

by

### Jonathan Patrick Gray

A thesis submitted to the Council for National Academic Awards in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Sponsoring Establishment:

School of Computing and

Management Sciences,

Sheffield City Polytechnic

Collaborating Establishment: National Transputer Support Centre,

Sheffield

January 1991

#### Abstract

A sophisticated database application generation environment known as DB4GL has been developed at Sheffield City Polytechnic. A unique feature of DB4GL is the object-oriented application model used to specify and generate database applications. Although DB4GL has many advanced and powerful features, such as a self-describing data dictionary and extensive integrity rule processing facilities; the system has not been designed for high performance in either the generation tools or the generated database applications. The Parallel-DB4GL (P-DB4GL) project represents an attempt to improve the performance of the generated database applications, by constructing a new concurrent implementation of DB4GL for execution on transputer-based parallel hardware.

This thesis describes the DB4GL system as developed to the commencement of the P-DB4GL project. A prototype P-DB4GL system has been implemented that demonstrates how significant performance gains can be obtained from a concurrent implementation on transputer-based parallel hardware. Based on the successful results of this prototype system, designs for a fully functional multiprocessor P-DB4GL system are proposed. The details of this prototype and the fully functional designs are presented in this thesis. The thesis also provides an evaluation of the P-DB4GL project as a whole, and concludes with some suggestions for further research in the areas of parallel databases and object-oriented system implementation.

## Acknowledgements

I would like to take this opportunity to thank my supervisor, Professor Frank Poole, for the excellent supervision and encouragement he has given. In addition I would also like to thank Mrs Innes Jelly for her valuable comments in the preparation of this thesis and other reports. Finally I would like to thank Ms Susan Cleary for her assistance in typing, proof reading, and printing of this thesis.

## **Contents**

| Chapter 1  |                                                  |

|------------|--------------------------------------------------|

| Introducti | <u>on</u>                                        |

| 1.1        | Motivation for the Research1                     |

| 1.2        | Aims of the Research2                            |

| 1.3        | The P-DB4GL Approach3                            |

| 1.4        | P-DB4GL Project Development5                     |

| 1.5        | Outline of Thesis Contents6                      |

| Chapter 2  |                                                  |

| The DB4G   | L Database Application Generation System         |

| 2.1        | DB4GL Project Overview10                         |

| 2.2        | Application Generation and Prototyping10         |

| 2.3        | DB4GL Application Development11                  |

| 2.4        | The DB4GL Application Model12                    |

|            | 2.4.1 A Generic Architecture12                   |

|            | 2.4.2 Presentation Objects                       |

|            | 2.4.3 Information Units14                        |

|            | 2.4.4 Data Relationships15                       |

|            | 2.4.5 Levels of Data Description16               |

| 2.5        | Implementation of the Application Model16        |

| Chapter 3  |                                                  |

| Object-Ori | ented Database Approaches                        |

| 3.1        | A Classification of Object-Oriented Approaches30 |

| 3.2        | Object-Oriented Approaches and DB4GL32           |

| Chapter 4  |                                                  |

| Transpute  | rs, Occam, and Databases                         |

| 4.1        | Transputers38                                    |

| 4.2        | Occam38                                          |

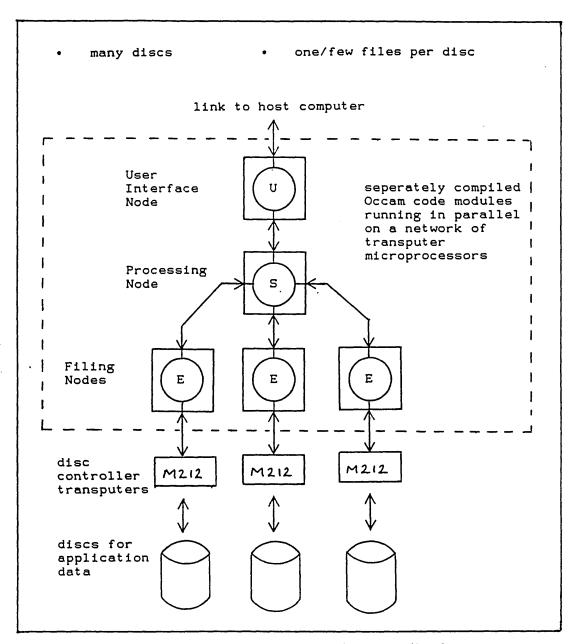

| 4.3        | Transputers and Databases                        |

| 4.4        | Project Resources42                              |

| Chapter 5  |                                                  |

| Developin  | g the Prototype Parallel-DB4GL                   |

| 5.1        | Project Objectives45                             |

| 5.2        | Design Methodology45                             |

| 5.3        | Development Approach46                           |

| 5.4         | Implementation                                | 47         |

|-------------|-----------------------------------------------|------------|

| 5.5         | Testing                                       | 51         |

| 5.6         | Results                                       | 53         |

| 5. <i>7</i> | Evaluation                                    | 54         |

| Chapter 6   | 5                                             |            |

| Designs f   | or a Fully Functional P-DB4GL                 |            |

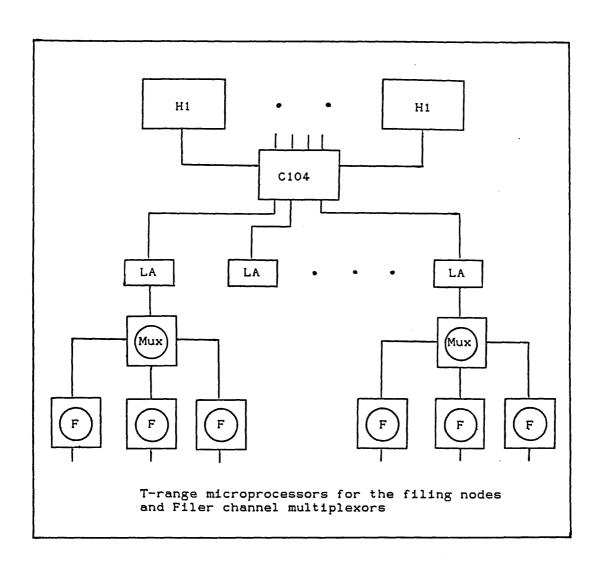

| 6.1         | A Multiprocessor Fully Functional P-DB4GL     | 67         |

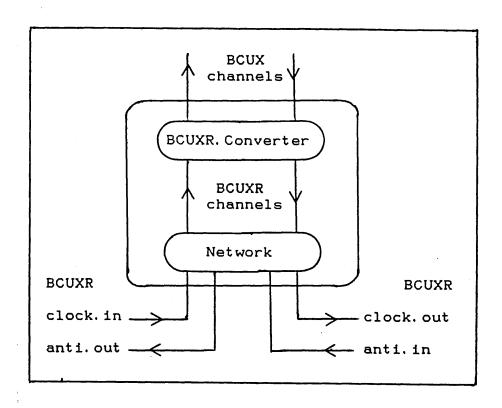

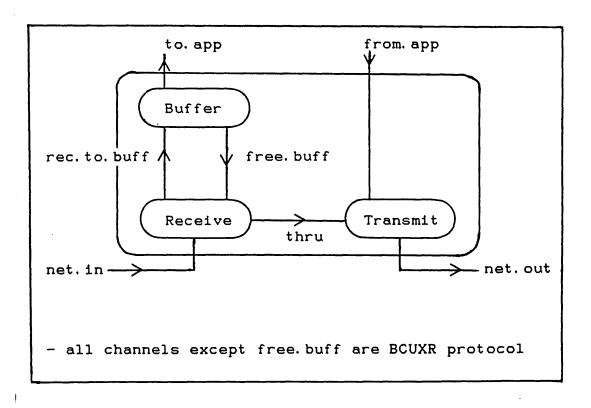

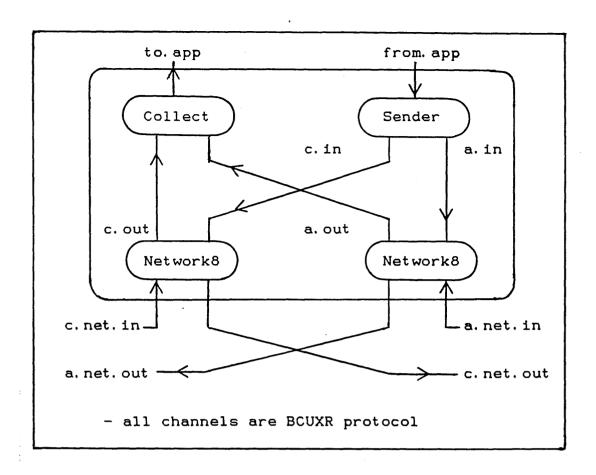

| 6.2         | Channel Multiplexors and Message Routers      | 68         |

|             | 6.2.1 Channel Multiplexing                    | 68         |

|             | 6.2.2 P-DB4GL Channel Multiplexors            | 69         |

|             | 6.2.3 P-DB4GL Message Routing                 | <b>7</b> 0 |

| 6.3         | Communication Loads and Protocol Overheads    | 72         |

| 6.4         | Designs for P-DB4GL Hardware Configurations   | 75         |

| 6.5         | Code Factoring                                | 77         |

| 6.6         | Code Generation                               | 78         |

| Chapter 7   | 7                                             |            |

| P-DB4GL     | Project Evaluation                            |            |

| 7.1         | Summary                                       | 90         |

| 7.2         | Communication Loads and Object Clustering     | 90         |

| 7.3         | Object Inheritance                            | 91         |

| 7.4         | Occam 2 as an Implementation Language         | 91         |

| <b>7.</b> 5 | Improvements in Secondary Storage Technology  | 92         |

| 7.6         | The Next Generation of Transputer Products    | 93         |

| 7.7         | Advantages of a Prototyping Development Cycle | 95         |

| Chapter 8   | <b>}</b>                                      |            |

| Conclusion  | ons                                           | 97         |

| Bibliograp  | phy                                           | 99         |

| Appendic    | <u>ces</u>                                    |            |

| Appendix    | A - Algorithm Syntax Definition               | 110        |

| Appendix    | B - Message Formats and Occam Channels        | 11         |

|             | C - Entity and Schema Handler Algorithms      |            |

|             | D - Disc and Filer Algorithms                 |            |

|             | E - Filer Harness Specification               |            |

|             | F - User Process Test Harness                 |            |

| Appendix    |                                               |            |

| Appendix H - Test Results                              | 151 |

|--------------------------------------------------------|-----|

| Appendix I - Test Application Performance Optimization |     |

| Appendix J - Routers and Multiplexors                  | 176 |

| Appendix K - System Constants                          | 192 |

| Appendix L - Channel Protocols                         |     |

## **List of Figures**

| Figure 1.1 - Thesis Contents                                       |            |

|--------------------------------------------------------------------|------------|

| Figure 2.1 - DB4GL Development Environment                         | 18         |

| Figure 2.2 - Information for Application Specification             | 19         |

| Figure 2.3 - DB4GL Application Model                               | 20         |

| Figure 2.4 - Database Applications as Instantiations               | 21         |

| Figure 2.5 - Examples of Application Structures                    | 22         |

| Figure 2.6 - Data Dependencies and Object Activity                 | 23         |

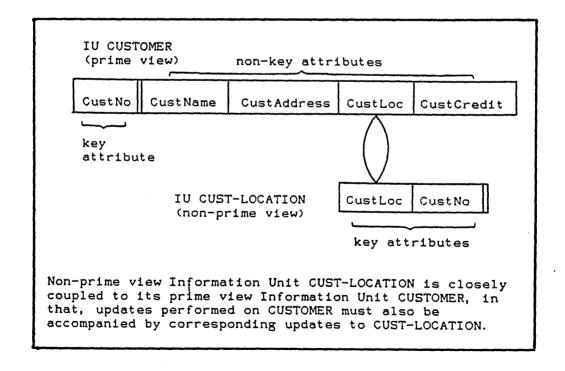

| Figure 2.7 - Prime View and Non-prime View Information Units       | 23         |

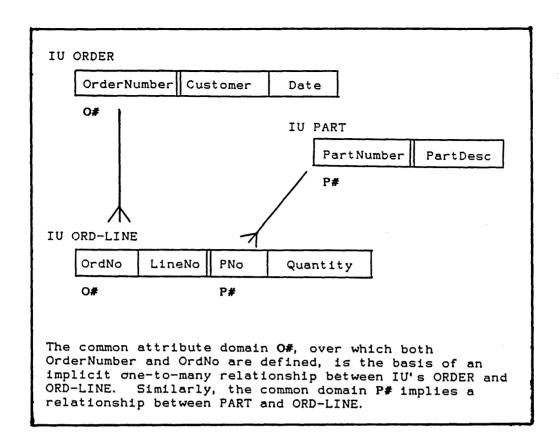

| Figure 2.8 - Domains and Relationships                             | 24         |

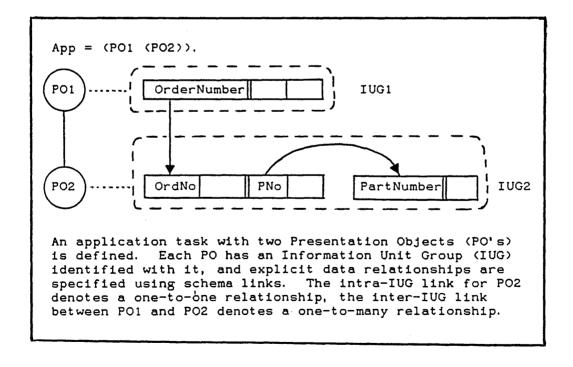

| Figure 2.9 - Information Unit Groups and Schema Links              | 24         |

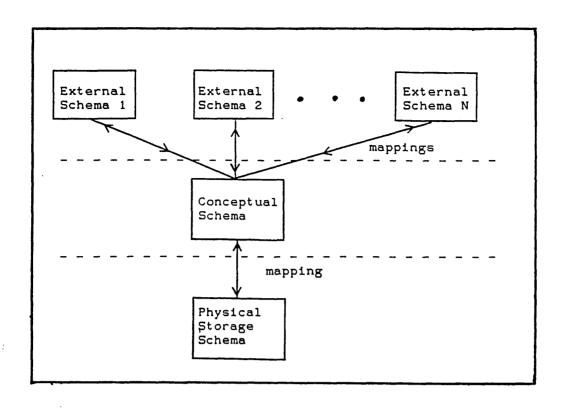

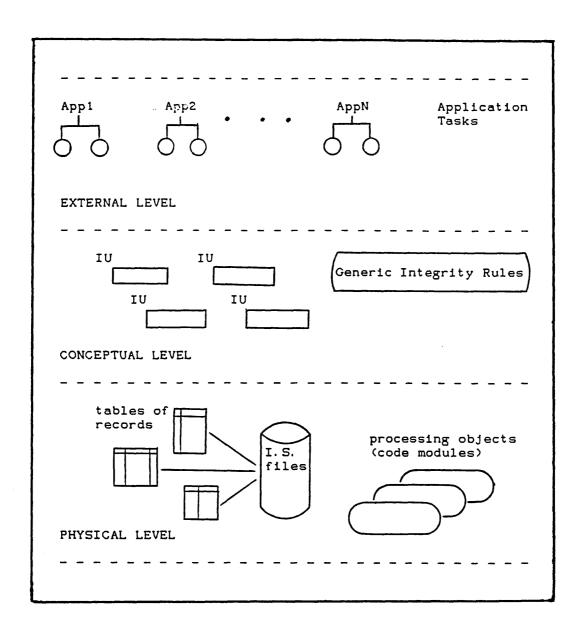

| Figure 2.10 - ANSI/SPARC DBMS Model                                | 25         |

| Figure 2.11 - Levels of DB4GL Data Description                     | 26         |

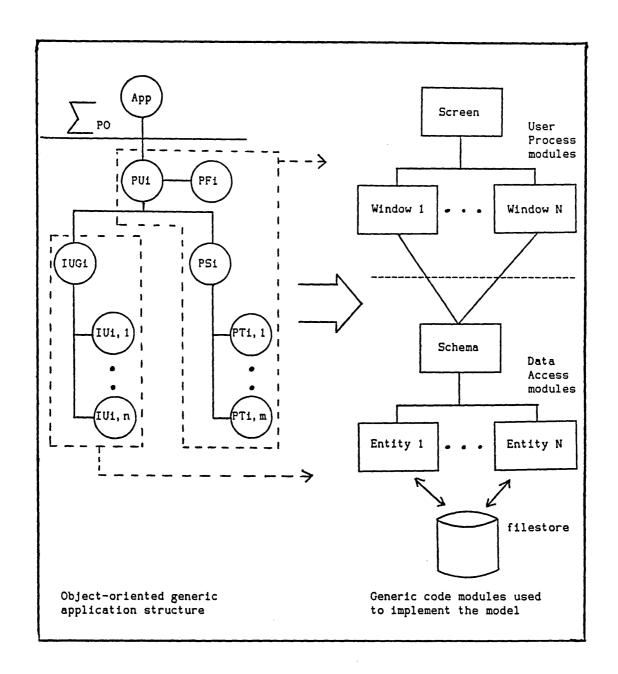

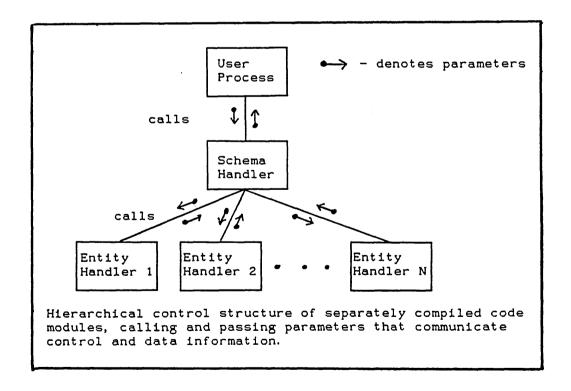

| Figure 2.12 - Implementation of the Application Model              | 27         |

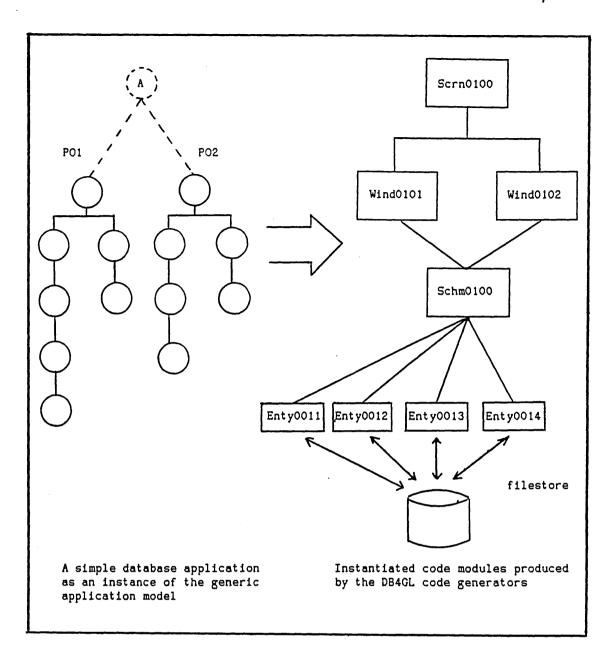

| Figure 2.13 - Generated Application Instances                      | <b>2</b> 8 |

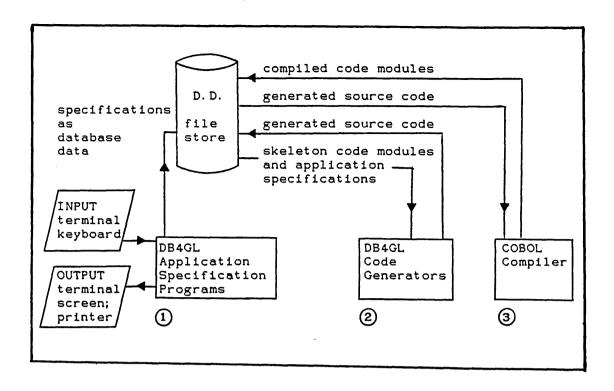

| Figure 2.14 - DB4GL Code Generation                                | 29         |

| Figure 2.15 - Modular Structure of Implemented Applications        | 29         |

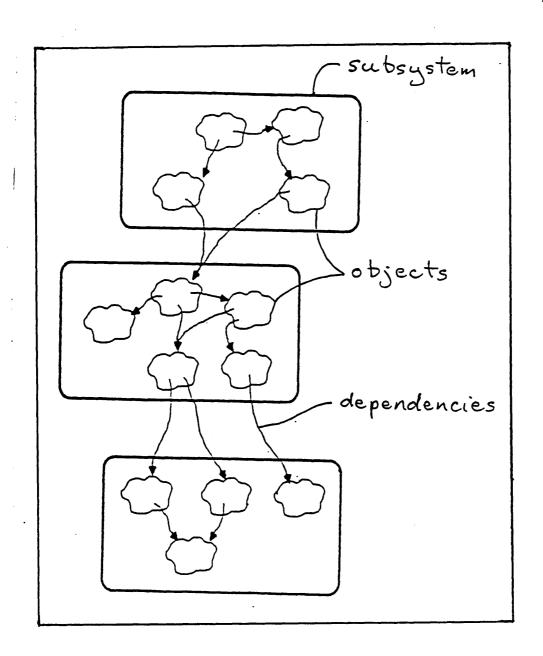

| Figure 3.1 - An Object-Oriented Design                             | 36         |

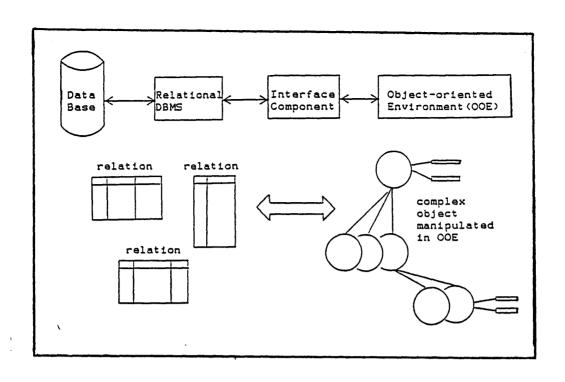

| Figure 3.2 - DBMS/Object-Oriented Environment Interface            | 37         |

| Figure 4.1 - Transputer Architecture                               | 43         |

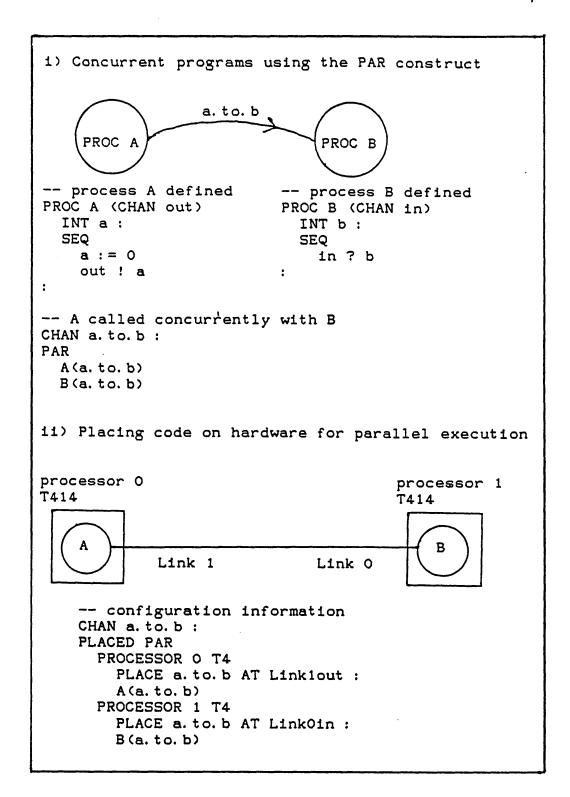

| Figure 4.2 - The Occam Language                                    | 44         |

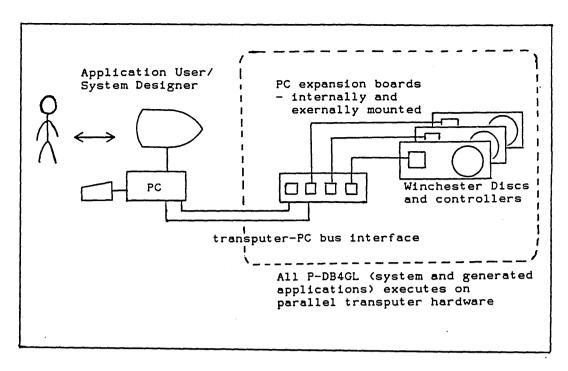

| Figure 5.1 - System Configuration for P-DB4GL                      | 58         |

| Figure 5.2 - Concurrent Message Passing Processes                  | 58         |

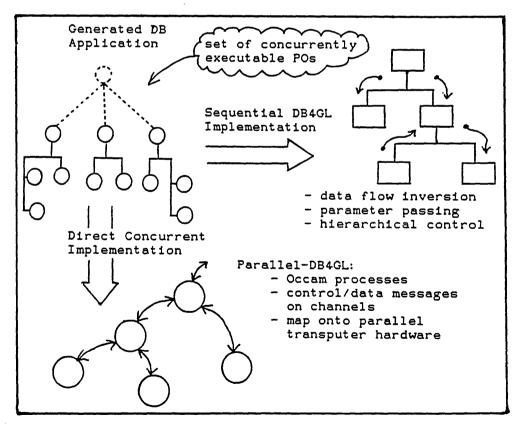

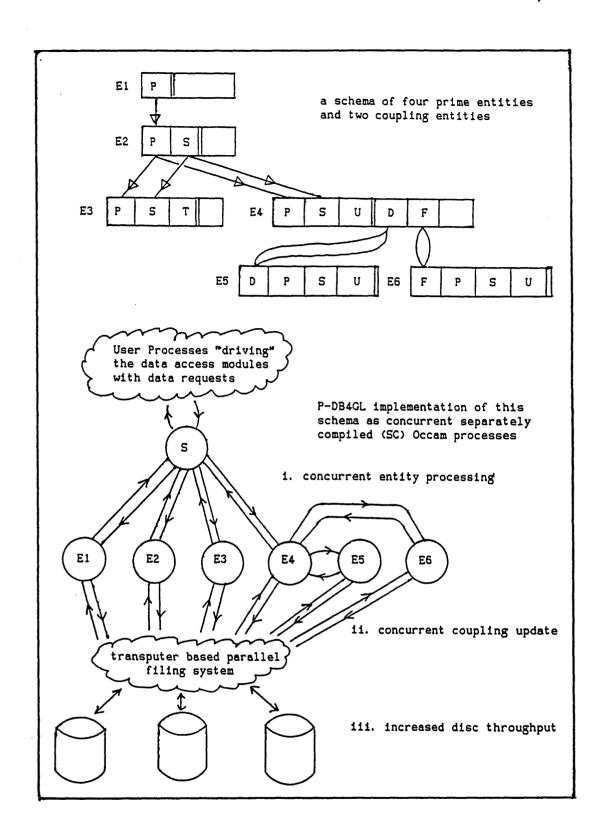

| Figure 5.3 - Typical P-DB4GL Database Application                  | 59         |

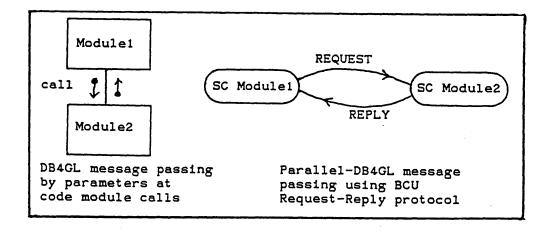

| Figure 5.4 - DB4GL and P-DB4GL Message Passing                     | 59         |

| Figure 5.5 - Concurrent Execution of Data Access Processes         | 60         |

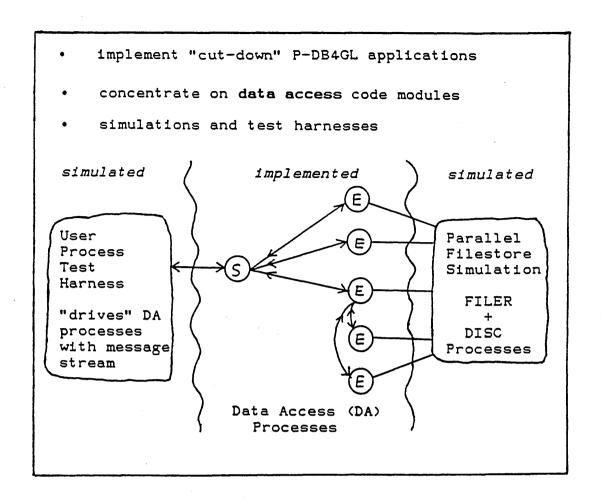

| Figure 5.6 - Developing the Prototype P-DB4GL System               | 61         |

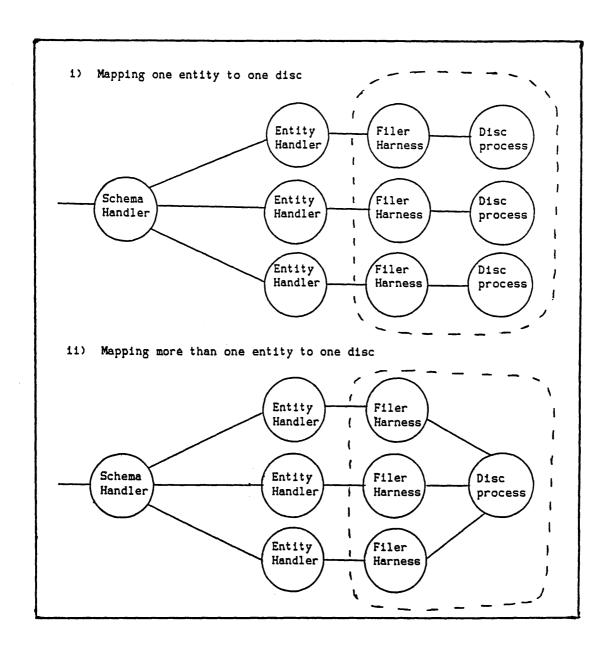

| Figure 5.7 - Mapping Entity Handlers to Discs                      | 62         |

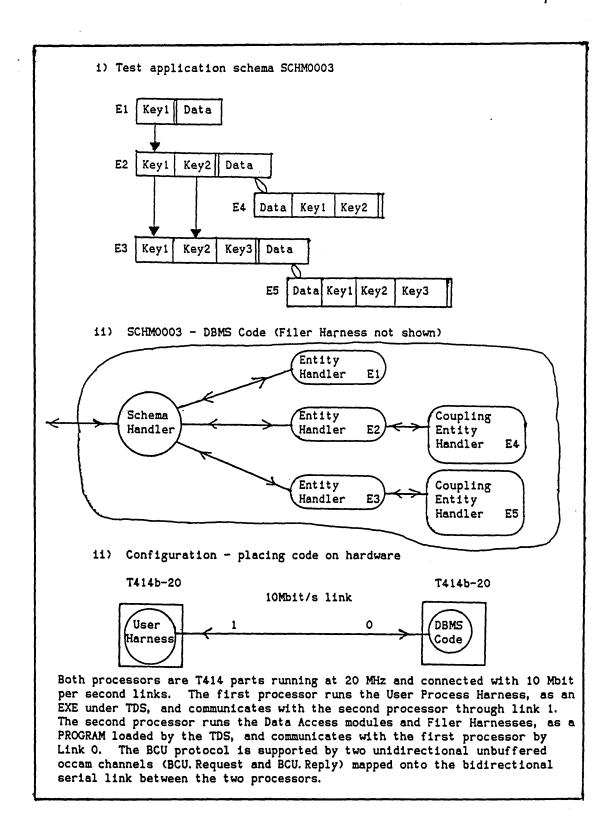

| Figure 5.8 - Typical Test Application Configuration                | 63         |

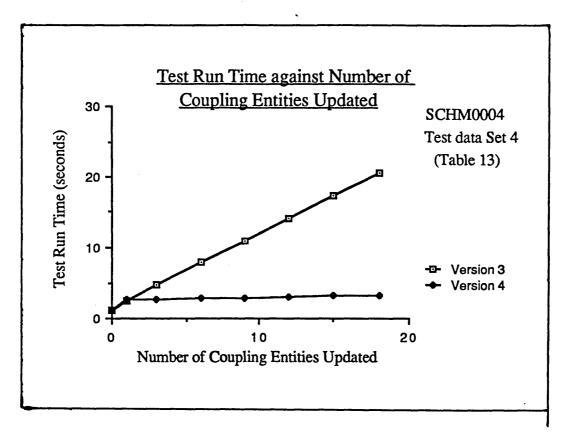

| Figure 5.9 - Version 4 Handlers Test Run Times                     | 64         |

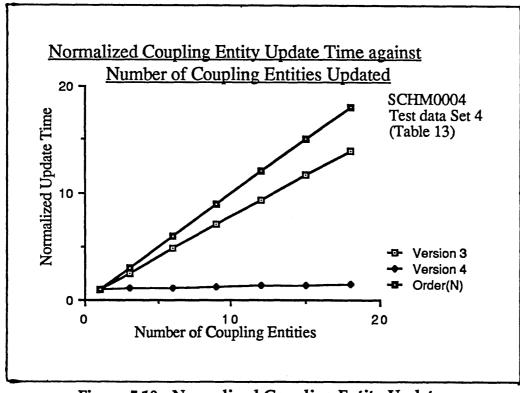

| Figure 5.10 - Normalized Coupling Entity Update                    | 64         |

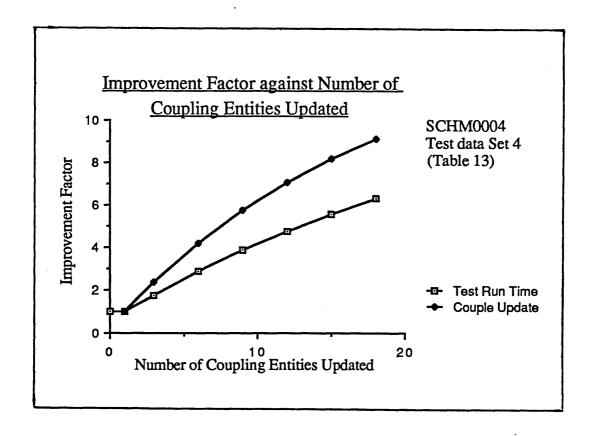

| Figure 5.11 - Version 4 Handlers Improvement Factor                | 65         |

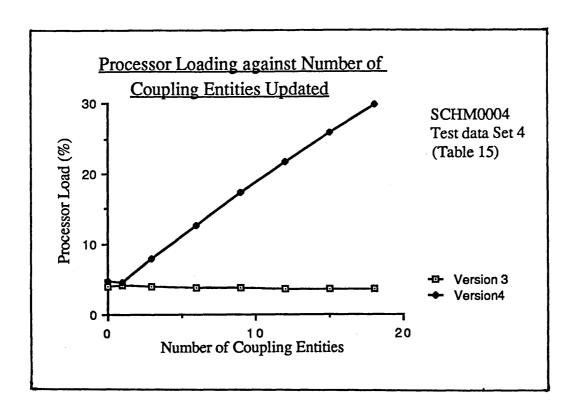

| Figure 5.12 - Test Run Processor Loading                           | 65         |

| Figure 5.13 - Processing/Disc Access Ratio                         | 66         |

| Figure 5.14 - Processor Loading and Parallel Configuration         | 66         |

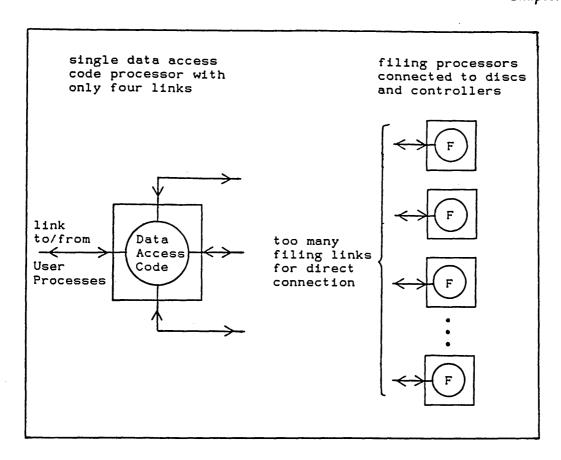

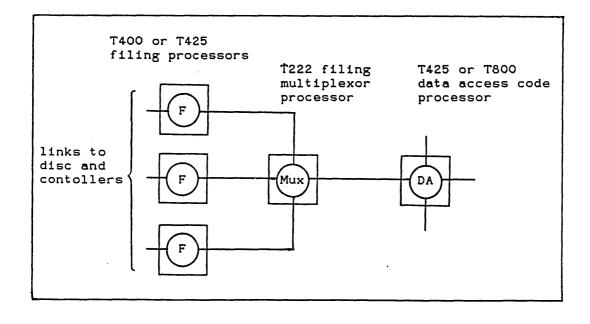

| Figure 6.1 - Insufficient Links for Filer Connection               |            |

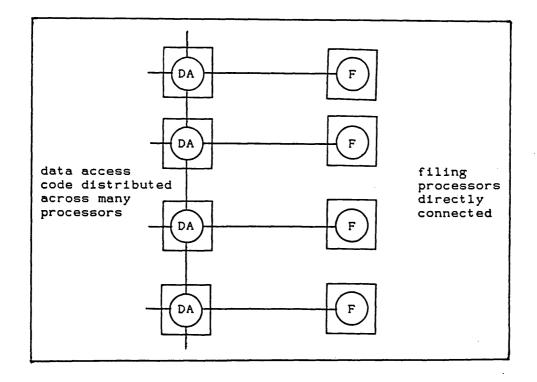

| Figure 6.2 - Distributing the Data Access Code                     |            |

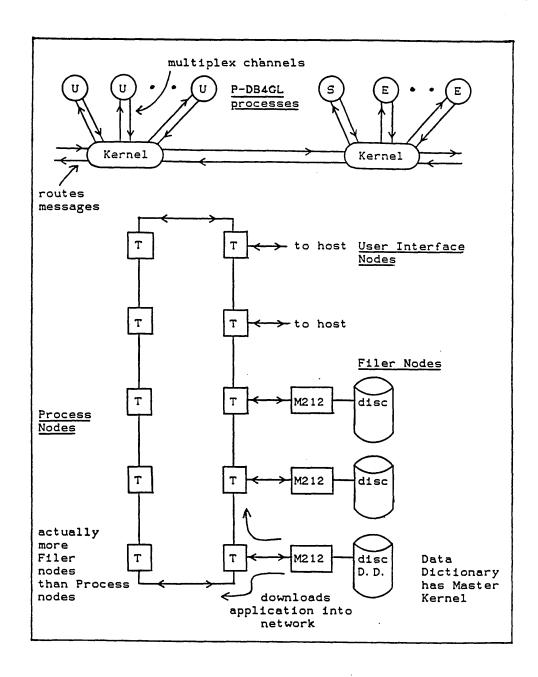

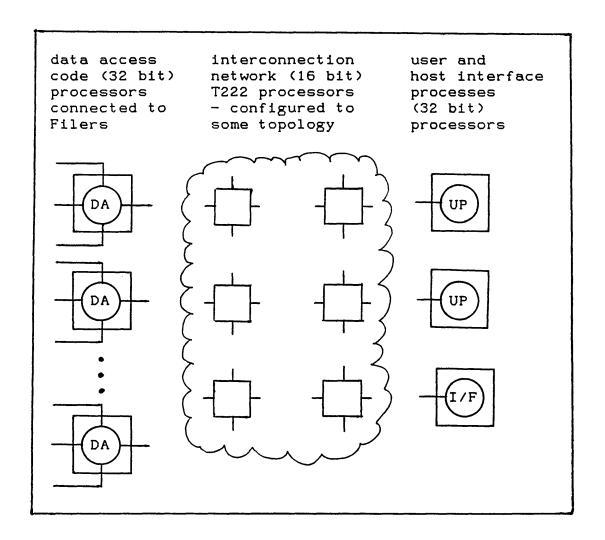

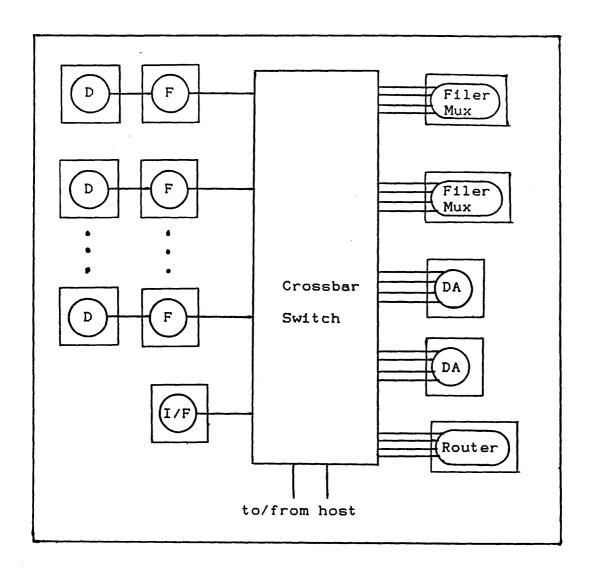

| Figure 6.3 - Designs for a Fully Functional Multiprocessor P-DB4GL |            |

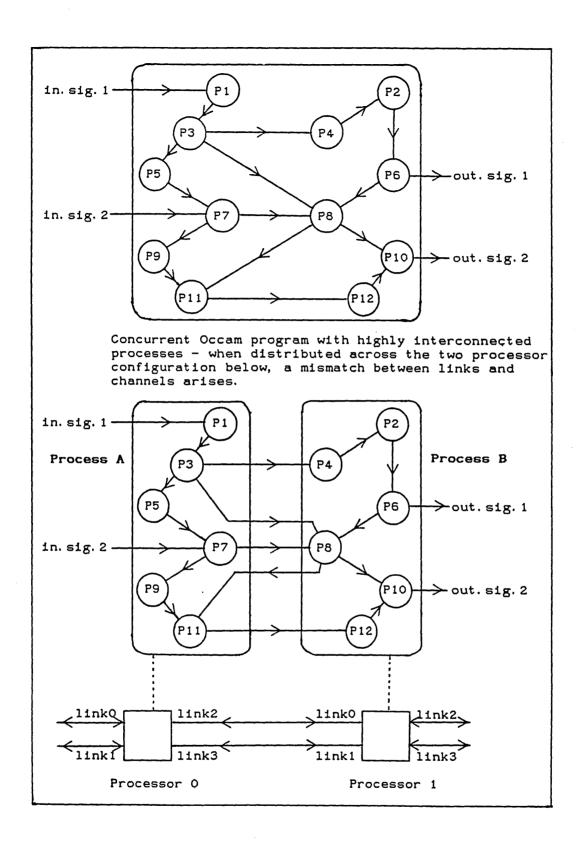

| Figure 6.4 - Configuration Mismatch Between Channels and Links     |            |

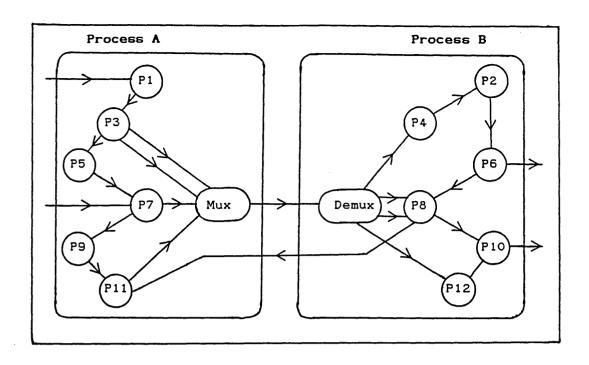

| Figure 6.5 - Addition of Multiplexor Processes                  | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

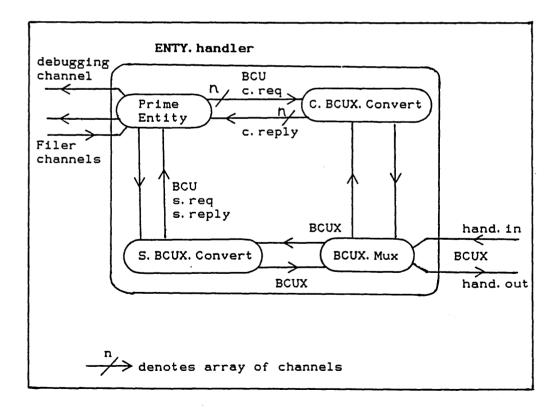

| Figure 6.6 - Modified Prime Entity Handler                      | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

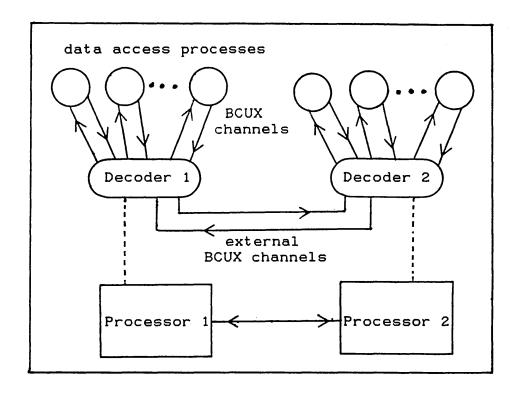

| Figure 6.7 - P-DB4GL Decoder Process                            | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

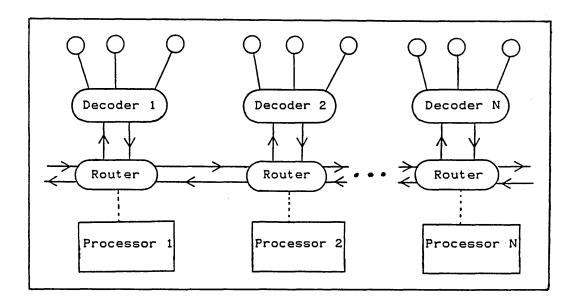

| Figure 6.8 - Routing Messages Through a P-DB4GL Network         | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

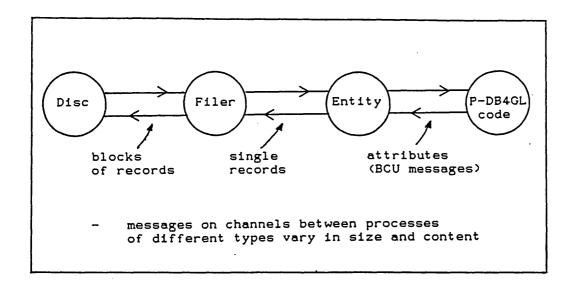

| Figure 6.9 - Different Types of P-DB4GL Messages                | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 6.10 - Multiplexing Filer Channels                       | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 6.11 - A Separate Interconnection Network                | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 6.12 - A Reconfigurable Network                          | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

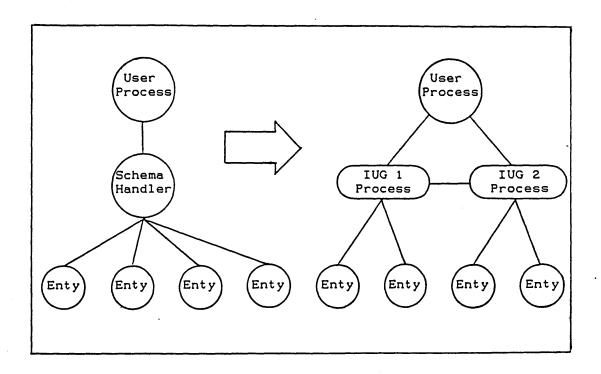

| Figure 6.13 - Replacement of Schema Handler by IUG Process      | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 6.14 - An Alternative Presentation Object Implementation | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 6.15 - Methods of Code Generation                        | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 7.1 - An H1 Based P-DB4GL Design                         | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure B1 - P-DB4GL Message Formats                             | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

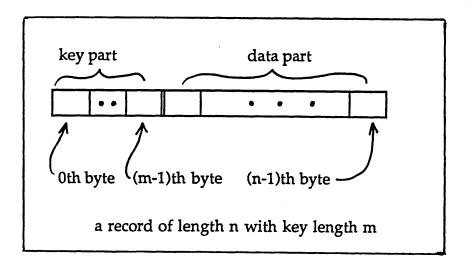

| Figure E1 - Filer Harness Record Representation                 | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure F1 - A Single Transaction                                | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure F2 - Optimised Sequence of Transactions                  | 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

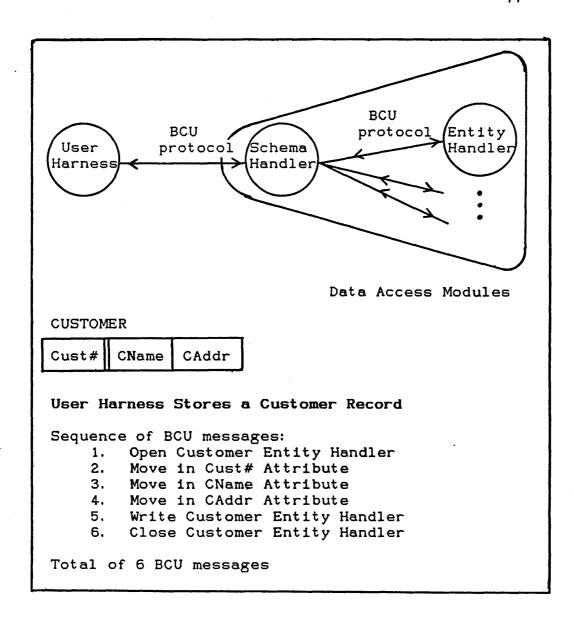

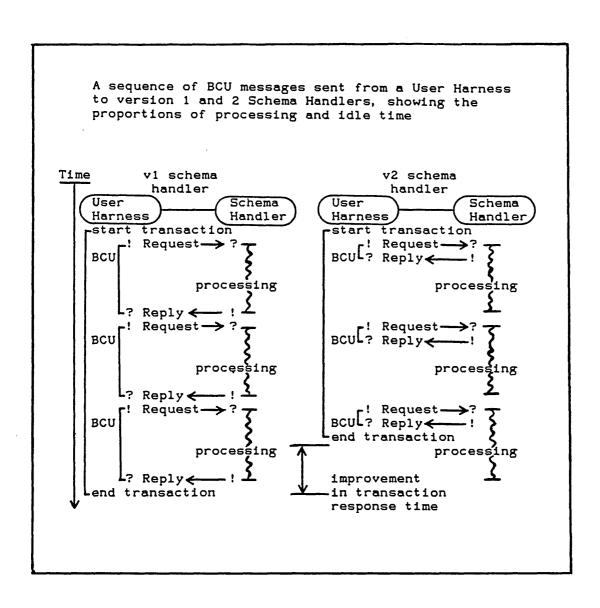

| Figure F3 - A Sequence of BCU Messages                          | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

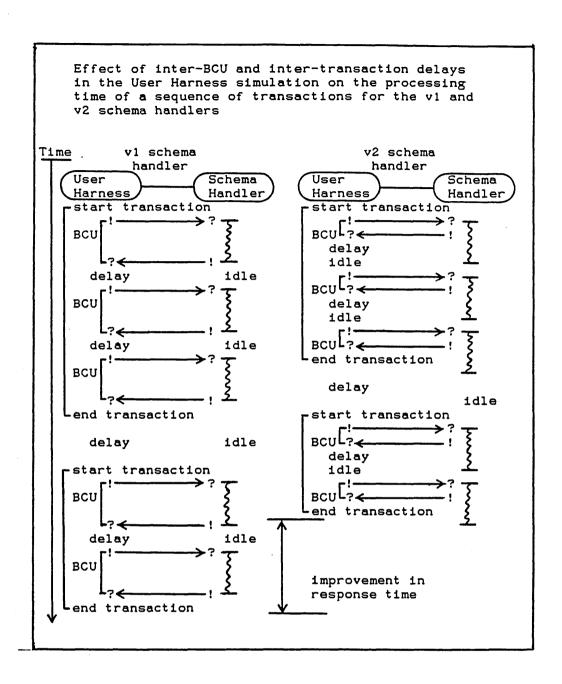

| Figure F4 - Effect of User Harness Delays                       | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

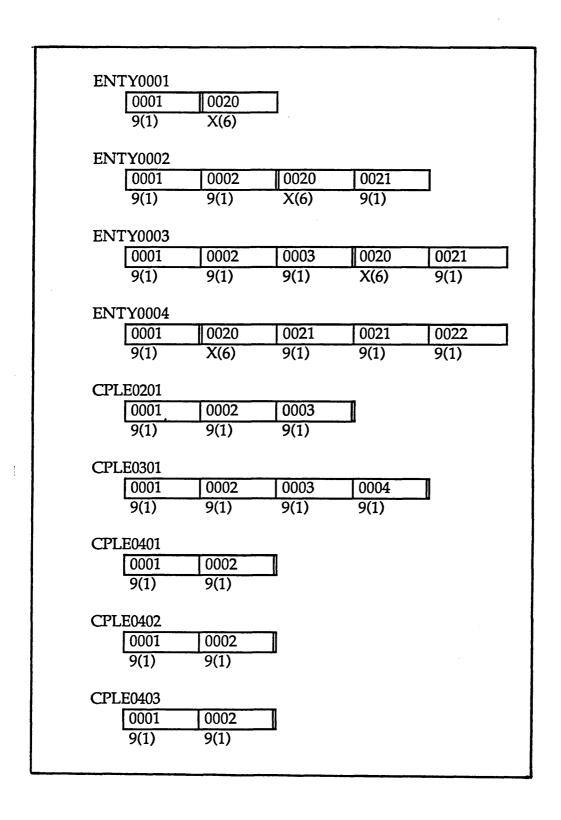

| Figure G1 - Test Entities (Information Units)                   | 147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

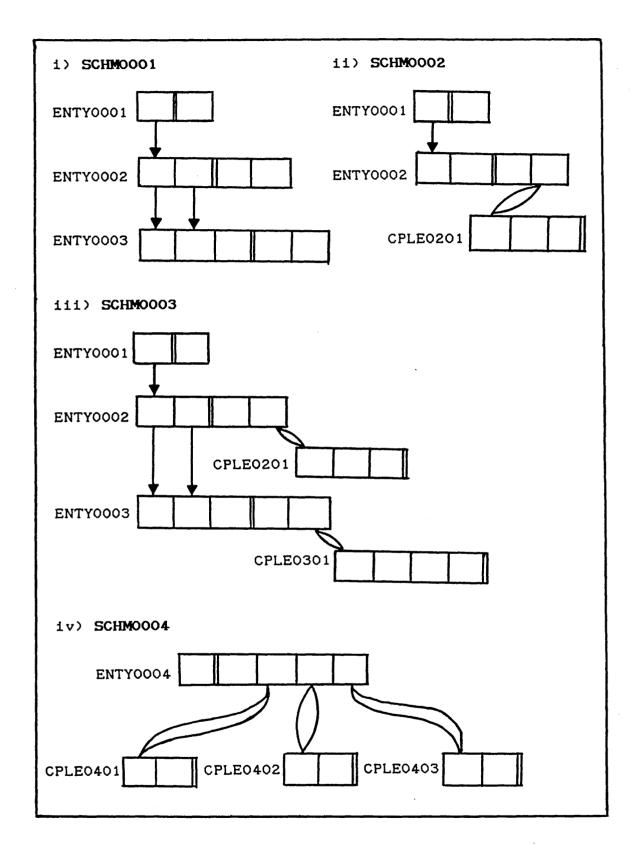

| Figure G2 - Test Schemas                                        | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

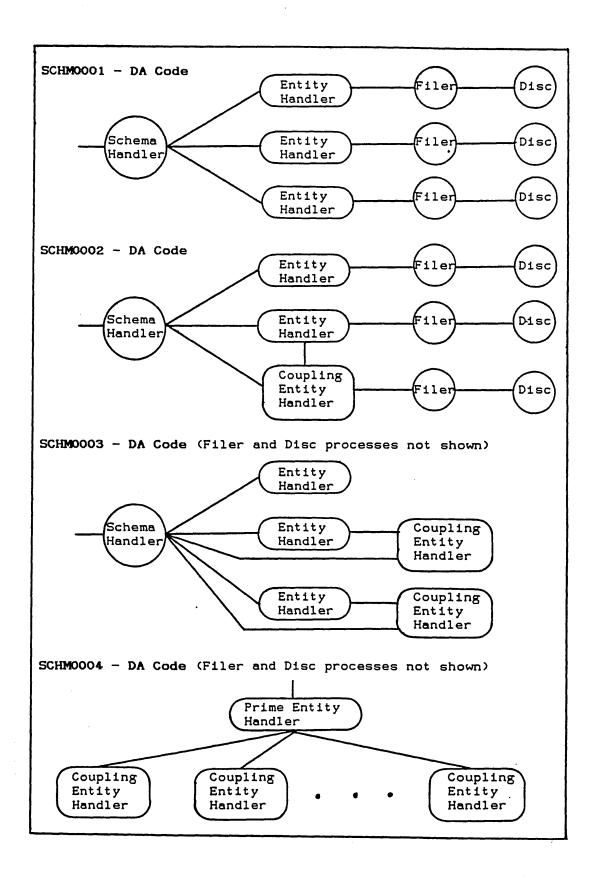

| Figure G3 - Test Data Access Code                               | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

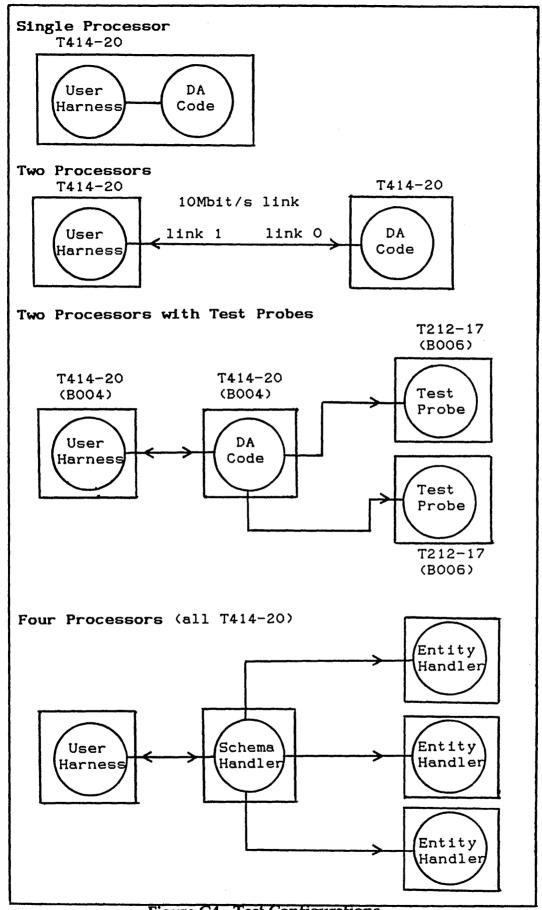

| Figure G4 - Test Configurations                                 | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

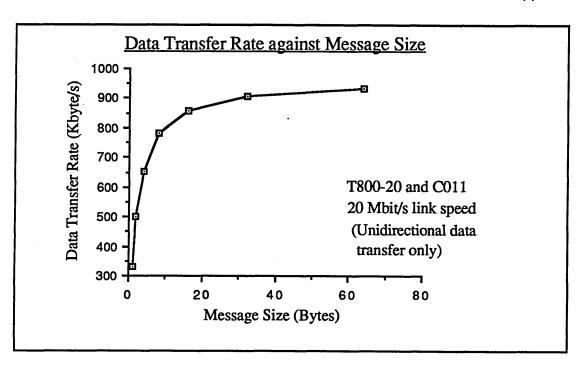

| Figure I1 - Effect of Message Size on Transfer Rate             | 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

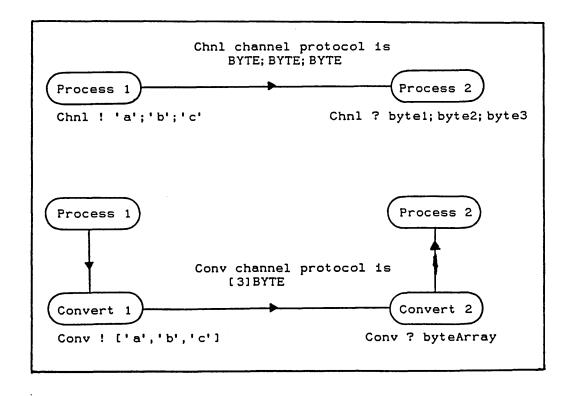

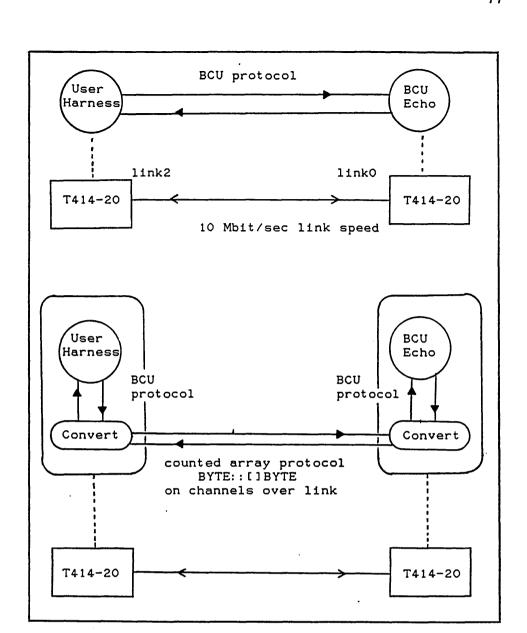

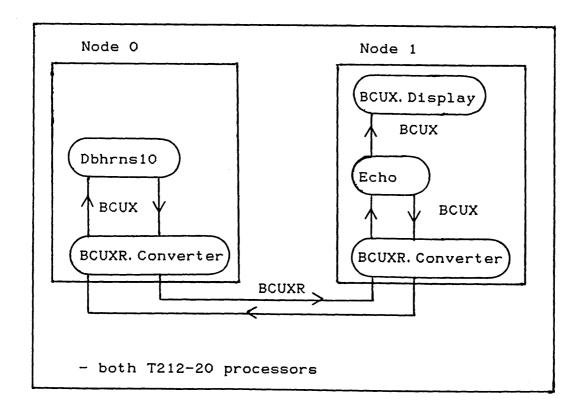

| Figure I2 - Channel Protocol Converter Processes                | 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure I3 - Protocol Conversion Test Configuration              | 175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

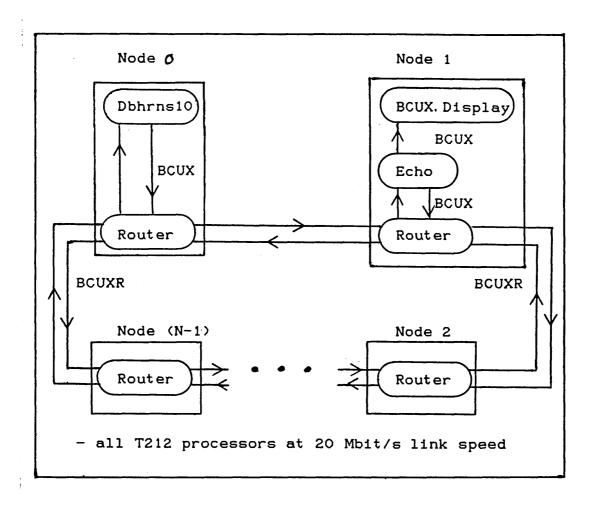

| Figure J1 - P-DB4GL Router Process                              | 188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure J2 - Network8 Ring Router Process                        | 188                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure J3 - Network9 Ring Router Process                        | 189                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

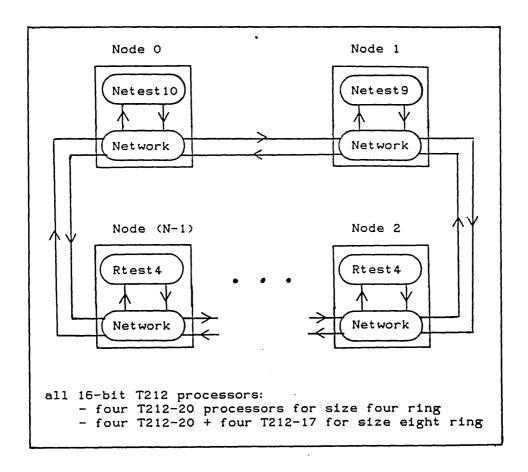

| Figure J4 - Net16 Ring Routing Test Configuration               | 190                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure J5 - Net18 Ring Routing Test Configuration               | 190                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure J6 - Net19 Ring Routing Test Configuration               | 191                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                 | Figure 6.6 - Modified Prime Entity Handler Figure 6.7 - P-DB4GL Decoder Process Figure 6.8 - Routing Messages Through a P-DB4GL Network Figure 6.9 - Different Types of P-DB4GL Messages. Figure 6.10 - Multiplexing Filer Channels Figure 6.11 - A Separate Interconnection Network Figure 6.12 - A Reconfigurable Network Figure 6.13 - Replacement of Schema Handler by IUG Process. Figure 6.14 - An Alternative Presentation Object Implementation Figure 6.15 - Methods of Code Generation Figure 7.1 - An H1 Based P-DB4GL Design Figure B1 - P-DB4GL Message Formats. Figure E1 - Filer Harness Record Representation Figure F2 - Optimised Sequence of Transactions Figure F3 - A Sequence of BCU Messages Figure F4 - Effect of User Harness Delays Figure G1 - Test Entities (Information Units) Figure G2 - Test Schemas. Figure G3 - Test Data Access Code Figure G4 - Test Configurations Figure I1 - Effect of Message Size on Transfer Rate. Figure I2 - Channel Protocol Converter Processes Figure J3 - Network9 Ring Router Process Figure J4 - Net16 Ring Routing Test Configuration Figure J5 - Net18 Ring Routing Test Configuration Figure J5 - Net18 Ring Routing Test Configuration |

## Chapter 1

#### Introduction

#### 1.1 Motivation for the Research

This PhD thesis describes the work undertaken and results obtained from the Parallel DB4GL (P-DB4GL) research project. The P-DB4GL project is an extension of continuing research at Sheffield City Polytechnic in the areas of databases and automated systems development. During recent years several research projects concerned with data dictionaries, 4th Generation Languages (4GL's), and application prototyping have been undertaken at the Polytechnic [Cooper83] [Beazley84] [Ewin84] [Bal85] [Priti86] [Kilo86]]; culminating in the development of a sophisticated database application generation environment known as DB4GL (Data Base 4th Generation Language) [Ewin85a] [Ewin85b] [Poole87] [Hird89].

The DB4GL research was motivated chiefly by concerns of improving programmer productivity and automating software development. DB4GL, like many 4GL's, exists as a collection of productivity enhancing tools [Nelson85]. These tools, such as data dictionaries, normalization engines, screen painters, report generators, and code generators, are used by system analyst/designers and programmers to improve efficiency and shorten development time in the traditional software system development cycle, or "waterfall" life cycle [Boehm76], of analysis-specification-design-implementation-testing [Cobb85] [Forage85]. Such 4GL tools can also be used to rapidly build, or "prototype", applications in a modified software development cycle [Brittan80] [McCraken82] [Appleton83] [Johnson83].

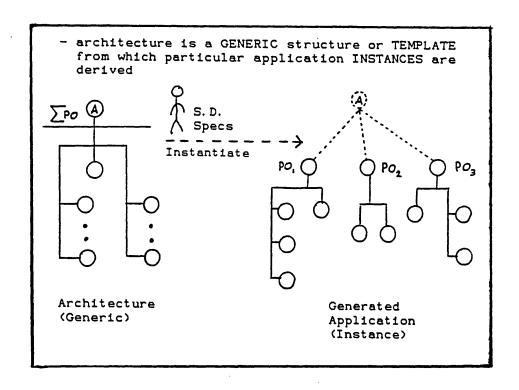

DB4GL represents an attempt to create a unifying ordered approach to the construction of database-oriented information systems (or database applications) within the context of a prototyping system development methodology. DB4GL integrates both processing and information descriptions, combined with rule-based integrity constraints, in a formal homogeneous object-oriented structure known as the DB4GL application model. This application model is fundamental to the generation of database applications; it is a generic structure, or template, from which generated applications are derived. Generated database applications are defined as specific instances of this generic structure.

The DB4GL generated database applications, and the DB4GL tools themselves, have not been designed with performance in mind. Some of the DB4GL tools, the generator tools in particular, are very slow in operation. The compiled program code that constitutes the generated DB4GL applications is slow in execution, and could have been more efficiently designed and coded. Because DB4GL has been developed as a research vehicle rather than a commercial product, performance issues have not been a major concern. Fortunately, DB4GL is fully portable to any system supporting a COBOL compiler, and many of the performance problems can be solved by transferring to target hardware of a higher specification than the PC system currently used. However, even with more efficient coding and faster hardware, there is a limit to the improvements that can be obtained with the existing DB4GL implementation.

The motivation for the P-DB4GL project is performance. To try and solve the performance problems encountered in the sequential COBOL implementation of DB4GL, a radically different approach has been taken, that is, the construction of an entirely new parallel implementation of DB4GL.

#### **1.2** Aims of the Research

The aim of the P-DB4GL project is to redesign the DB4GL generated database applications so that they can be executed on parallel hardware. The potentially massive processing power of this parallel hardware can then be used to speed-up the performance of the generated applications, and also allow the applications to be scaled-up to much larger database sizes without loss of performance. The DB4GL application model is retained. This has been shown to be a suitable software architecture for application specification and generation, and the P-DB4GL project is a test of the application model's suitability for parallel implementation. In particular, the object-oriented aspects of the application model are examined to see if an object-oriented specification facilitates parallel implementation.

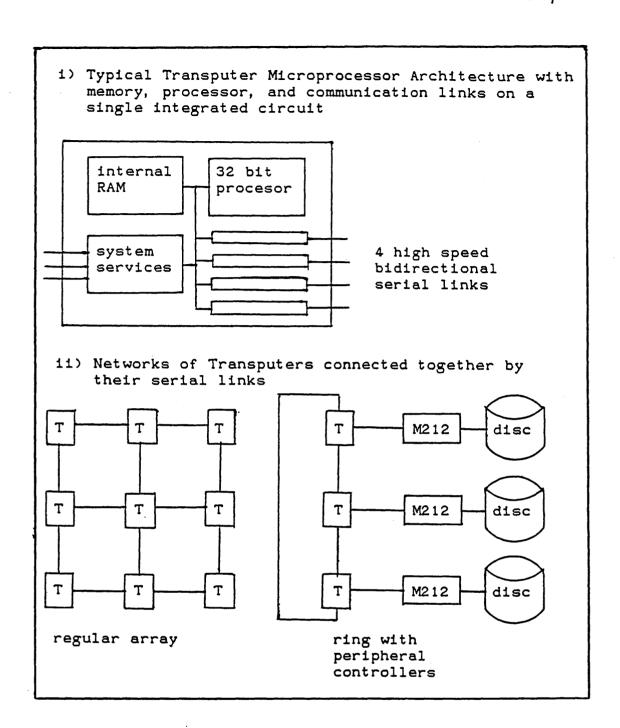

The parallel hardware chosen for the P-DB4GL implementation is transputer based. Transputers [Inmos88a] are a family of VLSI devices, including RISC (Reduced Instruction Set Computer) [Bell86] [Gimarc87] microprocessors and peripheral controllers, specially designed for the construction of distributed memory MIMD (Multiple Instruction Multiple

Data) [Flynn72] architectures. Each transputer microprocessor is a "computer on a chip" and combines on a single integrated circuit, CPU, RAM and high speed serial communication links. Transputers are relatively cheap and are easily connected together by their serial communications links to produce large extensible parallel architectures. The low cost and extensibility of transputers, combined with the availability of several high level parallel languages, makes them suitable candidates for the parallel hardware. Also, at the start of the P-DB4GL project, it was envisaged that the parallel DB4GL database applications would be essentially "shared nothing" architectures [Stonebraker86], and the transputer's built-in communication facilities were considered appropriate for the construction of such architectures.

#### 1.3 The P-DB4GL Approach

The P-DB4GL project differs significantly from many other research projects concerned with database performance issues. In particular, there are three aspects to the P-DB4GL approach which differentiate it from other database approaches. First, it differs architecturally from established database machine approaches. Secondly, the DB4GL application model represents a novel approach to database application development. Thirdly, P-DB4GL is intended for use in a prototyping development environment, and this offers certain advantages; in particular, it facilitates performance "tuning" of the generated database applications.

The P-DB4GL project is not an attempt to construct a dedicated "backend" database machine [Hsiao83]. Typically, such database machines are constructed from specialized custom hardware, and are invariably concerned with improved disc access and file processing, for example: CAFS [Babb79]. DIRECT [DeWitt79], SABRE [Gardarin83], RDBM [Schweppes83], DBMAC [Missikof83], Gamma [Schneider89]. They are generally not stand-alone machines, but dependent on either a host machine (usually a mainframe computer) in which they replace some of the operating system's functions and execute DBMS code more efficiently than the host machine; or else function as a database server forming part of a networked or distributed system, receiving database queries (typically in SQL [BSI88]) from client processors, processing these requests and returning results of this query to the clients. DB4GL differs from such database machines in that all of the database application executes entirely on the transputer-based hardware, there are no separate client or host processes being serviced by P-DB4GL.

Secondly, P-DB4GL applications are fully distributed parallel applications, and exhibit inter-query parallelism which arises from the inherently concurrent specification of DB4GL applications.

A unique feature of the P-DB4GL research is the DB4GL application model. This application model represents an attempt to specify and generate database applications in their entirety. It encompasses all facets of a database-oriented information system - that is, processing, data model, user interface, and integrity constraints - within a uniform structure. Thus, DB4GL differs from other database approaches, in that there is no distinction between DBMS functions and separate application programs using the DBMS. The application model is not relational, but has certain object-oriented characteristics. Specifically, a database application is defined by the model as a set of concurrently executable message passing Presentation Objects, and each particular generated application is considered as an instantiation of the application model. DB4GL is further distinguished from some other database approaches by the special emphasis placed upon the attribute, rather than tuple or relation, as the primary data item.

The use of DB4GL within a prototyping development environment has a significant effect on some implementation features. DB4GL applications are oriented towards on-line transaction processing (OLTP) rather than on-line query processing. This means that all the access paths (explicit data relationships) and patterns of data usage are known and defined in advance of end-user operation of the generated application. Consequently certain optimizations to data access mechanisms, such as the establishment of indexes on frequently used tables, are possible. Indexes reduce search time and improve response time to transactions, however, one disadvantage of indexes is the processing overhead entailed by the maintenance of indexes following an update to the table over which they are defined. The use of parallel processing hardware to improve index maintenance is a key feature of the P-DB4GL system.

A possible solution to the problem of providing an ad hoc query processing facility for a DB4GL system (assuming an appropriate DB4GL application does not already exist to satisfy a given query) is the rapid building of a specific (OLTP-oriented) application for that query. However, with the existing slow DB4GL generator tools this can take several minutes, and hardly constitutes on-line ad hoc query processing. An advantage of a faster

P-DB4GL running on parallel hardware is the potential for greatly reduced application generation time, thereby improving the query processing facilities of DB4GL.

The prototyping development cycle facilitates the "tuning" of P-DB4GL applications for optimal performance. A problem common to many parallel database implementations is efficient resource utilization, that is, matching processing and communication loads of the database software to the available hardware. Because P-DB4GL development is cyclic, at each cycle in the application development, the system analyst/designer has the opportunity of altering the mapping of application code and database data to the available processors and secondary storage devices (disks). Thus allowing the possibility of experimentation with different configurations to find a well balanced configuration offering optimal performance.

#### 1.4 P-DB4GL Project Development

The first stage in the parallel DB4GL investigation was the development of a prototype P-DB4GL system. In this prototype system, simplified "cut-down" database applications were designed and implemented. These P-DB4GL test applications are of reduced functionality, and are equivalent to applications generated by the original [Ewin85a] DB4GL. In a fully functional P-DB4GL, the parallel database applications would be generated automatically by P-DB4GL generation tools, but these tools are not yet fully implemented, and in the prototype system the test applications were hand coded. The test applications were run on several different network configurations, and designs for a fully functional P-DB4GL system are proposed based on the results obtained from these tests.

The reasons for constructing a prototype P-DB4GL are:

- determine the exact amount of parallelism inherent in the DB4GL application model;

- test the soundness of the design approach, that is, of a relatively simple translation from an object-oriented specification to an implementation of concurrent communicating processes;

- assess the suitability of Occam as an implementation language for P-DB4GL;

- examine the feasibility of using transputers as the basis of the parallel processing hardware, both for P-DB4GL in particular and other database (and data intensive) systems in general.

Briefly, the main findings from the prototype P-DB4GL investigation are:

- significant performance benefits were obtained from parallel index maintenance;

- speed-up of any given application by the simple addition of more processors is very difficult to obtain;

- good scale-up in performance by the addition of more processors and discs can be obtained as an application grows larger;

- the P-DB4GL database applications do not significantly load the processors, but applications often become communication bound.

Based on these findings, some design considerations for a fully functional P-DB4GL system are discussed in Chapter 6.

#### 1.5 Outline of Thesis Contents

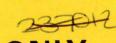

The P-DB4GL research project, as described in this thesis, brings together a number of strands, or themes, of different research interests (Figure 1.1). One of the core themes, providing motivation and background to the DB4GL project, concerns database application generation and prototyping software development. Another core theme is concerned with the technology of parallel processing hardware, specifically transputers and Occam, and the application of transputer technology to data intensive application areas. Parallel architectures for databases and knowledge based systems, including dedicated database machines, specialized relational and logic language machines, and hardware support for object-oriented environments, is a third theme of research. Finally, a concern with software design and development methodologies for concurrent systems completes the picture.

These four different themes of research interest are all components in the P-DB4GL project, and are present in various chapters of this thesis. In the following description of each chapter's contents, the relevance and influence of these themes is indicated.

Chapter 1, the <u>Introduction</u>, introduces the research themes, and explains the motivation and aims of the P-DB4GL project.

Chapter 2 describes the <u>DB4GL Database Application Generation System</u>. DB4GL is the result of research encompassed by the theme of database application generation. Chapter 2 describes the DB4GL system as developed by [Hird89], and pays particular attention to the DB4GL application model which has been greatly influenced by developments in object-oriented research.

Chapter 3, Object-Oriented Database Approaches, provides a simple classification of object-oriented approaches to database development. This classification is used to provide a background, or framework, in which the influence of object-oriented concepts on DB4GL is explained. DB4GL is not representative of the "mainstream" Object-Oriented Database Systems, but the development of DB4GL has drawn heavily on research developments in the object-oriented fields.

Chapter 4, <u>Transputers</u>, <u>Occam and Databases</u>, provides a short introduction to the transputer technology, and the concurrent programming language Occam, used in the construction of the parallel architecture for P-DB4GL. Other database research projects, also using transputer-based technology, are described; and the advantages of transputers for parallel database implementations is explained.

Chapter 5 describes the development of the <u>Prototype Parallel-DB4GL</u> system. The design, implementation, and testing of the prototype P-DB4GL implementation is described in detail. In particular, the design approach, a translation from concurrent object specification to an implementation of communicating concurrent Occam processes, is explained. Based on the results obtained from this prototype system, designs for a fully functional P-DB4GL system are proposed.

Chapter 6, <u>Designs for a Fully Functional P-DB4GL</u>, describes design proposals for a multiprocessor fully functional P-DB4GL system. Some features of these designs, such as channel multiplexing and message routing, have been implemented and tested, and in the light of these results, revisions to the designs are made.

Chapter 7 provides an <u>Evaluation of the P-DB4GL Project</u>, including both the prototype P-DB4GL system and the fully functional designs, and indicates where opportunities for further research lie.

Chapter 8 provides some overall Conclusions from the P-DB4GL project.

Lastly, there is <u>Bibliography</u> of all works cited in the thesis. Followed by a number of <u>Appendices</u>, which mostly contain very detailed information about test data, test results, and algorithms; this has been removed from the main text to make it more concise and readable.

Figure 1.1 - Thesis Contents

## Chapter 2

## The DB4GL Database Application Generation System

#### 2.1 DB4GL Project Overview

DB4GL (Data Base 4th Generation Language) [Ewin85a] [Ewin85b] [Hird89] [Poole87] is a database application generation environment that has been developed at Sheffield City Polytechnic. It is a result of research conducted in the Department of Computer Studies (now incorporated into the School of Computing and Management Sciences) in the areas of database application prototyping and Fourth Generation Languages (4GL's). DB4GL is intended for use within a rapid system building (or prototyping) development cycle [Appleton83] [Dearnley83] [McCraken82]. DB4GL is designed primarily for the generation of on-line transaction processing systems, rather than on-line enquiry systems.

Although DB4GL has been developed principally as a research vehicle, it has been applied to commercial problems. The first version of DB4GL [Ewin85a] was used successfully to generate database applications for a construction company [Ewin84] [Ewin85a]. Subsequent DB4GL research [Poole87] [Hird89], concentrating in the areas of improved specification tools, integrity rule processing, and data dictionary operation, has transformed the original DB4GL system into a sophisticated 4GL environment with a unique object-oriented application model.

#### 2.2 Application Generation and Prototyping

The term "prototyping", when used in the context of software development, means rapidly building an implementation for trial purposes. This provides users with a (sometimes partially) working model of the proposed system in order to identify and define their requirements more precisely. There are two main forms of prototyping:

- <u>"throw-away"</u> requirements analysis prototyping, whereby the prototype systems are discarded once user requirements are fully established;

- <u>"evolutionary"</u> prototyping, in which successive prototypes are developed and the final prototype becomes the delivered system.

Typically, 4GL's (fourth generation languages) or "application generators" [Horowitz85] [Luker86] are used for prototyping.

An application generator is a piece of software (more normally a suite of software tools) that produces a program in some object language, which is tailor-made to fit a specific set of requirements. Application generators (or 4GL's) differ from general purpose high level language translators in that:

- the target language is usually another high level language;

- the range of programs that can be generated, is limited to a particular application domain, for example, database applications;

- often, input to a 4GL does not have to conform to rigid rules of syntax, input is via a dialogue with the user, who may respond in some free format;

- the user of 4GL may not be a professional programmer, he may be an end user or system analyst/designer.

#### 2.3 DB4GL Application Development

DB4GL is an application generation system specifically for database applications. DB4GL generates single user database applications to run on an IBM PC AT microcomputer. The target language generated by DB4GL is COBOL. The specifications of required applications are input to DB4GL using menu-driven screen-based database maintenance applications. DB4GL can be used for either "throw-away" prototyping or for "evolutionary" prototyping. The DB4GL system is intended to be used principally by a system analyst/designer rather than an application end user.

DB4GL is a collection of tools - report generators, screen painters, code generators - based around a data dictionary. The DB4GL data dictionary is active, in that, applications are generated from the specifications stored in the data dictionary at generation time, the data dictionary does not just passively describe applications. The DB4GL data dictionary is itself maintained by DB4GL generated applications and uses a hybrid self-describing [Mark85] [Mark86] [Roussopoulos85] data model [Hird89] [Poole87], originally based on the Entity-Relationship approach [Chen76] [Howe83], but also influenced by other data models, for instance, DIAM [Senko73] [Senko76] and CODASYL [Olle78].

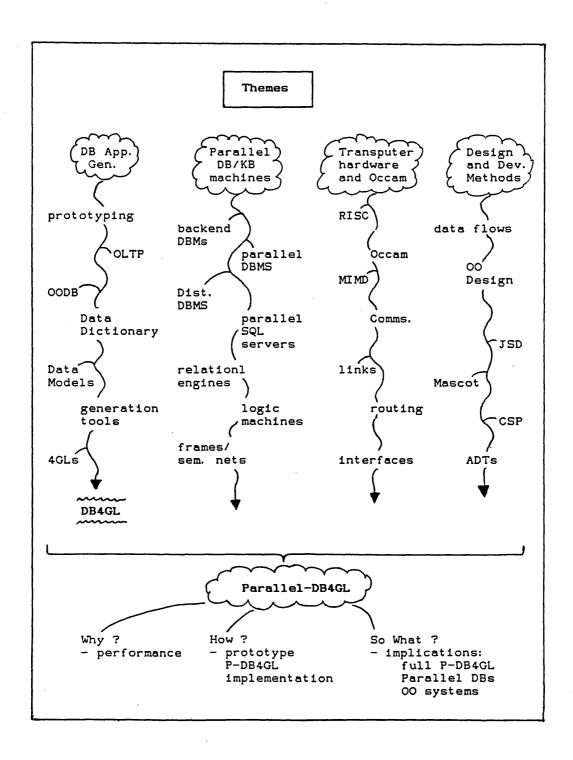

The DB4GL application development cycle is illustrated in Figure 2.1: the specification/generation/user-feedback cycle iterates until the system designer and application user are satisfied with the generated database

application. DB4GL is used mainly for "evolutionary" prototyping, in which the final generated prototype is the delivered database system. The delivered database system can then be operated by the application user without further DB4GL support.

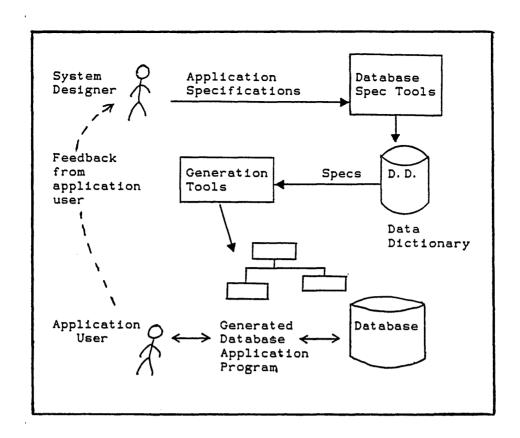

Figure 2.2 illustrates the types of information that constitute the specification of a DB4GL database application, it includes:

- data model description, in terms of entities, attributes, domains, and schema links (access paths);

- processing requirements, in terms of standard maintenance operations and query and report producing functions defined over the entities and attributes of the application;

- user interface, in terms of screens and windows of input and ouput data requested and produced by the processes specified above.

Often, considerable data analysis skills are needed, particularly in the case of large complex applications, in order to properly specify the required database application. Such skills are not normally possessed by application end users. It is therefore unlikely that an application end user would be able to define and generate a DB4GL database application without the help of a skilled system analyst/designer.

## 2.4 The DB4GL Application Model

#### 2.4.1 A Generic Architecture

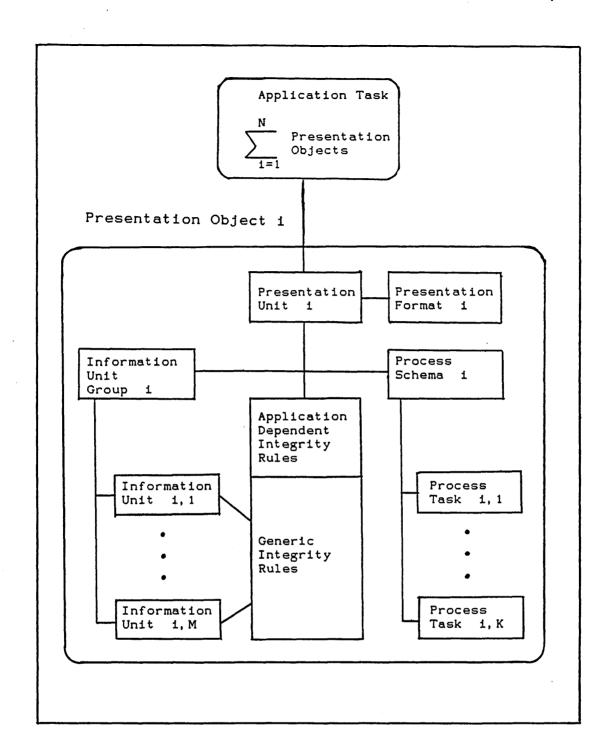

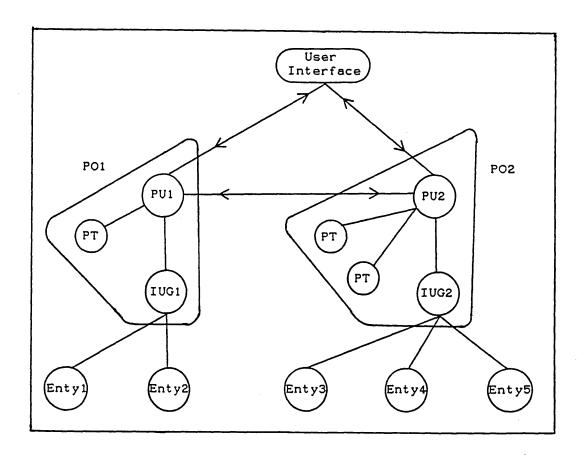

The DB4GL application model, or "architecture of a database application", is central to the generation of database applications (Figure 2.3). This application model is a generic structure or template from which particular application instances are derived. The DB4GL generation tools use the specifications stored in the DB4GL data dictionary to produce a required database application that is an instantiation of the generic DB4GL application model (Figure 2.4). The key features of the application model are:

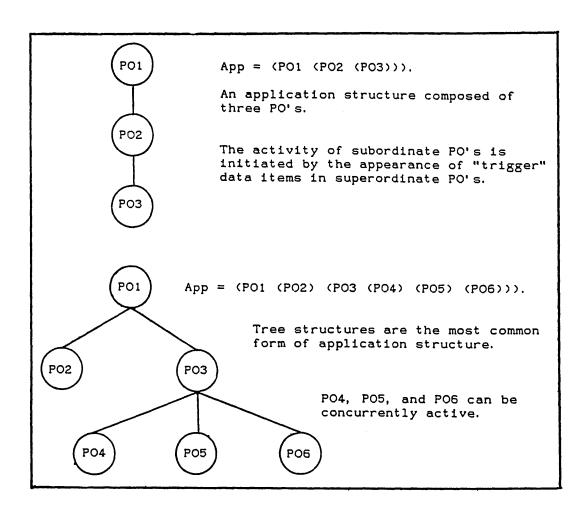

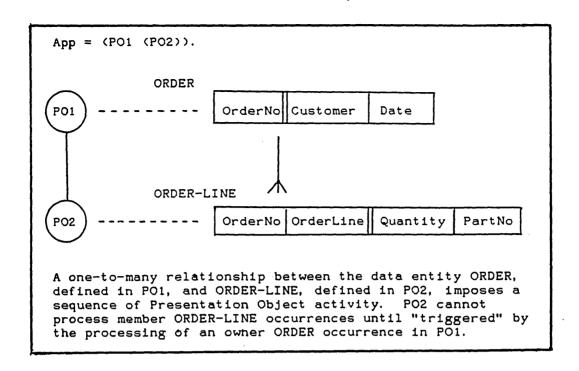

- an application task is defined as a set of Presentation Objects (PO's);

- each constituent PO of an application task includes both information entities and their associated processing tasks;

- each PO is, in principle, capable of concurrent execution, and only interacts with other PO's in the application task by

- communicating control/data messages;

- during the execution of an application task, the course of computation is message driven.

In the simplest of database application, all the required data and processing can be encompassed in a single application task. It is, however, more usual for a DB4GL database application to be constructed as a suite of application tasks. The application tasks are linked together by a menu-driven selection program, produced by a DB4GL menu generator tool. The menu program is used by the application user to select a database processing option, and the menu program invokes the appropriate application task.

#### 2.4.2 Presentation Objects

The concept of the Presentation Object (PO), and its role in the Application Model (AT), is of fundamental importance to DB4GL. Essentially, a Presentation Object combines descriptions of:

- persistent database data;

- processing operations, with their associated transient data, performed upon this persistent data;

- integrity rules, controlling updates to the persistent data.

The definition of an AT partitions a database into a number of disjoint, though related, parts; and each PO operates upon one of these separate parts of the database. The execution model is one of co-operating non-interfering objects.

Specifically, each PO is composed of:

- a Presentation Unit (PU), which defines the sequence of data access and program control required to support the user interaction for the PO;

- an Information Unit Group (IUG), that is, a collection of related data entities, known as Information Units (IU's), processed by the PO;

- a Process Schema (PS), with a number of Process Tasks (PT's) for processing the IUG, the PT's may be functions performing simple data type conversions, or they can be complex processes generating aggregate values and derived data from the IUG;

- a Presentation Format (PF), describing both the appearance of the PO to application users and the interface to other PO's within an

- application;