Electrically active defects in novel Group IV semiconductors.

ALMRABET, Meftah M.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/19253/

# A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/19253/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

Adsetts Centre City Campus Sheffield S1 1WB

101 807 124 5

Return to Learning Centre of issue are chr

2 200

REFERENCE

ProQuest Number: 10694133

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10694133

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code

Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

# Electrically active defects in novel group IV semiconductors

A thesis submitted in partial fulfilment of the requirements of Sheffield Hallam University for the degree of Doctor of Philosophy by:

Meftah M. Almrabet

January 2006

# To all my family, brothers and sisters and to the souls of my parents

# **Declaration**

The work described in this thesis was carried out by the author in the Materials and Engineering Research Institute, Sheffield Hallam University. The author declares that this work has not been submitted for any other degree. The work is original except where acknowledged by reference.

# **Author**

Meftah M. Almrabet

# Acknowledgements

There are many people to thank for their support and encouragement, without whom for one reason or another; my PhD study would have not been possible. First of all, I would like to express my indebtedness and my profound gratitude to my supervisor Professor Jan Evans-Freeman for her help, encouragement, guidance and enlightening discussions throughout this work. It is a great pleasure to thank also my whole family and Libyan higher education authority; I would like also to give special thanks to Dr. Karen Vernon-Parry, for her great help and kindness throughout my research period. I would like to thank also Mr. Mal McGowan for his help, and will not forget my friend Mr. Ahmed Hamed Mohamed for his help, and Dr. Mahmoud Gad. Finally, I would like to thank all the staff, (academic and non-academic) of the Electric and Electronic Engineering Department at The University of Manchester, and the Materials and Engineering Research Institute at Sheffield Hallam University for all the assistance I have received directly or indirectly in undertaking this research.

I would like to thank the Libyan Government for its financial support. Finally, I acknowledge with great pleasure the continuous encouragement and patience of my wife, daughters and sons during this work.

# **Abstract**

This thesis presents the electrical characterisation of defects in novel group IV semiconducting materials: semiconducting diamond and silicon germanium (SiGe) virtual substrates. Several methods to clean diamond surfaces are introduced, which lead to the fabrication of a diamond Schottky diode with acceptable characteristics. Current-Voltage (I-V) and Capacitance-Voltage (C-V) measurements were carried out to study the electrical properties of both the diamond and SiGe Schottky diodes. Deep level transient spectroscopy (DLTS) and Laplace DLTS were then carried out to investigate the deep electronic states in these devices. Scanning Electron Microscopy (SEM) was also used to investigate defects in the diamond samples.

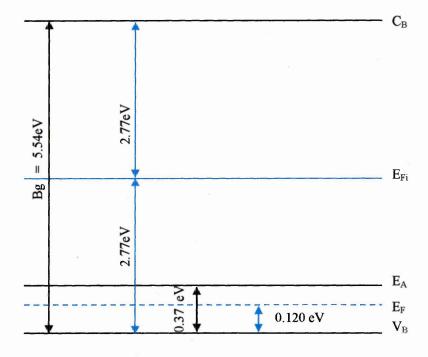

For the diamond Schottky diodes, I-V and C-V measurements confirmed the quality of the fabricated Schottky diode; the measured phase angle between capacitance and voltage was close to 90° for temperatures greater than 300K and frequencies above 200 kHz and the device clearly exhibited rectification. DLTS and LDLTS measurements of the diamond did not show any signatures that could be attributed to isolated point defects. This could be due to the fact that it was necessary to take the samples to higher temperatures in order to fully ionize the boron in the sample. The boron acceptor is at 0.37 eV above the valence band and therefore only about 5% is ionised at room temperature. During the major part of the study at Manchester, there was no access to a high temperature cryostat. However, a clear capacitance transient was observed at lower temperatures and it is proposed that this is due to emission of holes from boron. Deep traps will be located deeper in the band gap than the boron. An additional problem was that the sample was of polycrystalline structure and is full of grain boundaries, which appear to be implicated in the leakage currents present in our devices.

I-V, C-V, DLTS and LDLTS were also used to investigate the deep states in the SiGe virtual substrate. I-V and C-V measurements showed that the SiGe Schottky diode showed some leakage (reported by the suppliers) but nevertheless the diode exhibited rectification. Analysis of the DLTS data showed the presence of a defect in the SiGe samples which could be a structural defect, probably dislocation-related. However, the low background doping meant that a considerable depth below the surface was being measured in DLTS and depth profiling was not possible.

# **Contents**

| Chapter 1  | •••••••••••••••••••••••••••••••••••••••                   | 1  |

|------------|-----------------------------------------------------------|----|

| Introducti | on                                                        | 1  |

| 1.1        | General introduction/statement of the problem             | 1  |

| 1.2 F      | Rationale for research                                    | 2  |

| 1.3 F      | Research Aims and Objectives                              | 2  |

| 1.4        | Organisation of the thesis                                | 3  |

| Reference  | S                                                         | 5  |

| Chapter 2  | •••••••••••                                               | 6  |

| Properties | and growth of diamond                                     | 6  |

| 2.1 I      | ntroduction                                               | 6  |

| 2.1.1      | Silicon carbide                                           | 9  |

| 2.1.2      | Gallium nitride                                           | 10 |

| 2.1.3      | Zinc oxide                                                | 11 |

| 2.1.4      | Diamond                                                   | 12 |

| 2.2        | Classification of diamonds                                | 15 |

| 2.2.1      | Natural diamonds                                          | 15 |

| 2.2.2      | Synthetic industrial diamonds                             | 17 |

| 2.3 N      | Methods for production of synthetic diamond               | 17 |

| 2.3.1      | High-Pressure-High-Temperature growth                     | 18 |

| 2.3.2      | Chemical Vapour Deposition                                | 19 |

| 2.4 N      | Negative electron affinity effects on the diamond surface | 23 |

| 2.5 S      | Summary                                                   | 27 |

| Reference  | ces                                                       | 28 |

| Chapter 3  |                                                           | 32 |

| Impurities | and defects in diamond                                    | 32 |

| 3.1                                                         | Introduction                                                                                                                                                                                                                                                                                                    |                                        |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3.2                                                         | Defects in semiconducting diamond                                                                                                                                                                                                                                                                               | 32                                     |

| 3.3                                                         | Defect state measurements                                                                                                                                                                                                                                                                                       | 37                                     |

| 3.4                                                         | Treatment of the diamond surface                                                                                                                                                                                                                                                                                | 38                                     |

| 3.5                                                         | Impurities in diamond                                                                                                                                                                                                                                                                                           | 40                                     |

| 3.:                                                         |                                                                                                                                                                                                                                                                                                                 |                                        |

| 3.:                                                         | 5.2 Hydrogen in diamond                                                                                                                                                                                                                                                                                         |                                        |

| 3.:                                                         | 5.3 Boron in diamond                                                                                                                                                                                                                                                                                            |                                        |

| 3.:                                                         | 5.4 Phosphorous in diamond                                                                                                                                                                                                                                                                                      |                                        |

| 3.:                                                         | 5.5 Lithium in diamond                                                                                                                                                                                                                                                                                          |                                        |

| 3.:                                                         | 5.6 Other impurities in diamond                                                                                                                                                                                                                                                                                 | 50                                     |

| 3.6                                                         | Grain boundaries                                                                                                                                                                                                                                                                                                | 51                                     |

| 3.7                                                         | Summary                                                                                                                                                                                                                                                                                                         | 55                                     |

| Refe                                                        | rences                                                                                                                                                                                                                                                                                                          | 56                                     |

| Chant                                                       | er 4                                                                                                                                                                                                                                                                                                            | 64                                     |

| Спари                                                       | T 4                                                                                                                                                                                                                                                                                                             | ······································ |

|                                                             |                                                                                                                                                                                                                                                                                                                 |                                        |

| Genera                                                      | al properties of defects in semiconductors                                                                                                                                                                                                                                                                      | 64                                     |

| Genera                                                      |                                                                                                                                                                                                                                                                                                                 |                                        |

|                                                             | al properties of defects in semiconductors                                                                                                                                                                                                                                                                      | 64                                     |

| 4.1                                                         | Introduction                                                                                                                                                                                                                                                                                                    | 64<br>67                               |

| 4.1<br>4.2                                                  | Introduction  Definition of a trap or recombination centre                                                                                                                                                                                                                                                      | 64<br>67                               |

| 4.1<br>4.2<br>4.3<br>4.4                                    | Introduction  Definition of a trap or recombination centre.  Crystal structure and band structure of Si                                                                                                                                                                                                         | 64<br>67<br>69                         |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4                             | Introduction  Definition of a trap or recombination centre  Crystal structure and band structure of Si  Crystal defects                                                                                                                                                                                         | 64<br>67<br>69<br>70                   |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4                             | Introduction  Definition of a trap or recombination centre  Crystal structure and band structure of Si  Crystal defects  1.1 Shallow level defects                                                                                                                                                              | 6467697072                             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4                             | Introduction  Definition of a trap or recombination centre  Crystal structure and band structure of Si  Crystal defects  1.1 Shallow level defects  1.2 Deep level defects                                                                                                                                      | 6467707273                             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.4<br>4.5               | Introduction  Definition of a trap or recombination centre.  Crystal structure and band structure of Si.  Crystal defects.  1.1 Shallow level defects.  1.2 Deep level defects.  1.3 Extended defects.                                                                                                          | 6467707273                             |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.5<br>4.5               | Introduction  Definition of a trap or recombination centre  Crystal structure and band structure of Si  Crystal defects  1.1 Shallow level defects  1.2 Deep level defects  1.3 Extended defects  Effects of defects  Effects of defects                                                                        | 646770727376                           |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5        | Introduction  Definition of a trap or recombination centre  Crystal structure and band structure of Si  Crystal defects  1.1 Shallow level defects  1.2 Deep level defects  1.3 Extended defects  Effects of defects  5.1 Leakage currents                                                                      | 64677072737676                         |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5        | Introduction  Definition of a trap or recombination centre  Crystal structure and band structure of Si  Crystal defects  1.1 Shallow level defects  1.2 Deep level defects  1.3 Extended defects  Effects of defects  5.1 Leakage currents  5.2 Lifetime shortening                                             | 6467707273767677                       |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.4<br>4.5<br>4.5<br>4.5<br>4.6 | Introduction  Definition of a trap or recombination centre.  Crystal structure and band structure of Si.  Crystal defects.  1.1 Shallow level defects.  1.2 Deep level defects.  1.3 Extended defects.  Effects of defects.  5.1 Leakage currents.  5.2 Lifetime shortening.  5.3 Transient enhanced diffusion. | 646770727376767778                     |

| 4.0     | 6.3 The emission process                             | 81  |

|---------|------------------------------------------------------|-----|

| 4.7     | Summary                                              | 83  |

| Refe    | rences                                               | 84  |

| Chapte  | er 5                                                 | 86  |

| Schottl | ky diode                                             | 86  |

| 5.1     | Introduction                                         | 86  |

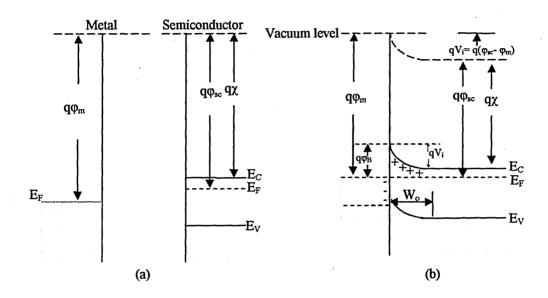

| 5.2     | Energy band diagrams for metal-n-type semiconductor  | 88  |

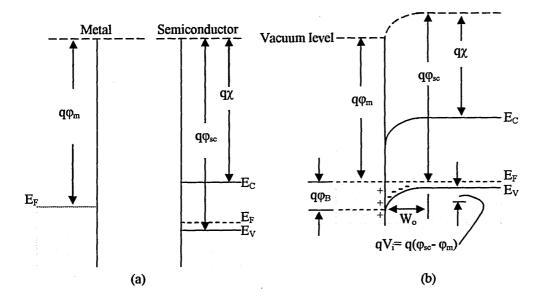

| 5.3     | Energy band diagrams for metal-p-type semiconductor  | 91  |

| 5.4     | Schottky barrier diode                               | 92  |

| 5.5     | Depletion region capacitance                         | 94  |

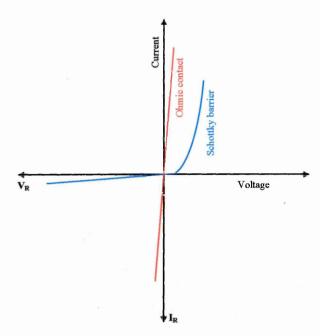

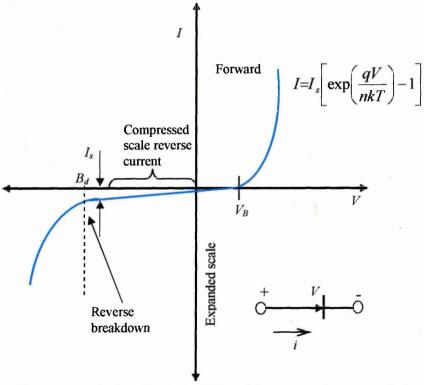

| 5.6     | Typical current-voltage characteristics              | 95  |

| 5.7     | Typical capacitance-voltage characteristics          | 96  |

| 5.8     | Summary                                              | 96  |

| Refe    | rences                                               | 98  |

| Chapte  | er 6                                                 | 99  |

| Experi  | mental techniques                                    | 99  |

| 6.1     | Introduction                                         | 99  |

| 6.2     | Current-voltage and capacitance-voltage measurements | 99  |

| 6.3     | Description of DLTS technique                        | 101 |

| 6.4     | DLTS measurements                                    | 103 |

| 6.5     | Determination of trap parameters                     | 106 |

| 6.5     | 5.1 Trap activation energy, E <sub>A</sub>           | 106 |

| 6.5     | 5.2 Trap concentration, N <sub>T</sub>               | 107 |

| 6.5     | 5.3 Capture cross section, σ <sub>T</sub>            | 107 |

| 6.6     | Emission and capture from deep levels                | 109 |

| 6.7     | Transient capacitance                                | 111 |

| 6.8     | Majority carrier emission                            | 111 |

| 8.3.3      | Capacitance-voltage characteristics                                   | 168   |

|------------|-----------------------------------------------------------------------|-------|

| 8.3.4      | Phase angle versus temperature                                        |       |

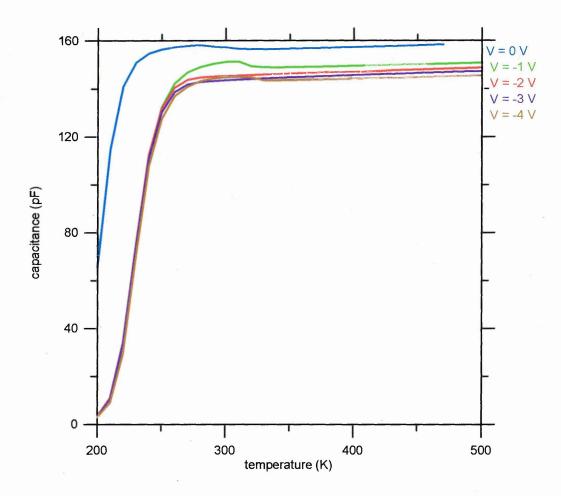

| 8.3.5      | Capacitance versus temperature                                        | 177   |

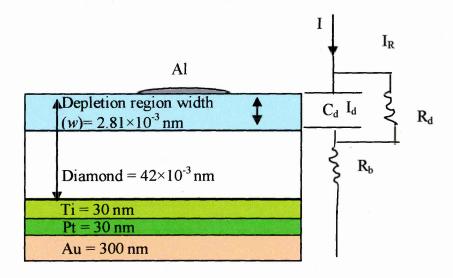

| 8.4        | Depletion region width (w)                                            | 179   |

| 8.5        | DLTS characteristics                                                  | 182   |

| 8.6        | Laplace DLTS characteristics                                          | 188   |

| 8.7        | Scanning electron microscopy                                          | 190   |

| 8.8        | Discussion                                                            | 195   |

| 8.9        | Summary                                                               | 195   |

| Referen    | ces                                                                   | 197   |

| Chapter 9  | )                                                                     | 200   |

| Silicon ge | rmanium Schottky diode                                                | 200   |

|            | Introduction                                                          |       |

| 9.2        | Structural properties of Si <sub>1-x</sub> Ge <sub>x</sub> /Si layers | 201   |

| 9.3        | Lattice misfit parameter                                              | 202   |

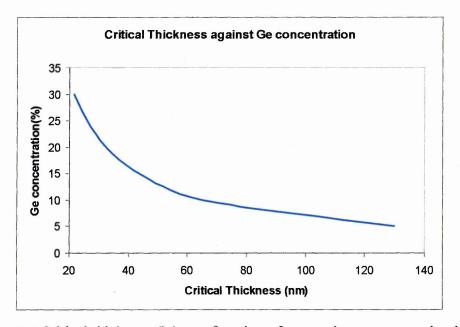

| 9.4        | Critical layer thickness (h <sub>c</sub> )                            | 202   |

| 9.5        | Experimental results                                                  | 204   |

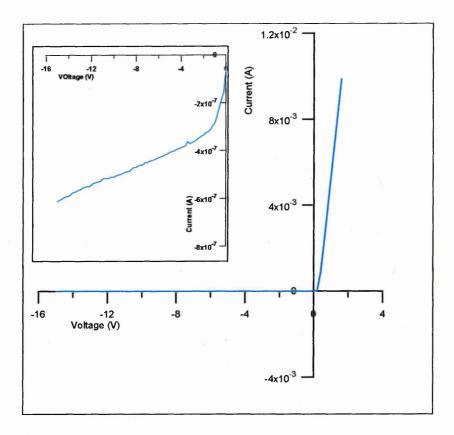

| 9.5.1      | Current-voltage measurements                                          |       |

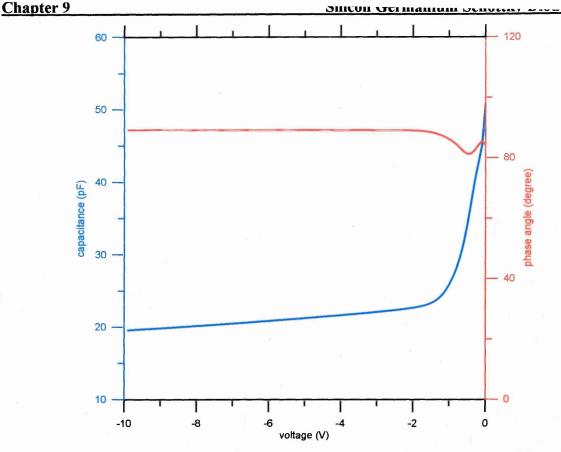

| 9.5.2      | Capacitance-voltage measurements                                      | 205   |

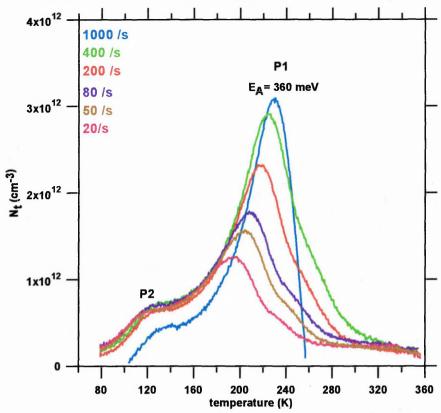

| 9.5.3      | DLTS measurements                                                     |       |

| 9.5.4      | Determination of trap parameters                                      | 211   |

| 9.5.5      |                                                                       |       |

| 9.6        | Comparison between C-V measurements for diamond and SiGe Schottky     |       |

| diodes 2   | 218                                                                   |       |

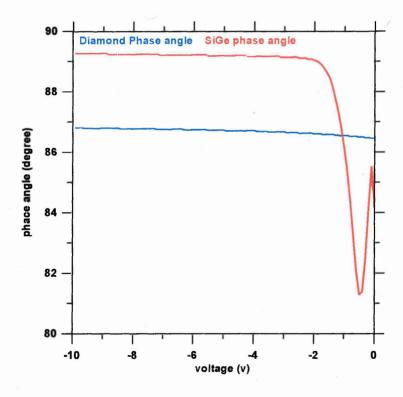

| 9.6.1      | Variation of phase angle with voltage                                 | 218   |

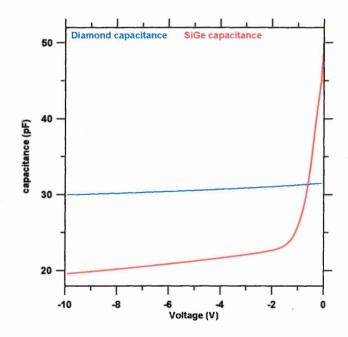

| 9.6.2      | Variation of capacitance with voltage                                 | 219   |

| 9.7        | Summary                                                               | . 220 |

| Referen    | ces                                                                   | 221   |

| Chanter 1  | 0                                                                     | . 222 |

| Conclusions and future work |             | 222   |

|-----------------------------|-------------|-------|

| 10.1                        | Conclusions | . 222 |

| 10.2                        | Future work | 224   |

# **List of figures**

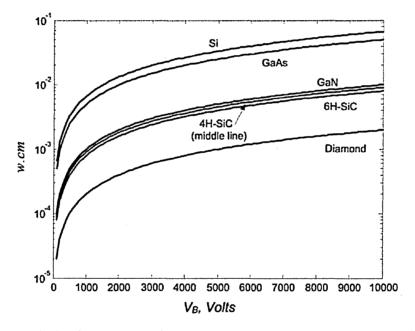

| Figure 2-1 Width of the drift region for several common materials at different                         |

|--------------------------------------------------------------------------------------------------------|

| breakdown voltages                                                                                     |

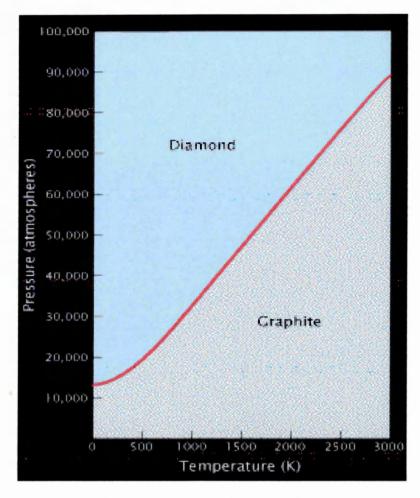

| Figure 2-2 The conditions of pressure and temperature required to form diamond an graphite from carbon |

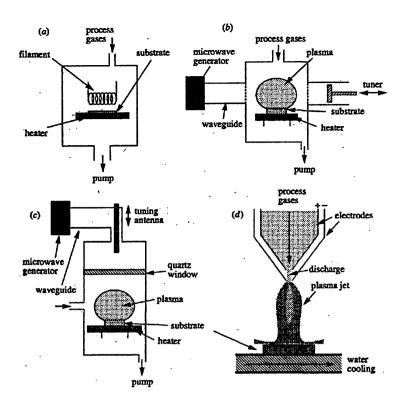

| Figure 2-3 Examples of the more popular types of low pressure CVD diamond reactors                     |

| a- Hot filament, b- National institute for research in inorganic materials "NIRIM-type                 |

| microwave plasma reactor, c- Applied science and technology exchange "ASTEX-type                       |

| microwave plasma reactor, d- dc arc (plasma torch)                                                     |

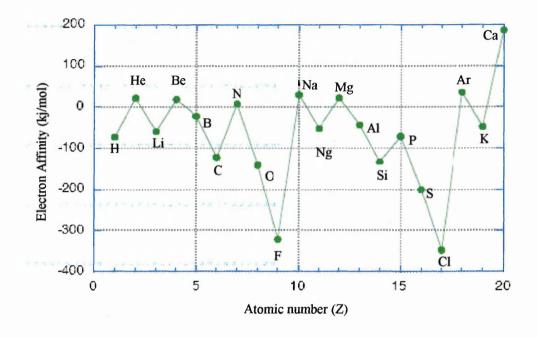

| Figure 2-4 Electron affinity values for the first 20 elements                                          |

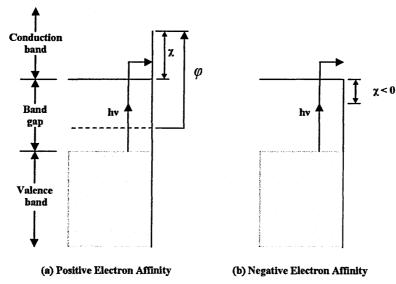

| Figure 2-5 Shows the electron affinity band diagram; (a) PEA, (b) NEA                                  |

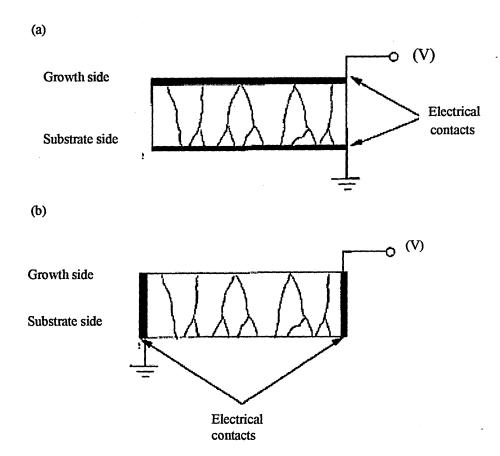

| Figure 3-1 Schematic of the device geometries for measurements of grain boundary                       |

| effect: a- applied electric field parallel to the crystallite growth direction; b- applied             |

| electric field normal to the crystallite growth direction                                              |

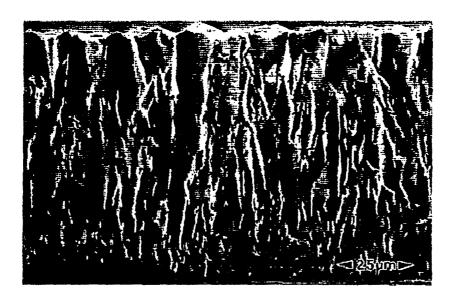

| Figure 3-2 SEM micrograph of across section of a CVD diamond sample, showing the                       |

| columnar microstructure with a very wide range of grain size from $<<1\mu m$ on the                    |

| nucleation surface to $\sim$ 20 $\mu m$ on the growth surface                                          |

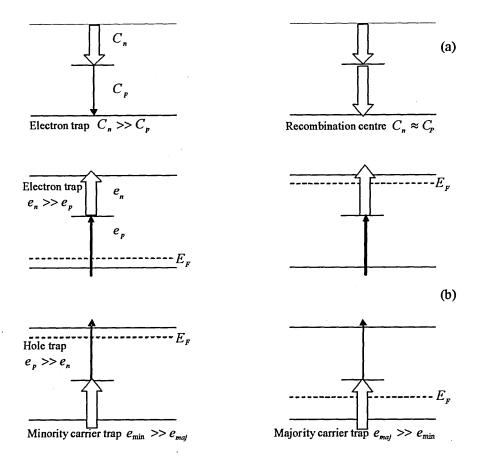

| Figure 4-1 (a) Definition of the terms of electron traps and recombination centres by                  |

| means of the relative magnitudes of the capture coefficients as indicated by the width                 |

| of the arrows. (b) Definition of the terms majority carrier trap and minority trap                     |

| (columns) and electron trap and hole trap (rows), the relative magnitudes of the carrie                |

| emission coefficients are indicated by the widths of the arrows                                        |

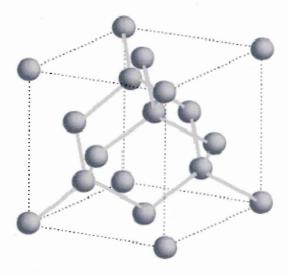

| Figure 4-2 Silicon, germanium and diamond crystal structure                                            |

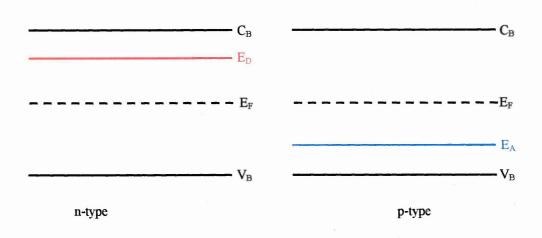

| Figure 4-3 The donor and acceptor levels in the conduction band                                        |

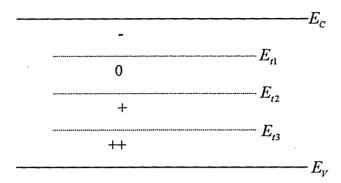

| charge states. The absolute state of the defect is dependent on the position of the Ferm                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| level                                                                                                                                                                                                                                                                                                                              |

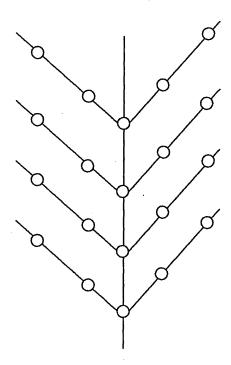

| Figure 4-5 Two-dimensional representation of a twinned crystal                                                                                                                                                                                                                                                                     |

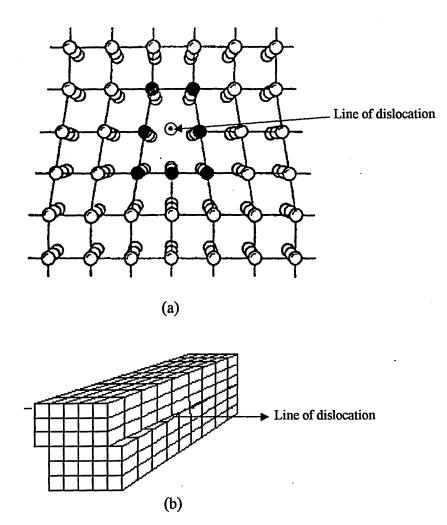

| Figure 4-6 (a) Schematic diagram of a crystal containing an edge dislocation. (b) Geometry of a screw-type dislocation                                                                                                                                                                                                             |

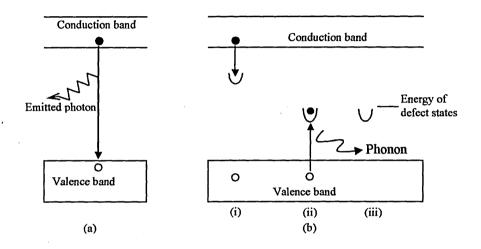

| Figure 4-7 (a) Band to band recombination (b) recombination via a defect centre. The first step in (b) is (i) the trapping of an electron followed by (ii) hole capture. This result in the annihilation of an electron hole pair and emission of a phonon, leaving the centre ready to participate in another recombination (iii) |

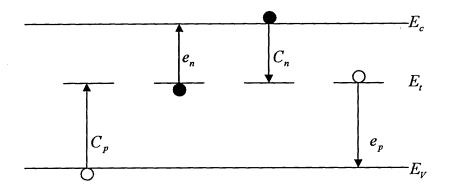

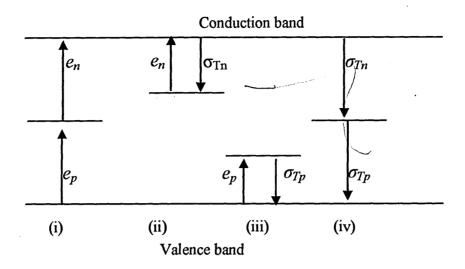

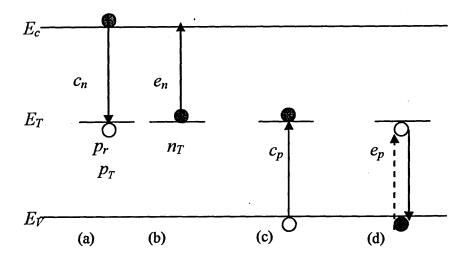

| Figure 4-8 Interactions between a deep energy level and the two bands. Electrons an holes are represented by filled and open symbols, respectively                                                                                                                                                                                 |

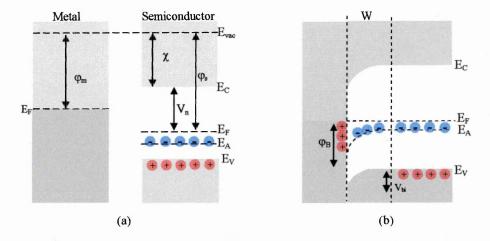

| Figure 5-1 (a) A metal and a semiconductor before contact. (b) A Schottky barried formed after contact between metal and semiconductor. A region of uncompensate charged acceptors results. This causes a voltage drop at the interface                                                                                            |

| Figure 5-2 Energy band diagrams of metal-n-type semiconductor contact (a) two materials isolated from each other, (b) thermal equilibrium situation after the contact is made                                                                                                                                                      |

| Figure 5-3 Energy band diagrams of a metal-p-type semiconductor contact with $\phi_m < \phi_m$ (a) Materials isolated from each other, (b) situation after the contact is made an thermal equilibrium is reached                                                                                                                   |

| Figure 5-4 The current-voltage characteristics of Schottky diode and Ohmic contact o silicon                                                                                                                                                                                                                                       |

| Figure 6-1 The principal charge mechanisms associated with deep states                                                                                                                                                                                                                                                             |

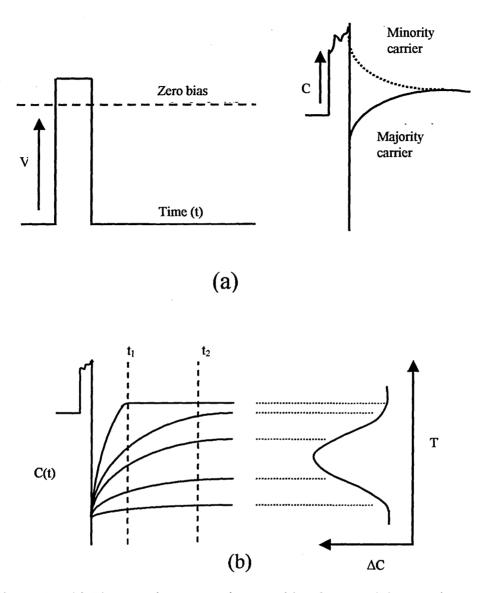

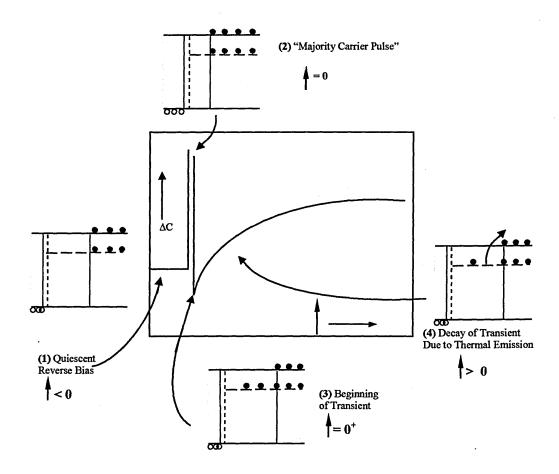

| Figure 6-2 (a) The capacitance transient resulting from applying a voltage pulse to                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| diode containing deep states. (b) The use of test pulses at t1 and t2 to extract $\Delta C$ 104                                                                                                                                                                                                                                                                                                                                                                                                  |

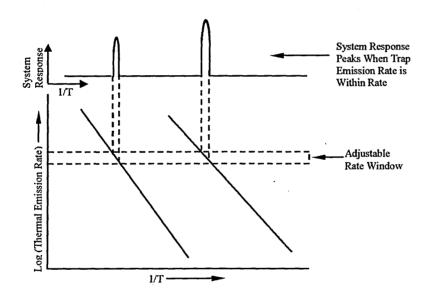

| Figure 6-3 Shows the rate widow concept, which is the basis of the DLTS method 106                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 6-4 Various carrier transitions between deep level and band edge                                                                                                                                                                                                                                                                                                                                                                                                                          |

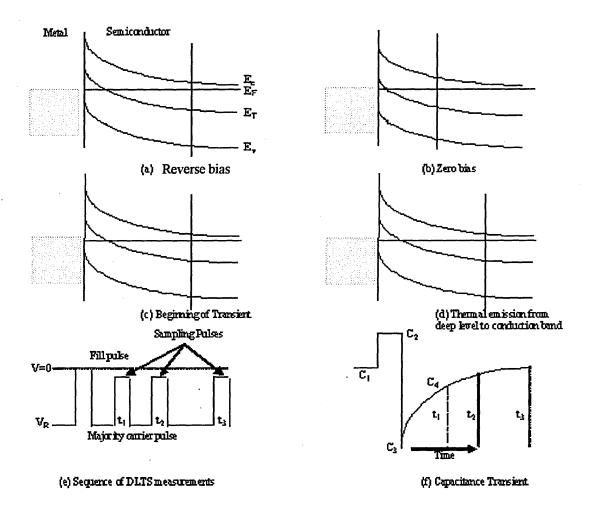

| Figure 6-5 Variation of capacitance with the filling and thermal emission of a majority carrier trap                                                                                                                                                                                                                                                                                                                                                                                             |

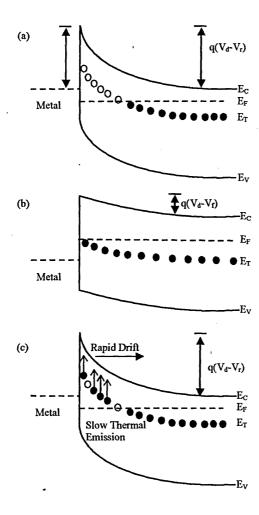

| Figure 6-6 The band gap of the Schottky barrier. (a) At quiescent reverse bias with all deep levels empty. (b) Filling pulse, all deep levels full (c) The deep levels emit the                                                                                                                                                                                                                                                                                                                  |

| trapped electrons with a characteristic emission rate                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 6-7 Isothermal capacitances transient for thermal emission from a majority carrier trap                                                                                                                                                                                                                                                                                                                                                                                                   |

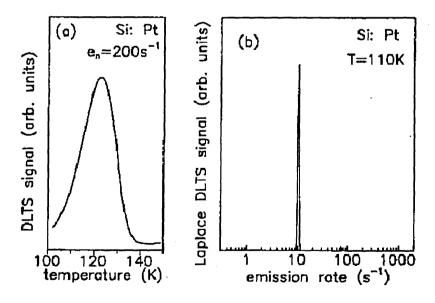

| Figure 6-8 Comparison between conventional and LDLTS spectra. These show a platinum related defect in silicon                                                                                                                                                                                                                                                                                                                                                                                    |

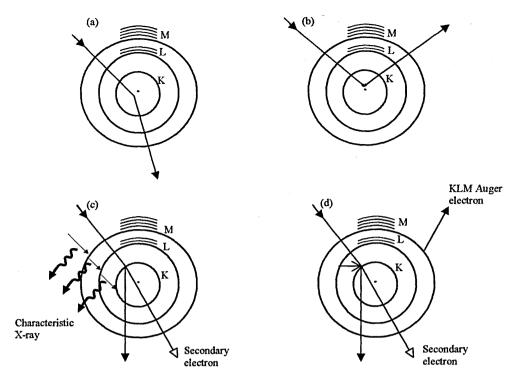

| Figure 6-9 Atom-high energy electron interactions. The inner electron shells of atoms are labelled according to standard notation (the innermost states K, L etc). The incident particle is arrowed. a- Low-angle scattering – electrons scattered in this way pass to the next layer of the atoms with very little loss of energy; b- Back (or high angle) scattering; c- Emission of a secondary electron and characteristic X-ray; d- Emission of a secondary electron and an Auger electron. |

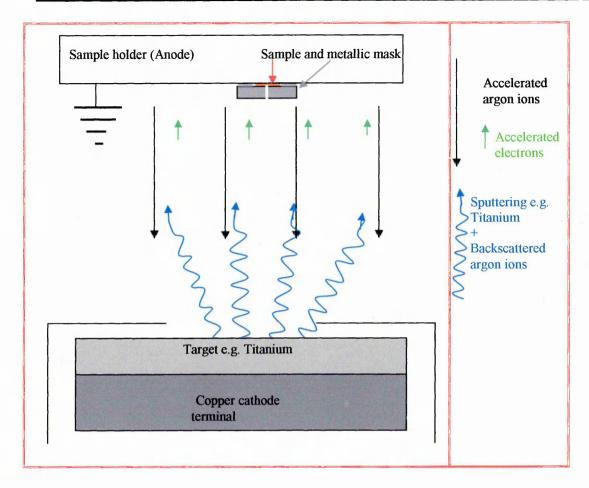

| Figure 7-1 Schematic of the sputtering system                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

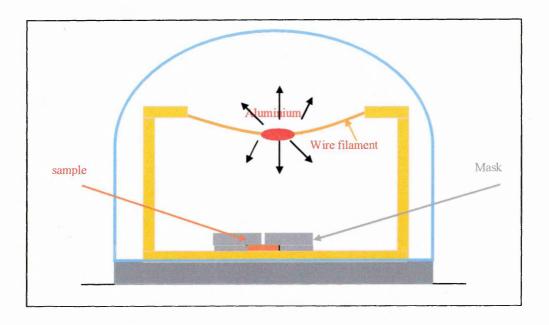

| Figure 7-2 Schematic of the thermal evaporation system                                                                                                                                                                                                                                                                                                                                                                                                                                           |

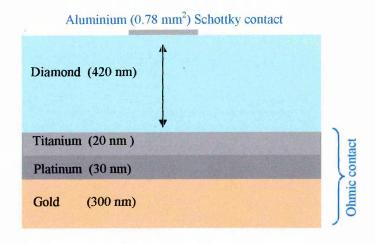

| Figure 7-3 Cross-section schematic of the fabricated diode                                                                                                                                                                                                                                                                                                                                                                                                                                       |

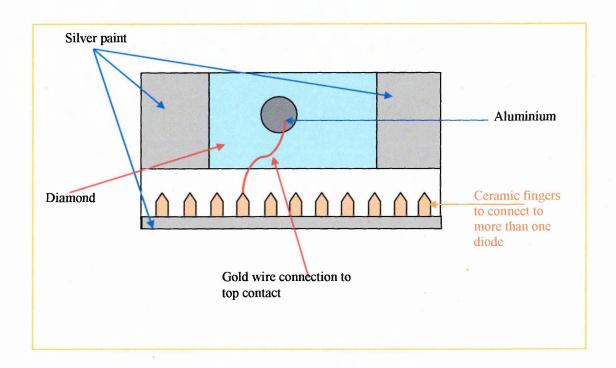

| Figure 7-4 Bird's eye view of the Schottky diode mounted on the ceramic                                                                                                                                                                                                                                                                                                                                                                                                                          |

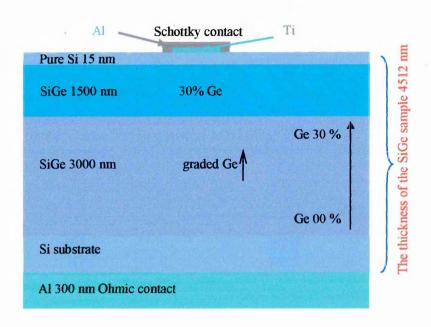

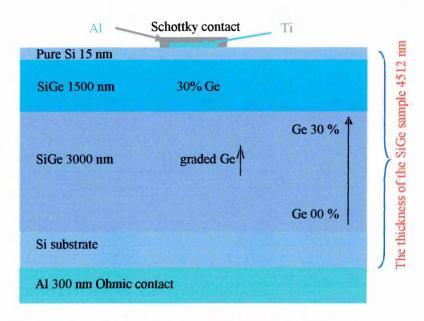

| Figure 7-5 Schematic of the SiGe Schottky diode                                                                                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

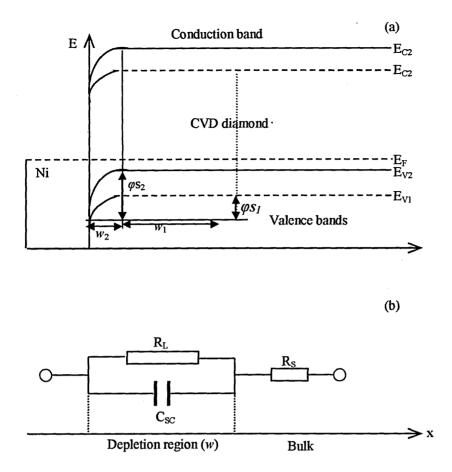

| Figure 8-1 (a) and (b) shows a schematic view of the energy band diagram for B-doped and undoped diamond films and the equivalent circuit respectively: RS is the bulk resistance of diamond; CSC is the capacitance of the depletion region or space charge region, RL is the resistance determining the leakage current of the Schottky contact152 |

| Figure 8-2 Band diagram of the Schottky diamond diode                                                                                                                                                                                                                                                                                                |

| Figure 8-3 Diode I-V relationship with some scales expanded and other compressed in order to reveal details                                                                                                                                                                                                                                          |

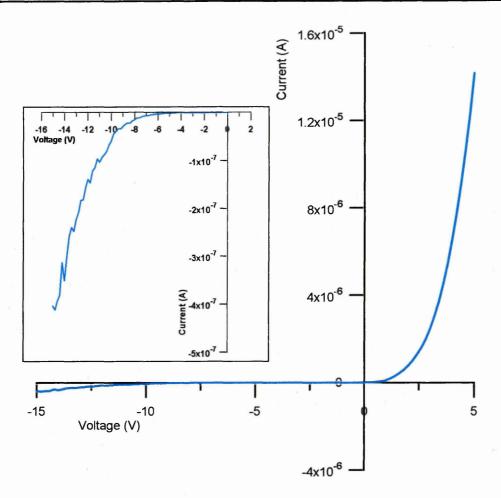

| Figure 8-4 measurement of a low boron doped diamond sample. The window shows reverse biased I-V curve for the same sample with an expanded current scale over the range -16 to 2V.                                                                                                                                                                   |

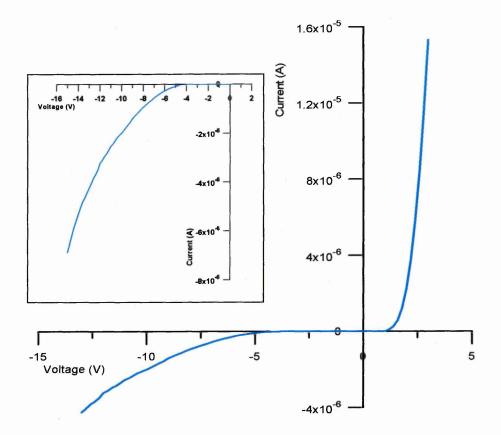

| Figure 8-5 measurement of high boron doped diamond sample. The window shows reverse biased I-V curve for the same sample with an expanded current scale over the range -16 to 2V                                                                                                                                                                     |

| Figure 8-6 Variation of the current and barrier height with temperature of a diamond Schottky diode doped with a low proportion of boron                                                                                                                                                                                                             |

| Figure 8-7 Variation of current and barrier height of a silicon Schottky diode with change of temperature                                                                                                                                                                                                                                            |

| Figure 8-8 Derivation of the derived saturation current ( <i>I<sub>s</sub></i> ) with the voltage for the lower doped diamond                                                                                                                                                                                                                        |

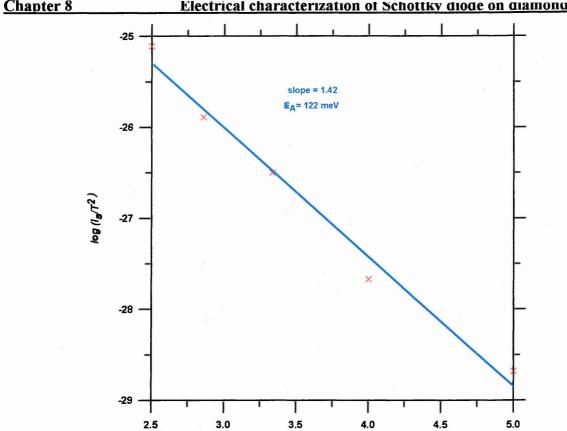

| Figure 8-9 Arrhenius plot of $\ln (I_s/T^2)$ against $10^3/T$ for the lower doped diamond165                                                                                                                                                                                                                                                         |

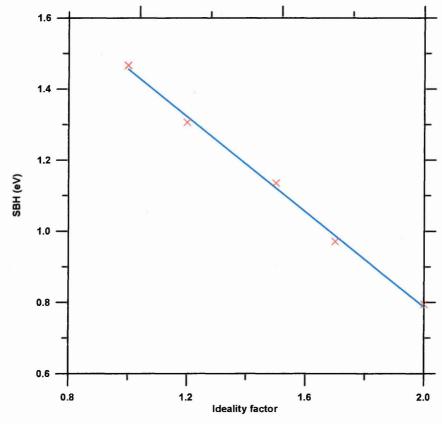

| Figure 8-10 Relation between the SBH and the ideality factor for the lower doped diamond                                                                                                                                                                                                                                                             |

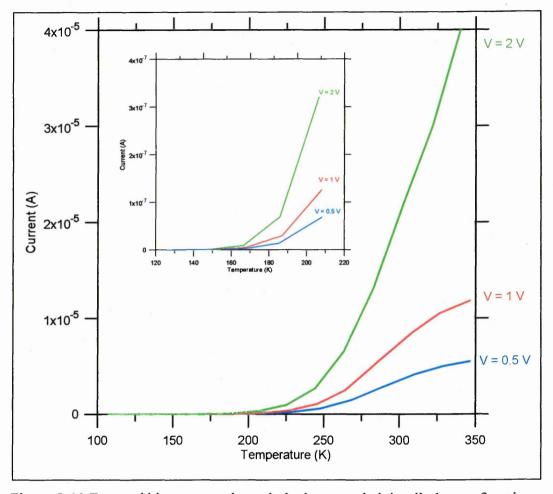

| Figure 8-12 Forward bias current through the lower resistivity diode as a function of        |

|----------------------------------------------------------------------------------------------|

| temperature for three different voltages. Inset is a high resolution plot of the carrier     |

| freeze out region                                                                            |

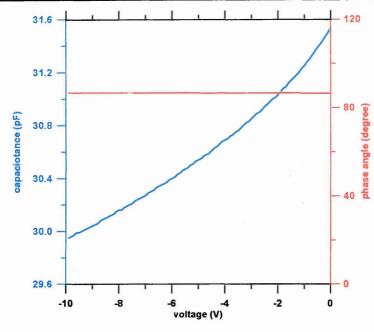

| Figure 8-13 C-V measurement for low boron doped diode diamond                                |

| Figure 8-14 Change of phase angle of Schottky on diamond with reverse bias voltage           |

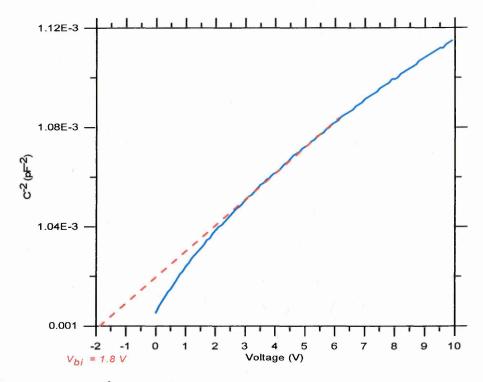

| Figure 8-15 C <sup>-2</sup> as a function of forward bias $V_{app}$ on low boron sample      |

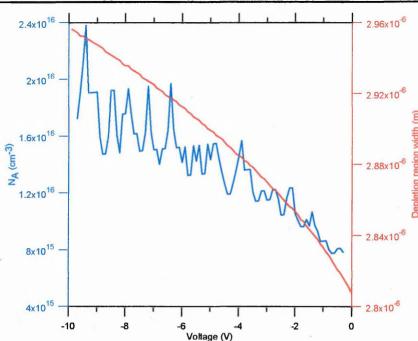

| Figure 8-16 Change in carrier density and voltage as a function of depletion region          |

| width for the low boron doped sample                                                         |

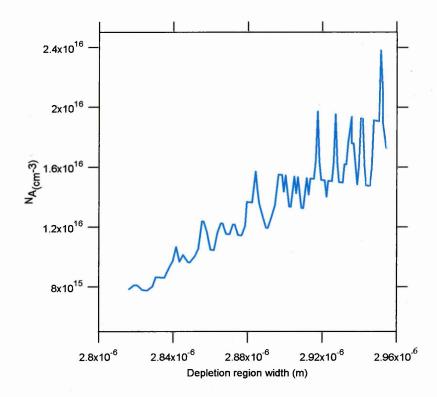

| Figure 8-17 Carrier concentration of low boron diamond Schottky diode as a function          |

| of depletion region width (w)                                                                |

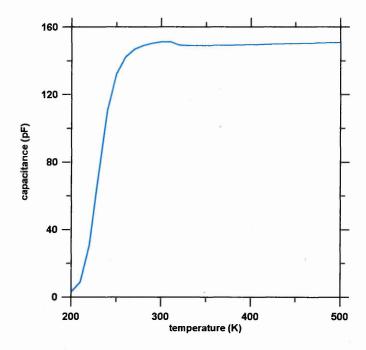

| Figure 8-18 Capacitance as a function of temperature of semiconducting diamond with          |

| a resistivity of $800\Omega$ -cm. Carrier freeze-out onto the boron atoms occurs between 200 |

| K and 300 K in diamond                                                                       |

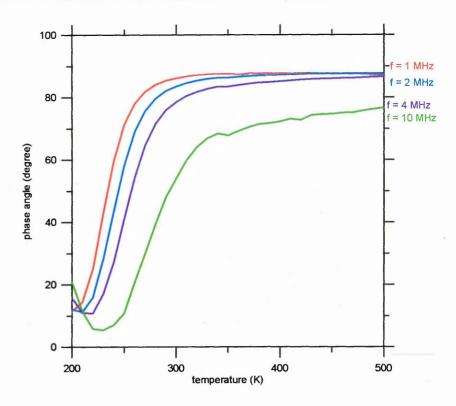

| Figure 8-19 Phase angle versus temperature at various frequencies in high boron doped        |

| diamond measured at 1-10 MHz                                                                 |

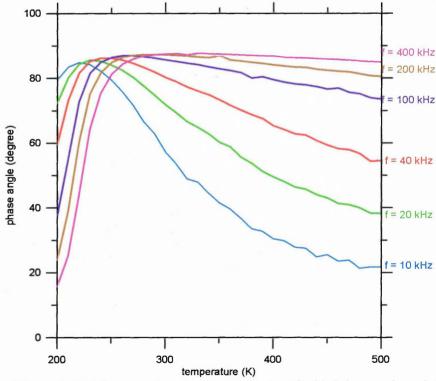

| Figure 8-20 Phase angle versus temperature in high boron doped diamond measured at           |

| 10-400 MHz                                                                                   |

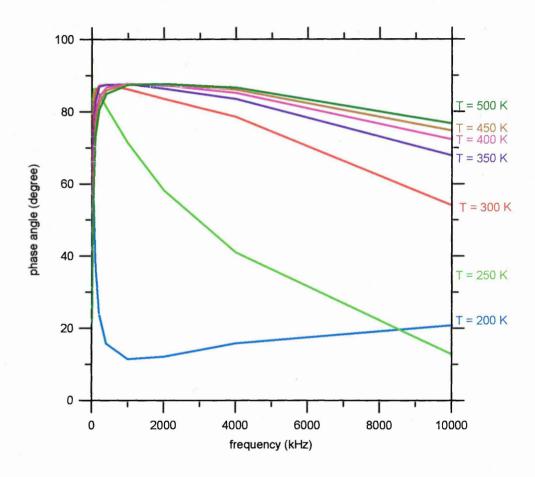

| Figure 8-21 Phase angle versus frequency at different temperatures in high boron doped       |

| diamond                                                                                      |

| Figure 8-22 Capacitance versus temperature for high boron doping at different bias           |

| voltages. V= 0, -1, -2, -3 and -4V                                                           |

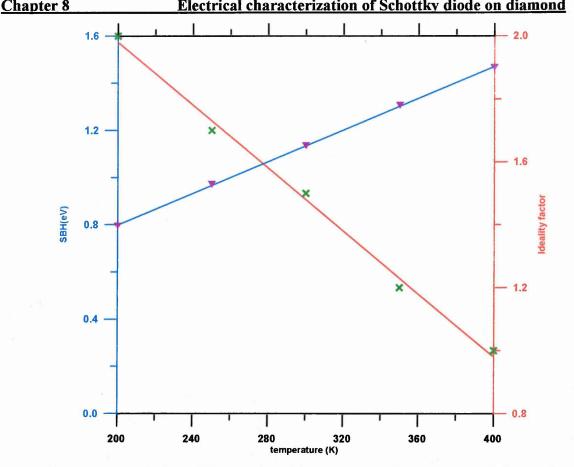

Figure 8-11 Variation of SBH and n with temperature for lower doped diamond .... 166

| Figure 8-23 Structure of diode and equivalent circuit of the sample                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

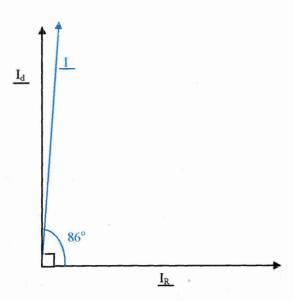

| Figure 8-24 Vectorial representation of current flows in the capacitor and resistor is series connection.                                                                                                                                     |

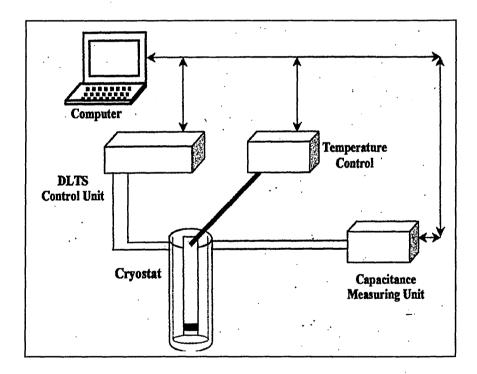

| Figure 8-25 Diagram of conventional DLTS measurement system                                                                                                                                                                                   |

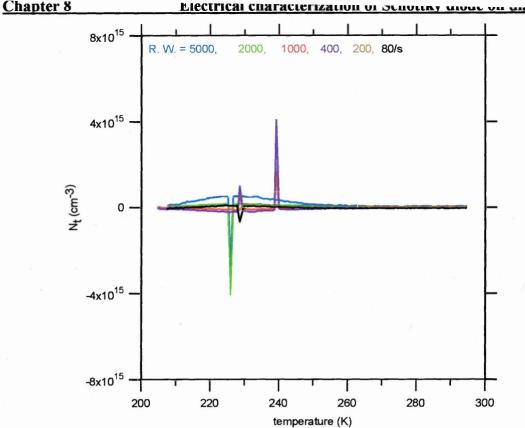

| Figure 8-26 DLTS measurement when $V = -1.5V$ , high boron doped diamond 186                                                                                                                                                                  |

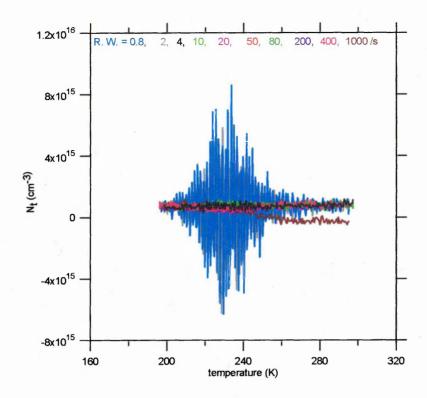

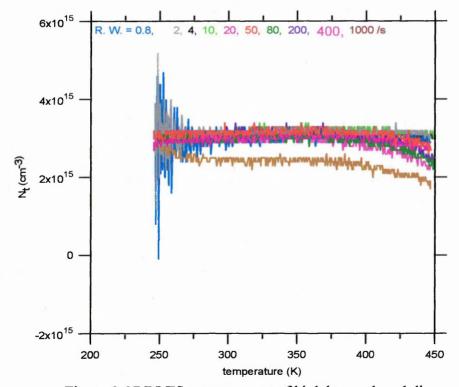

| Figure 8-27 DLTS measurement of high boron doped diamond                                                                                                                                                                                      |

| Figure 8-28 DLTS measurement of high boron doped diamond                                                                                                                                                                                      |

| Figure 8-29 DLTS measurement of high boron doped diamond                                                                                                                                                                                      |

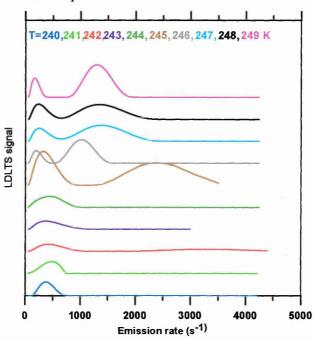

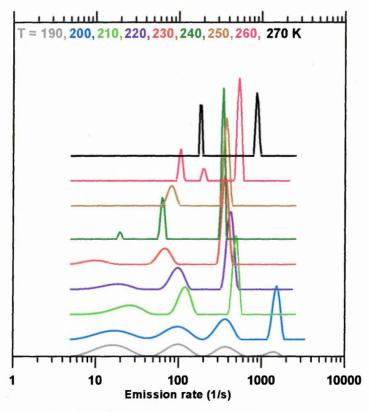

| Figure 8-30 Peaks in LDLTS at different temperatures versus emission rate, of diamond with a high concentration of boron                                                                                                                      |

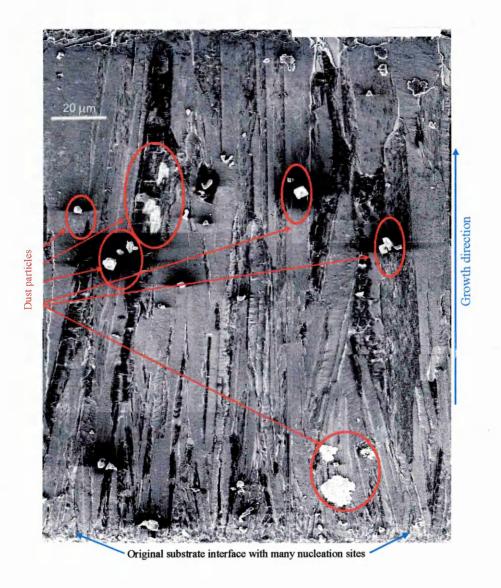

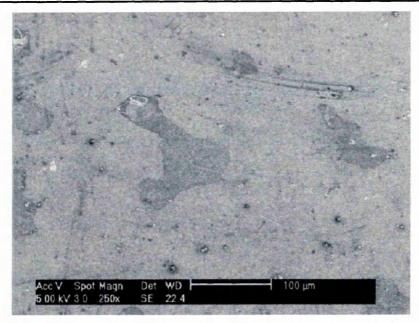

| Figure 8-31 Secondary electron images of a cross-section of a polycrystalline diamond film, illustrating the columnar nature of the grains                                                                                                    |

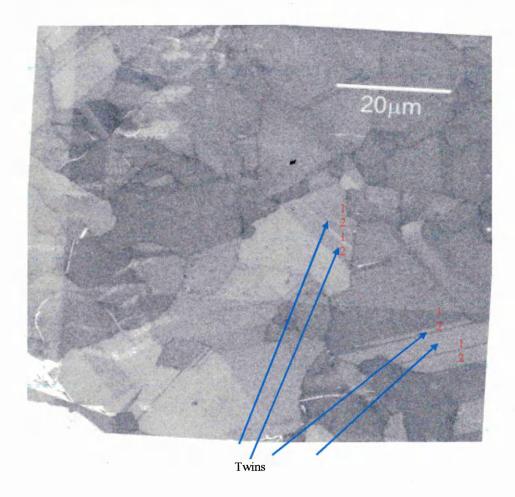

| Figure 8-32 Secondary electron image of the top surface of the polycrystalline diamond film                                                                                                                                                   |

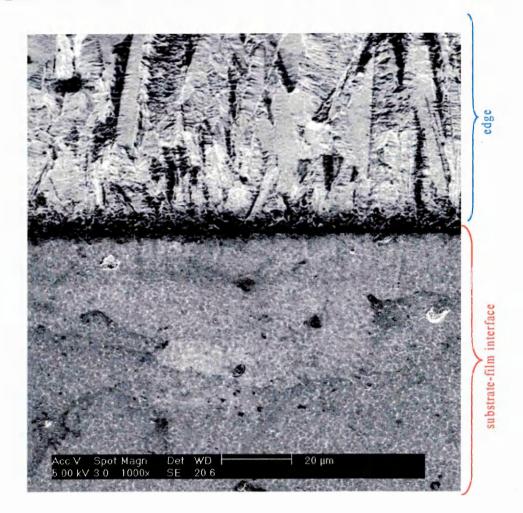

| Figure 8-33 Secondary electron image of specimen tilted to show both original substrate-film interface and edge of film                                                                                                                       |

| Figure 8-34 Secondary electron image of original substrate interface                                                                                                                                                                          |

| Figure 9-1 Critical thickness (h <sub>c</sub> ) as a function of germanium concentration in the Si <sub>1</sub> -  Ge <sub>x</sub> layer                                                                                                      |

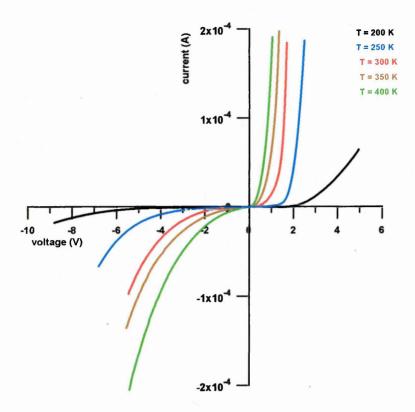

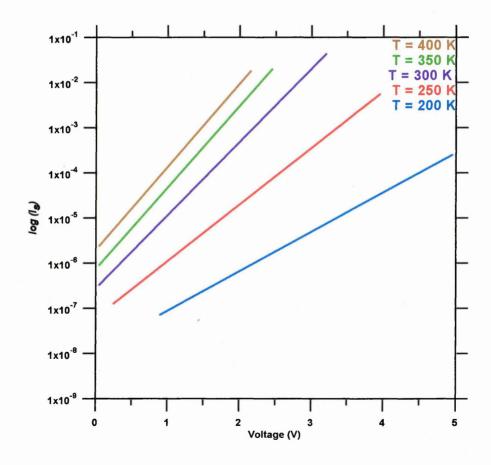

| Figure 9-2 curve at room temperature of a Schottky diode on Si <sub>1-x</sub> Ge <sub>x</sub> grown on a virtual substrate, inset shows the reverse bias region in more detail. The diode shown is the least leaky of all the tested samples. |

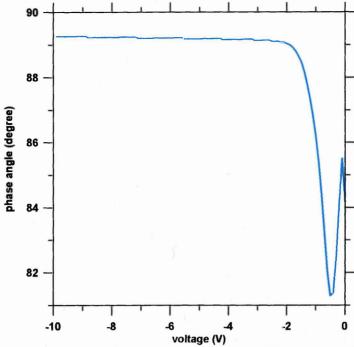

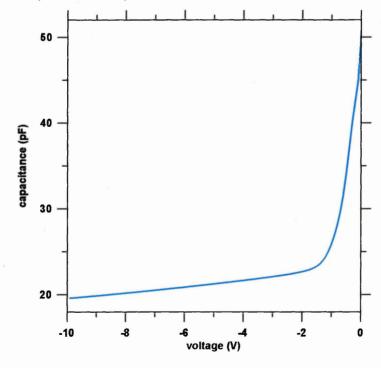

| Figure 9-3 Variation of capacitance and phase angle with applied reverse bias of                                                                                                    | Si <sub>0.7</sub> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Ge <sub>0.3</sub> grown on a virtual substrate                                                                                                                                      | 206               |

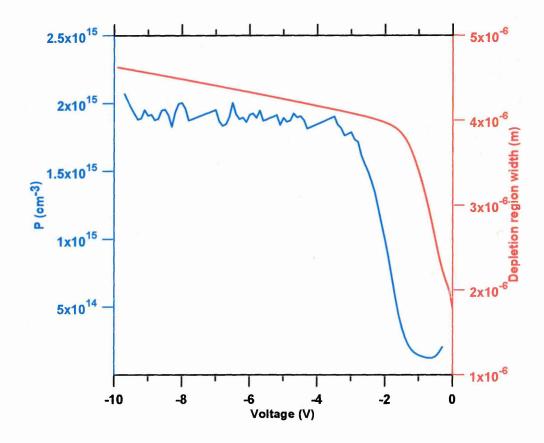

| Figure 9-4 Variation of phase angle with reverse bias in more detail of the Si <sub>0.7</sub> C Schottky diode grown on a virtual substrate                                         |                   |

| Figure 9-5 Change of the capacitance as function of reverse bias voltage of the Ge <sub>0.3</sub> Schottky diode grown on a virtual substrate                                       |                   |

| Figure 9-6 Variation of boron concentration and depletion region width with rev bias voltage of the Si <sub>0.7</sub> Ge <sub>0.3</sub> Schottky diode grown on a virtual substrate |                   |

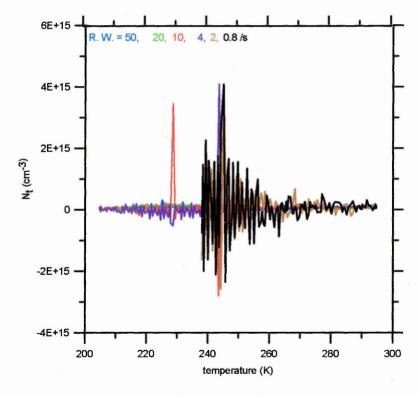

| Figure 9-7 DLTS at different rate windows of Si <sub>0.7</sub> Ge <sub>0.3</sub> grown on a vir substrate                                                                           |                   |

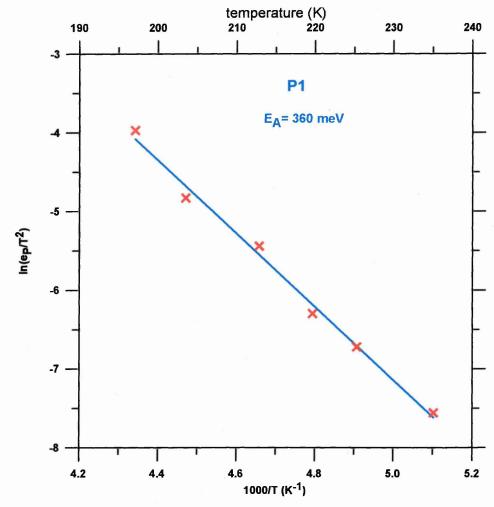

| Figure 9-8 Arrhenius plots for activation energy for P1                                                                                                                             | 212               |

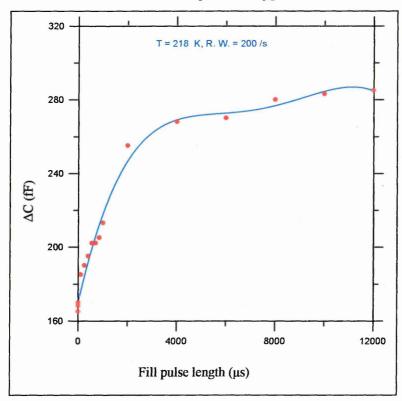

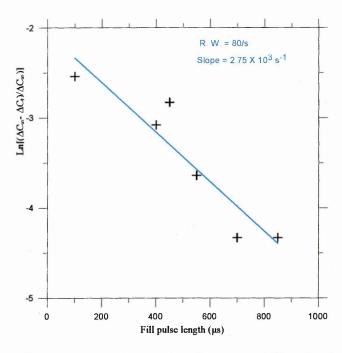

| Figure 9-9 $\Delta C$ as a function of fill pulse length for the SiGe sample, T = 218 K window = 200 /s.                                                                            | rate<br>213       |

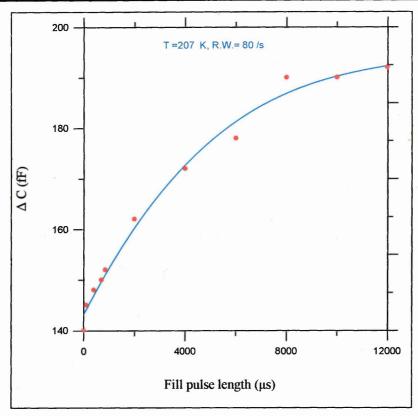

| Figure 9-10 $\Delta C$ as a function of fill pulse length for the SiGe sample, $T = 207 \text{ K}$ , window = $80/\text{s}$ .                                                       |                   |

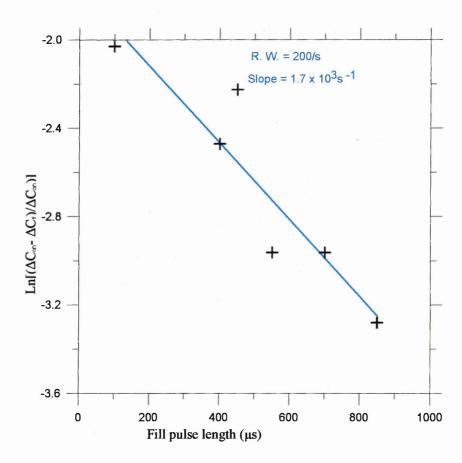

| Figure 9-11 Change in capacitance as a function of fill pulse length, for a rate wind of 200/s                                                                                      | ow<br>215         |

| Figure 9-12 Change in capacitance as a function of fill pulse length, for a rate wind of 80/s                                                                                       | dow<br>216        |

| Figure 9-13 LDTS of peak P1, for SiGe virtual substrate                                                                                                                             | 217               |

| <u>Figure 9-14</u> Phase angle as a function of applied reverse bias voltage for SiGe (red) diamond (blue).                                                                         | and<br>218        |

| <u>Figure</u> | <u>9-15</u> S | chematic of the | ie Si | Ge | e Schottky | dio | de showr | in fig | gure 7-5 |     | • • • • • • • | 219 |

|---------------|---------------|-----------------|-------|----|------------|-----|----------|--------|----------|-----|---------------|-----|

|               |               |                 |       |    |            |     |          |        |          |     |               |     |

| <u>Figure</u> | 9-16          | Capacitance     | as    | a  | function   | of  | reverse  | bias   | voltage  | for | SiGe          | and |

| diamon        | <b>1</b>      |                 |       |    |            |     |          |        |          |     |               | 219 |

# **List of tables**

| <u>Table 2-1</u> Physical characteristics of silicon and common wide bandgap                          |

|-------------------------------------------------------------------------------------------------------|

| semiconductors                                                                                        |

|                                                                                                       |

| <u>Table 4-1</u> A section of the periodic table of elements                                          |

| •                                                                                                     |

| <u>Table 5-1</u> Work functions of common substances                                                  |

|                                                                                                       |

| <u>Table 6-1</u> Difference between optical microscopy and scanning electron                          |

| microscopy                                                                                            |

|                                                                                                       |

| <u>Table 7-1</u> Relationship between work function $(\varphi_m)$ and electronegativity $(\chi_m)$ of |

| metals, and their contact properties with CVD diamond before (as-grown) and after                     |

| treatment A or C                                                                                      |

|                                                                                                       |

| <u>Table 8-1</u> Description of the samples used in this work                                         |

|                                                                                                       |

| Table 8-2 The ideality factor and barrier height of p-type diamond Schottky                           |

| diode                                                                                                 |

|                                                                                                       |

| <u>Table 9-1</u> The parameters used in the DLTS measurements shown in figure                         |

| 9-7                                                                                                   |

# Chapter 1

## Introduction

#### 1.1 General introduction/statement of the problem

This research is centred around two novel and emerging technologies in electronic devices, namely new materials for power electronics, and the need for new designs to enable complementary metal oxide semiconductor (CMOS) scaling.

Silicon diodes presently used in power electronics are approaching their theoretical limits in that they lack both the high voltage capacity and power handling capabilities needed for high efficiency power electronic converters and systems. Progress is hampered by the nature of the materials used [Benjamin, 1997].

Strained silicon has higher carrier mobility than bulk silicon but needs to be grown on a substrate with a different lattice constant. One solution is to grow a graded SiGe layer and deposit Si on the top where the Ge can be as high as 30%.

Graded silicon germanium layers, usually called 'virtual substrates', are one industrial approach to producing strained silicon, but they are associated with higher-than-acceptable leakage currents. They often contain threading dislocations, because the layer progressively relaxes as growth continues.

Among other semiconducting materials, diamond has the widest band gap (5.5 eV) with considerable potential for high power throughput at high operating temperatures. However, it is only since about 1990 that the Chemical Vapour Deposition technique (particularly microwave plasma CVD) of growing diamond wafers on semiconductor substrates (e. g., silicon) has opened the door to practical applications of thin film

Chapter 1 Introduction

semiconducting diamond. Progress in the synthesis of high quality diamond films has made them a promising material for many specialised electronic device applications [Buckley-Golder and Collins, 1992; Ralchenko *et al*, 1999]. It is hoped that devices capable of operating at voltages in excess of 10,000 volts and at higher temperatures than other semiconductor materials may soon be available. This thesis is concerned with the fabrication of a working Schottky diode on semiconducting diamond and the testing of its properties for future commercial use.

#### 1.2 Rationale for research

Diamond exhibits a rare combination of physical, optical and thermal properties that make it a very attractive material for many electronic applications. It is extremely hard, it is electrically insulating but can be made conducting, has the highest thermal conductivity at room temperature of any semiconducting material, and is transparent to electromagnetic waves from about 225nm to beyond the infra-red region. Because of these advantages this research attempts to develop a Schottky diode on thin film diamond, and studies the defects that are in the diamond by Deep Level Transient Spectroscopy (DLTS).

We illustrate the properties of diamond and discuss the different methods used for the production of synthetic diamond and conclude that the presence of defects in a diamond sample will have a great effect on the electronic behaviour of a device.

### 1.3 Research Aims and Objectives

The major aims of this research are two-fold:

- (i) to fabricate a working diamond Schottky diode with acceptable characteristics, and

- (ii) to study the defects in a strained silicon Schottky diode fabricated on a virtual substrate.

The objectives of the research programme are:

- To study certain novel group IV semiconductors and their applications.

- To study those defects in diamond that could have a significant effect on the electronic behaviour of the diamond, and to develop an analytical explanation of the behaviour of defects and the subsequent behaviour of the Schottky diode

- To study defects in virtual substrates.

On the basis of the investigation conducted, to provide useful information to guide future research in this field.

## 1.4 Organisation of the thesis

This work is organized as follows:

Chapter 2 is concerned with the investigation of diamond growth and properties, and present a survey of different material systems used in power electronic devices.

Chapter 3 consists of a discussion and analysis of defects in diamond. It also illustrates the use of different techniques (such as temperature dependent current-voltage (I-V) characteristics and DLTS) for the investigation of the electronic behaviour of defects and traps in diamond.

Chapter 4 gives a brief account of defects in silicon and their consequences for the behaviour of silicon devices, as comparison.

Chapter 5 discusses briefly the metals used to fabricate a Schottky diode and illustrates how a Schottky diode is created when a metal is deposited on the surface of a semiconductor. It also introduces techniques for characterising a Schottky diode.

Chapter 6 gives a survey of the experimental techniques, including Laplace DLTS, used in investigating the electronic behaviour of the traps in semiconductors using a Schottky diode.

Chapter 7 introduces the fabrication of a Schottky diode on diamond.

Chapter 8 shows the experimental results obtained from the I-V and capacitance-voltage (C-V) measurements carried out on the fabricated diamond Schottky diode. The results of DLTS measurements are introduced in order to fully electrically characterise the fabricated diamond Schottky diode.

In chapter 9 we introduce a SiGe Schottky diode. We report its excellent characteristics and the experimental results. At the end of this chapter we introduce a comparison between a diamond Schottky diode and a SiGe Schottky diode from the point of view of the C-V measurements.

3

Introduction

Finally, conclusions and suggestions for future work are given in Chapter 10.

## References

Benjamin M. C., thesis "Electronic Properties of SiC and AIN Surfaces and Interfaces". The Surface Science Lab (SSL) North Carolina, North Carolina State University, 107, 1-15 (1997)

Buckley-Golder I. M., and Collins A. T., Diamond and Related Materials, 1, 1083, (1992)

Ralchenko V., Sychov I., and Vlasov I., Diamond and Related Materials, 8, 189 (1999).

# Chapter 2

# Properties and growth of diamond

#### 2.1 Introduction

Silicon diodes have been used in power electronics for many years and their properties and characteristics have been studied in great detail. The increasing proportion of electricity generated by power electronic converters in motor drives, high voltage dc systems, distributed energy resource interfaces, and flexible ac transmission, makes the efficiency and reliability of these converters of the utmost importance. Several of these applications require voltage-blocking capabilities in the tens and hundreds of kV and thus need series connection of many silicon-based power electronic devices to achieve the necessary voltage rating. Power electronic converters may process gigawatts of power between where that power is generated and where it is ultimately utilized, emphasizing the need for highly efficient power electronic converters and systems. All commercial power electronic devices (diodes, thyristors, etc.) are presently silicon-based, but the performance of these systems is approaching its theoretical limit. The development of new power electronic devices based on wide bandgap semiconductor materials would give substantial improvements in the performance of power electronics converter systems in terms of higher blocking voltages, efficiency and reliability as well as reduced thermal requirements [Ozpineci et al, 2002].

Modern power electronic devices have reached the point where progress is hampered by the nature of the materials themselves. For a given size, silicon transistors can only switch so fast, and new materials are needed for high speed switching applications. Similarly, silicon is a poor conductor and so thermally produced carriers

can cause conduction problems. In many high power, high frequency applications vacuum tubes are required, but these are bulky, inefficient and much more prone to failure than semiconductors. It would thus be advantageous to replace such tubes with semiconductors wherever possible and so new semiconductor materials for power device applications are needed [Benjamin, 1997].

Wide bandgap semiconductors like silicon carbide (SiC), gallium nitride (GaN), zinc oxide (ZnO), and diamond, with their superior electrical properties, are candidates likely to meet the enhanced requirements [Tolbert et al, 2003]. These materials are very attractive for certain applications, having many remarkable properties, such as high-temperature capabilities and higher threshold voltages, which make them very promising semiconductor materials for power electronics. However, the large-scale manufacturing of electronic devices requires continuous production of good quality wafers, which is currently a problem. For example, in silicon carbide growth there are still some basic problems that limit the commercial utilisation of the material [Raback, 1999] although recently much larger wafers of SiC have become commercially available.

So what are the advantages of wide bandgap materials? A bandgap is the amount of energy required for an electron to jump from the valence band to the conduction band. Wide bandgap materials have a bandgap energy of, typically, between 3-6 eV. A high bandgap energy gives a higher breakdown voltage, which in turn leads to higher power operation. Threshold voltages are greatly increased and there is a high output impedance because of high resistivity. Although wide bandgap semiconductor-based power devices have these advantages compared with silicon, manufacturing difficulties and other disadvantages limit their widespread use. These disadvantages include: low processing yield because of defects in SiC, processing problems with GaN and single crystal diamond, high cost and limited availability. Only SiC Schottky diodes of relatively low power are commercially available [Ozpineci, 2003].

Wide bandgap semiconductor materials have better electronic characteristics than silicon [see table 2-1 for some characteristics of the most popular wide bandgap semiconductors]. Among these diamond has the widest band gap. Because semiconductors with wide bandgaps can operate at higher temperatures, diamond power devices, potentially, have the capability to operate at higher ambient temperatures than

the other materials. Additionally, a higher electric breakdown field results in power devices with higher breakdown voltages. The breakdown voltage of a diode is expressed as [Raback, 1999, Ozpineci, 2003]:

$$V_B \approx \frac{\varepsilon_r E_C^2}{2qN_P}$$

2.1

where q is the charge of an electron,  $N_D$  is the doping density,  $\varepsilon_r$  is the dielectric constant and  $E_C$  is the electric breakdown field.

| Property                                                                                                     | Si   | GaAs | 6H-SiC | 4H-SiC | GaN  | Diamond |

|--------------------------------------------------------------------------------------------------------------|------|------|--------|--------|------|---------|

| Bandgap, $E_g$ (eV)                                                                                          | 1.12 | 1.43 | 3.03   | 3.26   | 3.45 | 5.54    |

| Dielectric constant, $\varepsilon_r$                                                                         | 11.9 | 13.1 | 9.66   | 10.1   | 9    | 5.5     |

| Electric Breakdown Field, $E_C$ (kV/cm)                                                                      | 300  | 400  | 2500   | 2200   | 2000 | 10000   |

| Electron Mobility, $\mu_n$ (cm <sup>2</sup> .V.s)                                                            | 1500 | 8500 | 500    | 1000   | 1250 | 2200    |

| Hole Mobility, $\mu_p(cm^2.V.s)$                                                                             | 600  | 400  | 101    | 115    | 850  | 850     |

| Thermal conductivity, λ(W/cm. K)                                                                             | 1.5  | 0.46 | 4.9    | 4.9    | 1.3  | 22      |

| Theoretical breakdown voltage of material normalized to a silicon diode, using eqn 2.1 (same doping assumed) | ·    |      | 56     | 46     | 34   | 514     |

| Saturated Electron Drift Velocity, $V_{sat}(x10^7 \text{cm/s})$                                              | 1    | 1    | 2      | 2      | 2.2  | 2.7     |

$\varepsilon = \varepsilon_r \varepsilon_o$  where  $\varepsilon_o = 8.85 \times 10^{-12}$  F/m,  $\varepsilon_r =$  relative permittivity.

Table 2-1 Physical characteristics of silicon and common wide bandgap semiconductors [Raback, 1999, Ozpineci, 2003].

Using equation 2.1, the breakdown voltages of diodes made of the materials in table 2-1 were calculated assuming the same doping density, and the results are shown normalized to the breakdown voltage of a silicon diode. The theoretical breakdown voltages for 6 H-SiC, 4H-SiC, and GaN are respectively 56, 46, and 34 times that of a silicon diode; but for diamond it is 514 times greater. Tolbert *et al*, [2003] have noted that with higher electric breakdown fields, a greater doping density can be introduced in the material than in silicon. This will further increase the breakdown field of the wide bandgap semiconductor diodes.

Another consequence of the higher breakdown field and higher doping density is a width reduction in the drift region of the devices. The required width of the drift region can be expressed as [Raback, 1999, Ozpineci, 2003];

$$w(V_B) \approx \frac{2V_B}{E_C}$$

2.2

A plot of the drift region width versus the breakdown voltages for different types of semiconductors can be seen in figure 2-1 for a breakdown voltage range of 100 to 10,000 V. Diamond, as expected, requires the minimum width while 6H-SiC, 4H-SiC, and GaN follow diamond in order of increasing width. Compared to these, silicon requires approximately a 10 times thicker drift region [Tolbert *et al*, 2003].

Figure 2-1 Width of the drift region for several common materials at different breakdown voltages [Ozpineci *et al*, 2002].

Silicon carbide, gallium nitride, zinc oxide and diamond will be discussed in the following sections.

#### 2.1.1 Silicon carbide

Silicon carbide (SiC) is a wide bandgap semiconductor currently of interest to the semiconductor device industry for use in high temperature, high power voltage, and high frequency devices and sensors [Silly et al, 2004]. In particular it possesses an

electrical field strength one order of magnitude larger than that of silicon, a bandgap of 2.9 eV, and a high thermal conductivity. Silicon carbide is hard, has high heat resistance, strong oxidisation and a small thermal coefficient, which makes it favoured for many technical applications [Werhiet and Schwetz, 2004]. Silicon carbide is also very resistant to radiation damage [Cheng et al, 2002. Silly et al, 2004]. Silicon carbide occurs in many different crystal structures; more than 200 different polytypes. SiC-4H and SiC-6H have the same basic parameters including their crystal structures (Wurtzite (Hexagonal)), melting point (3103 ± 40 K at 35 atm), and density (3219 gcm<sup>-3</sup> at 300 K) [de Mesquita 1967; Harris and Weiner, 1989]. SiC exhibits a higher value of thermal conductivity (3 to 13 times), critical electric field (4 to 20 times), and saturated carrier velocity (2 to 2.5 times) compared to conventional semiconductor materials such as silicon, germanium and gallium arsenide [Lee, 2002].

Schottky diodes constructed from silicon carbide are stable to high temperatures, but there are still a number of factors that limit device performance. One of the most important and critical factors is the formation of low resistivity Ohmic contacts [Lee, 2002]. For applications in silicon-compatible technology, a new process at a lower temperature is required. Furthermore, SiC has a large lattice mismatch to silicon, making it difficult to achieve good performance from heteroepitaxial growth [Kiuchi et al, 2004].

### 2.1.2 Gallium nitride

Gallium nitride (GaN) has some of the advantages of SiC; a direct wide bandgap, high thermal conductivity, and relatively good high frequency performance, so applications of GaN devices have mainly focused on short wavelength optoelectronics and radio frequency uses. GaN and SiC Schottky diodes show similar performance advantages (at similar blocking voltages) compared to Si pn junction diodes. There is a negligible reverse recovery current and consequently a lower switching loss that is independent of the operating temperature. The switching speed and losses of GaN Schottky diodes have been shown to be slightly better than similarly rated SiC diodes. On the other hand, because of its wider bandgap, the forward voltage drop of a GaN Schottky diode is much higher than both Si and SiC Schottky diodes [Ozpineci et al, 2002].

GaN does have some disadvantages compared to SiC; for example, it does not have a native oxide, which is required for MOS devices. Studies are underway to find a suitable oxide since without it GaN MOS devices are not possible. Also, with present technology, GaN boules are difficult to grow, so pure GaN wafers are not available; instead GaN wafers are grown on sapphire or even SiC. Even then, thick substrates are not commercially available. As a consequence, GaN wafers are more expensive than SiC wafers [Ozpineci et al, 2002]. Another disadvantage compared to SiC is its thermal conductivity, which is almost one quarter of that of SiC. This property is crucial in high power, high temperature operation because the heat generated inside the device needs to be dissipated as quickly as possible. The higher the thermal conductivity, the quicker the heat is dissipated. Growing GaN on SiC wafers increases the overall thermal conductivity but it still does not reach the performance of SiC [Ozpineci et al, 2002]. Undesired screw dislocations are observed in gallium nitride films, although they are reduced by growing on a vicinal surface [Goorsky, 2002; Wulfhekel et al, 2004].

Bandgap engineering, through alloying and heteroepitaxial annealing has enabled systems with a broad range of applications. High breakdown electric field and electron saturation velocities make the system suitable for high power applications, as does its overall thermal robustness. Applications, however, require the use of GaN substrates because heat dissipation is a problem when sapphire substrates are used [Arulkumaran et al, 2002, Goorsky, 2002]. Finally, GaN and SiC wafers are, relatively, very expensive.

#### 2.1.3 Zinc oxide

Zinc oxide (ZnO) has a wide bandgap (3.4 eV) but it has not received the same attention as SiC and GaN, probably because this material has been perceived as being useful only in its polycrystalline form in such diverse areas as facial powders and sun cream. Recently, however, large area bulk growth has been achieved, and furthermore, several epitaxial methods have produced excellent material. Also, quantum wells have been successfully grown, by alloying with other materials. Thus ZnO is now being proposed for the same applications as those listed above for GaN, SiC, and diamond. In fact, ZnO recently exhibited several fundamental advantages over its chief competitor; renewed interest in ZnO culminated in the first international Workshop on ZnO in 2000 [Look, 2001]. In general, the electrical properties of bulk ZnO are excellent, as might

have been expected from the low background impurity concentrations. However, good electrical properties also demand low point defect and dislocation concentrations, and bulk ZnO also excels in these aspects. So far, it has proved difficult to dope ZnO p-type, although thin film results look promising [Look, 2001].

#### 2.1.4 Diamond

Diamond is a metastable form of carbon in which each carbon atom is tetrahedrally sp3 bonded to its four nearest neighbours. This strong bonding is responsible for a number of unique physical and chemical properties [Field, 1992, Prawer and Kalish, 1994].

Diamond shows the best theoretical performance, with several times the improvement in every power electronics category compared with every other wide bandgap semiconductor. However, its processing problems have not been solved yet. SiC also still has processing problems, even after years of research, because of the high temperatures required in the process; diamond is a mechanically harder material, needing even higher temperatures for processing, and much research has yet to be done on its processing before it can be used commercially [Ozpineci et al, 2002].

Diamond has amazing properties: because of its fundamental material parameters such as critical field for avalanche breakdown, it has potentially high power throughput and high operational temperature. Also many of its properties are extreme, such as being the hardest solid and the best thermal conductor at room temperature, but, as yet, the electronic applications have been quite limited. Because of diamond's corrosion and radiation resistance, and its stability at high temperatures and pressures, a variety of applications are possible [Mainwood, 2000].

The ability to synthesise diamond from methane and other hydrocarbons (i.e., by Chemical Vapour Deposition) and to deposit the diamond on semiconductor substrates (e. g., silicon) opens many technological applications. Semiconducting diamond exhibits a unique combination of electrical, optical, and physical properties, e. g., low thermal impedance, low dielectric constant, high strength, excellent corrosion resistance, high breakdown voltage, radiation hardness, high saturated carrier velocities at high electric fields, and optical transparency over a wide frequency range [Moazed et