Full-custom integrated circuit design for a pulse frequency modulator.

SCHILLER, Uwe.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/20335/

### A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/20335/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

SHEFFIELD HALLASI LIMATESTY LIBRARY

CITY CAMPLIS FORD STREET

SHEFFIELD S1 1WB

101 536 561 2

Sheffield Hallam University

REFERENCE ONLY

Fines are charged at 50p per hour

- 2 SEP 2004

4.27pm

ProQuest Number: 10700981

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10700981

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC.

789 East Eisenhower Parkway

P.O. Box 1346

Ann Arbor, MI 48106 – 1346

# Full-Custom Integrated Circuit Design for a Pulse Frequency Modulator

# Uwe Schiller

A thesis is submitted in partial fulfilment of the requirements of Sheffield

Hallam University for the degree of Doctor of Philosophy

September 1996

#### **ACKNOWLEDGEMENT**

A number of people supported me during the course of my research and without the help of whom I could have never completed this thesis. Both of my supervisors, Dr J. R. Travis and Dr Z. Ghassemlooy, were actively involved in all stages of my work and I wish to express my sincere gratitude and appreciation for their constant support, encouragement, valuable discussions and guidance throughout the duration of this project and for proof-reading the thesis.

I would also like to thank Dr J. M. Holding for many hours of useful discussions and support. Special thanks goes to all the technicians of the former School of EIT for their technical support, especially to Mr S. Spencer. The help of Jerome Grillot from GEII IUT 'A' Bordeaux I, France, and Michael J. Raabe from Fachhochschule Esslingen, Germany, who carried out project work at the School of EIT is greatly appreciated.

I also thank Ms O. Omar for her help in producing the scanning electron micrographs of the IC layout. I also thank all the members of the Electronics & Communications Engineering Research Group, especially my colleagues, and many of the lecturing staff of the former School of EIT who gave me lots of support and made my stay in England very enjoyable.

The financial help of Sheffield Hallam University is gratefully acknowledged.

Finally, the personal support given to me by my relatives and friends has been valuable indeed. I thank my parents for their encouragement and trust in me. Their Sunday telephone call never let me loose touch with home.

#### **ABSTRACT**

Pulse frequency modulation (PFM) is one of a number of pulse time modulation (PTM) techniques which is suitable for the transmission of video or TV signals through optical fibre. Although several PFM transmission systems have been reported over the past few years, those available commercially usually consist of several components. This thesis describes the design of a novel single chip PFM modulator implemented in 2.4  $\mu$ m CMOS technology. Various design approaches are considered together with a review of circuit and silicon implementation techniques. The fabricated integrated circuit (IC) matches or exceeds the performance of PFM modulators built with commercially available components.

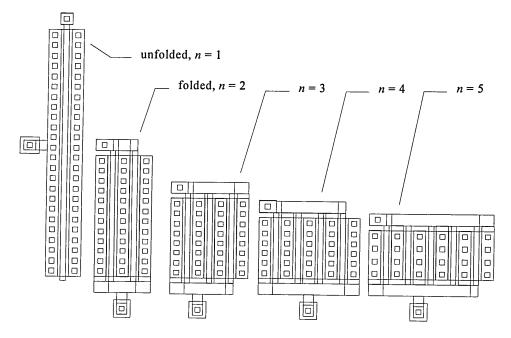

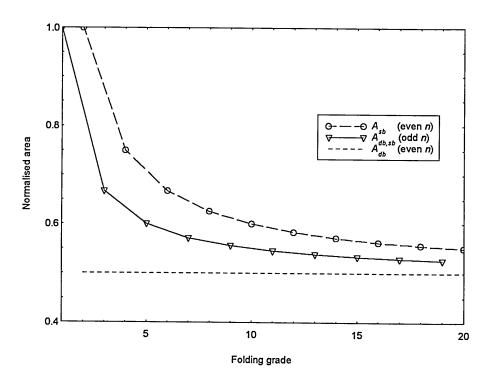

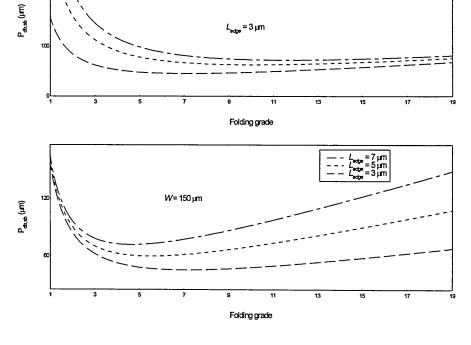

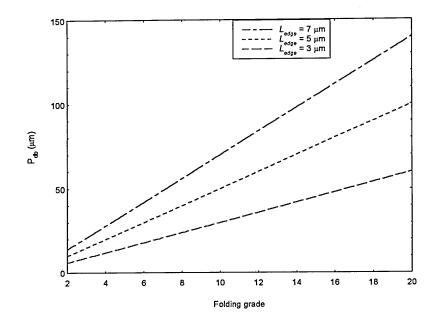

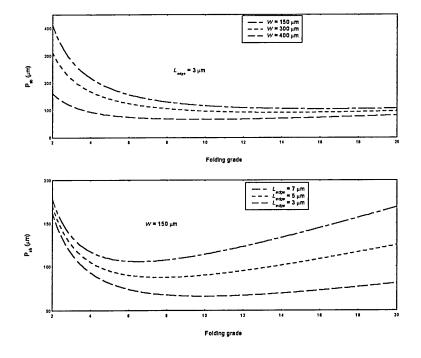

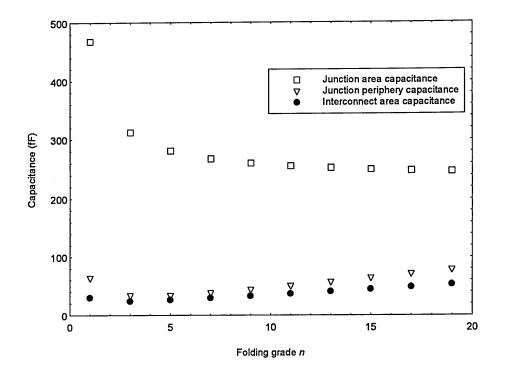

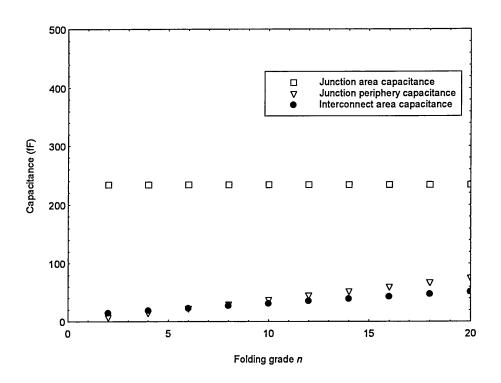

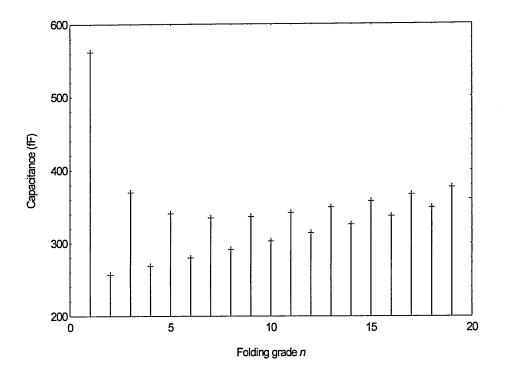

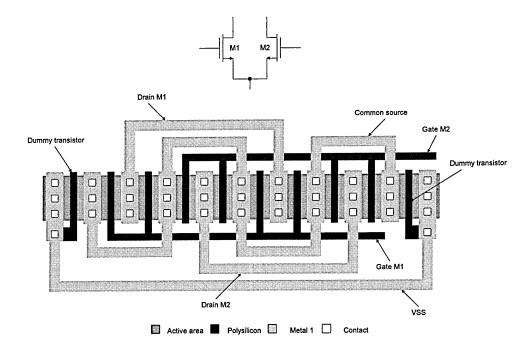

The performance of the design is strongly dependent upon its IC layout. A theoretical analysis of the relationship between the folding grade of a transistor and its parasitic capacitances has been undertaken. Novel equations are developed which enable to trade-off design shape against parasitic capacitance. The lowest drain/source capacitance is always achieved at a folding grade of two regardless of the transistor width to length ratio. The equations developed also show that even folding grades generally achieve a lower parasitic capacitance than odd folding grades.

Performance tests on prototype ICs have shown that the measurement equipment introduces significant capacitive loading. A novel approach of calculating this capacitive loading from transient measurement results is described.

The designed IC was extensively tested in a practical transmission system comprising modulator and demodulator and results of both quantitative and qualitative measurements are reported. At a carrier frequency of 32 MHz and a modulating input signal amplitude of 1 V, the circuit achieves a harmonic and non-linear distortions of -37.87 dB and -56 dB, respectively. These values compare favourably with published results of PFM systems. Further in system tests confirmed that the IC developed is well suited for the transmission of high quality still and moving pictures.

The IC was only compared with the VCO circuits available commercially (Plessey SP1658 and TI SN74S124) since VCOs are the main building block of a PFM modulator and single chip versions are not currently available. Results of the comparison show that the performance of PFM modulators, based on those VCOs, is inferior to the designed circuit whilst requiring a much higher power dissipation. The power dissipation of the designed circuit is 47.5 mW compared to 165 mW and 525 mW for the SP1658 and SN74S124, respectively. Due to the much reduced power dissipation, almost no heat is dissipated from the designed circuit. When operated at its maximum frequency (~ 40 MHz) the temperature of the IC was found to be only 3°C above room temperature.

# **DECLARATION**

I hereby declare that this thesis is entirely my own work and has not been submitted in support of an application of another degree or qualification of this or any other university, institute of learning or industrial organisation.

Uwe Schiller

16 September 1996

# **TABLE OF CONTENTS**

| 1 Introduction                                    | 1          |

|---------------------------------------------------|------------|

| 2 Pulse time modulation techniques                | 6          |

| 2.1 Communication Systems                         | $\epsilon$ |

| 2.2 Comparison of Modulation Techniques           | 8          |

| 2.3 Pulse Time Modulation Techniques              | 11         |

| 2.3.1 PTM schemes                                 | 11         |

| 2.3.2 Modulation spectrum                         | 15         |

| 2.3.2.1 Pulse width modulation                    | 16         |

| 2.3.2.2 Pulse position modulation                 | 19         |

| 2.3.2.3 Pulse interval modulation                 | 19         |

| 2.3.2.4 Pulse interval and width modulation       | 21         |

| 2.3.2.5 Pulse frequency modulation                | 22         |

| 2.3.2.6 Square wave frequency modulation          | 23         |

| 2.4 Comparison of PTM Schemes                     | 24         |

| 2.4.1 Non-linear distortion                       | 26         |

| 2.4.2 Signal-to-noise ratio performance           | 28         |

| 2.5 Theoretical Aspects of PFM                    | 30         |

| 2.5.1 PFM frequency spectrum and spectral overlap | 30         |

| 2.5.2 Modulation and demodulation of PFM          | 32         |

| 2.6 Summary                                       | 33         |

| 3 Integrated circuit design                       | 34         |

| 3.1 IC Design Overview                            | 3.4        |

| 3.2 Silicon Integrated Circuit Technologies                                   | 36 |

|-------------------------------------------------------------------------------|----|

| 3.2.1 Technology overview                                                     | 36 |

| 3.2.2 Theoretical aspects of bipolar and CMOS transistors                     | 39 |

| 3.2.2.1 Bipolar transistor                                                    | 39 |

| 3.2.2.2 CMOS transistor                                                       | 40 |

| 3.2.2.3 Comparison of bipolar and MOS transistor                              | 41 |

| 3.3 IC Design Methodologies                                                   | 42 |

| 3.4 Custom Integrated Circuit Design                                          | 43 |

| 3.5 Computer Aided Design Tools                                               | 44 |

| 3.6 EUROPRACTICE IC Technologies                                              | 46 |

| 3.6.1 EUROPRACTICE                                                            | 46 |

| 3.6.2 Performance consideration for the MIETEC 2.4 µm technology              | 48 |

| 3.7 Design Environment                                                        | 49 |

| 3.8 Summary                                                                   | 51 |

| 4 Full-custom integrated circuit layout                                       | 53 |

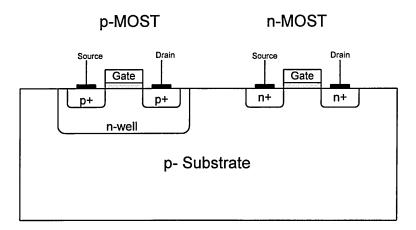

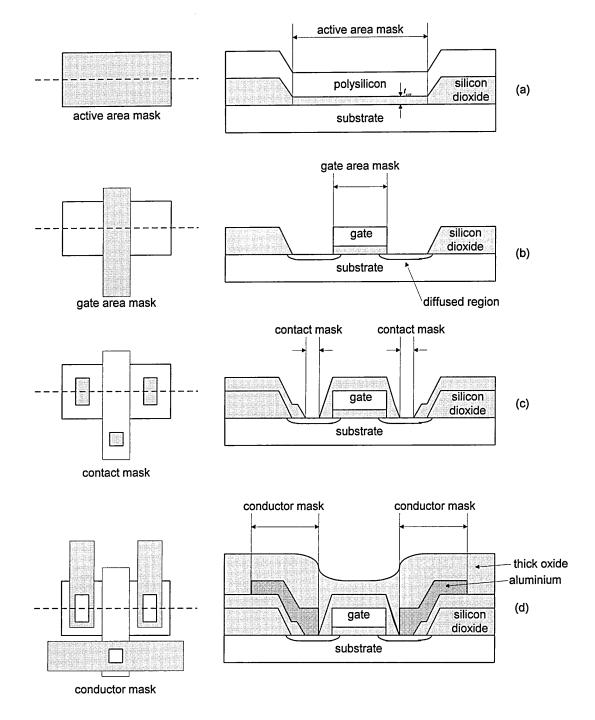

| 4.1 The CMOS Process                                                          | 54 |

| 4.1.1 Structure of a MOSFET                                                   | 54 |

| 4.1.2 Complementary metal oxide semiconductor (CMOS)                          | 56 |

| 4.2 IC Layout                                                                 | 56 |

| 4.3 Optimisation of Folded MOS Transistor Layouts                             | 58 |

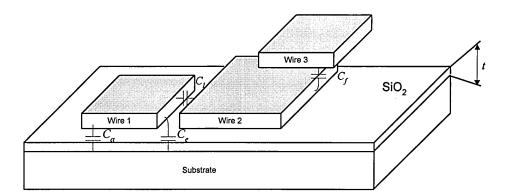

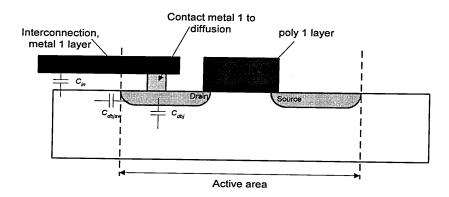

| 4.3.1 Parasitic elements in ICs                                               | 59 |

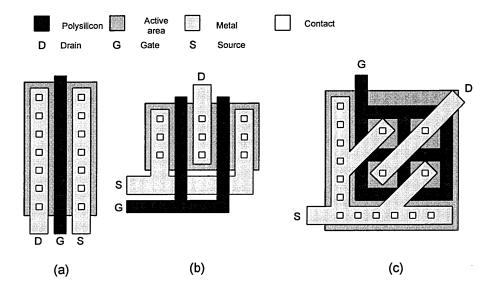

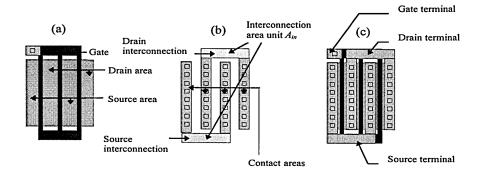

| 4.3.2 Transistor layout methodologies                                         | 60 |

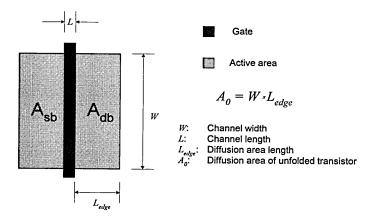

| 4.3.3 Folding of a simple MOS transistor layout                               | 62 |

| 4.3.4 Calculation of parasitic capacitances of a folded MOS transistor layout | 64 |

| 4.3.4.1 Areas of diffused regions                                     | 65         |

|-----------------------------------------------------------------------|------------|

| 4.3.4.2 Perimeter of diffused regions                                 | 67         |

| 4.3.4.3 Areas of interconnections                                     | 70         |

| 4.3.4.4 Capacitance calculations from geometry equations              | 70         |

| 4.3.4.5 Specific calculations for the MIETEC 2.4 $\mu m$ CMOS process | 72         |

| 4.3.5 Concluding remarks on layout optimisation of MOSFETs            | <b>7</b> 4 |

| 4.4 Matching of Components in IC Layout                               | 75         |

| 4.5 Extraction of Parasitic Elements                                  | 77         |

| 4.5.1 Parasitic extraction using MG IC Extract                        | 77         |

| 4.5.2 Software problems within MG's IC Extract                        | 78         |

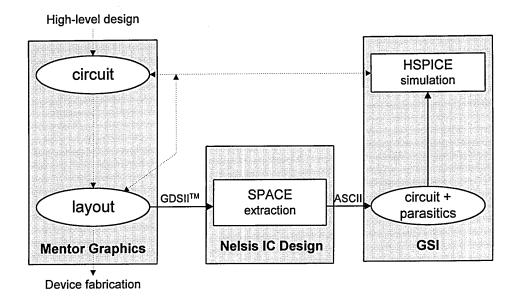

| 4.5.3 Parasitic extraction with SPACE                                 | 78         |

| 4.6 Summary                                                           | 80         |

| 5 CIRCUIT DESIGN AND DESCRIPTION                                      | 82         |

| 5.1 Overall Circuit Description                                       | 82         |

| 5.2 Voltage Controlled Oscillator Design                              | 83         |

| 5.2.1 Types of VCOs                                                   | 83         |

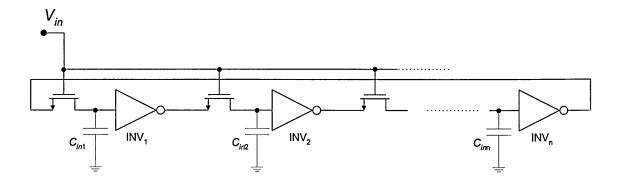

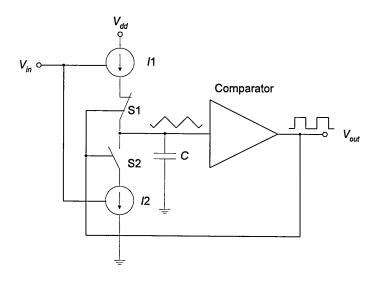

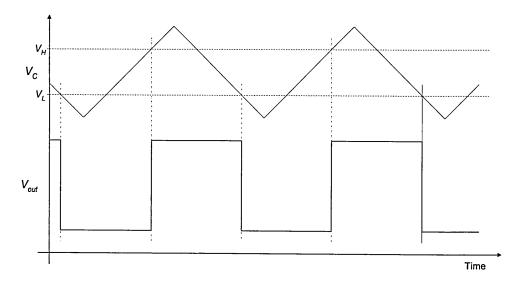

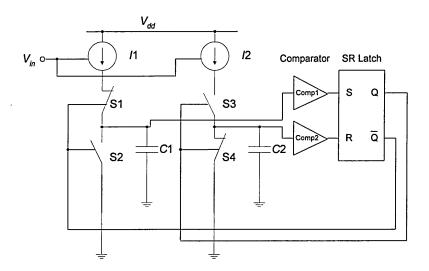

| 5.2.2 Grounded capacitor based VCO design                             | 89         |

| 5.2.2.1 Single capacitor oscillator                                   | 90         |

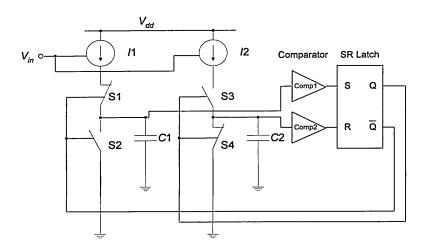

| 5.2.2.2 Double capacitor oscillator                                   | 92         |

| 5.2.2.3 Switching and comparison                                      | 94         |

| 5.2.2.4 Final VCO circuit diagram                                     | 94         |

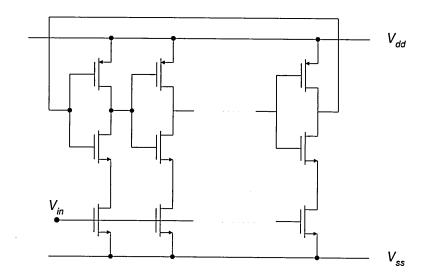

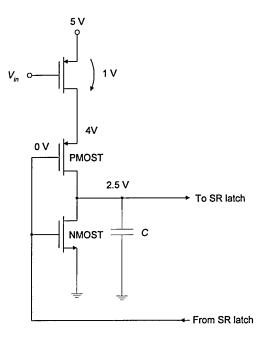

| 5.2.3 Voltage controlled current sources                              | 95         |

| 5.3 VCO Linearization Scheme                                          | 100        |

| 5.4 Pulse Generator                                                   | 102        |

|   | 5.5 Summary                                                                   | 102 |

|---|-------------------------------------------------------------------------------|-----|

| 6 | SUBCIRCUIT IMPLEMENTATION, SIMULATION AND MEASUREMENTS                        | 104 |

|   | 6.1 Initial Simulations and Tests                                             | 104 |

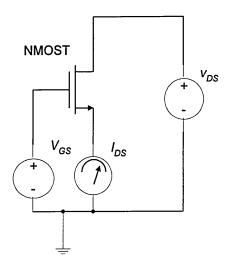

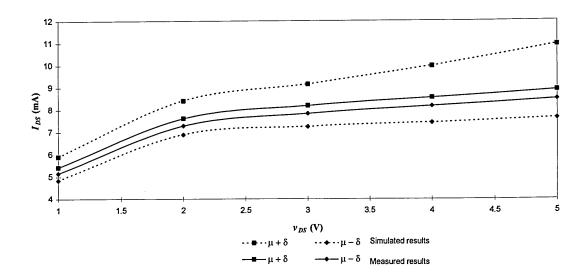

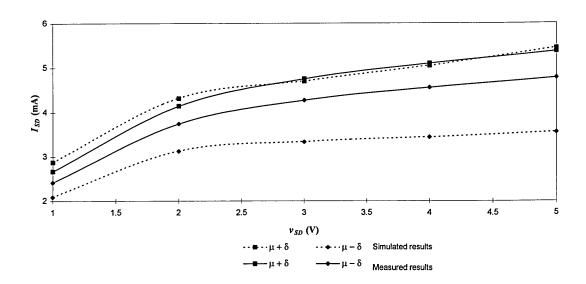

|   | 6.1.1 Single transistor DC simulations and measurements                       | 106 |

|   | 6.1.2 Transient simulations and practical measurement - capacitive loading of | •   |

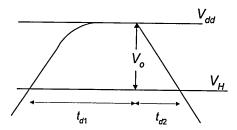

|   | measuring equipment                                                           | 108 |

|   | 6.1.3 Concluding remarks on initial simulations and tests                     | 112 |

|   | 6.2 Determination of Design and Layout Parameters                             | 112 |

|   | 6.2.1 Voltage controlled oscillator                                           | 112 |

|   | 6.2.2 Pulse generation circuitry                                              | 123 |

|   | 6.2.3 Second design submission                                                | 124 |

|   | 6.2.4 Voltage to current converter                                            | 127 |

|   | 6.3 Summary                                                                   | 133 |

| 7 | RESULTS AND DISCUSSIONS                                                       | 134 |

|   | 7.1 Final PFM Modulator Implementation                                        | 134 |

|   | 7.1.1 Complete circuit diagram                                                | 134 |

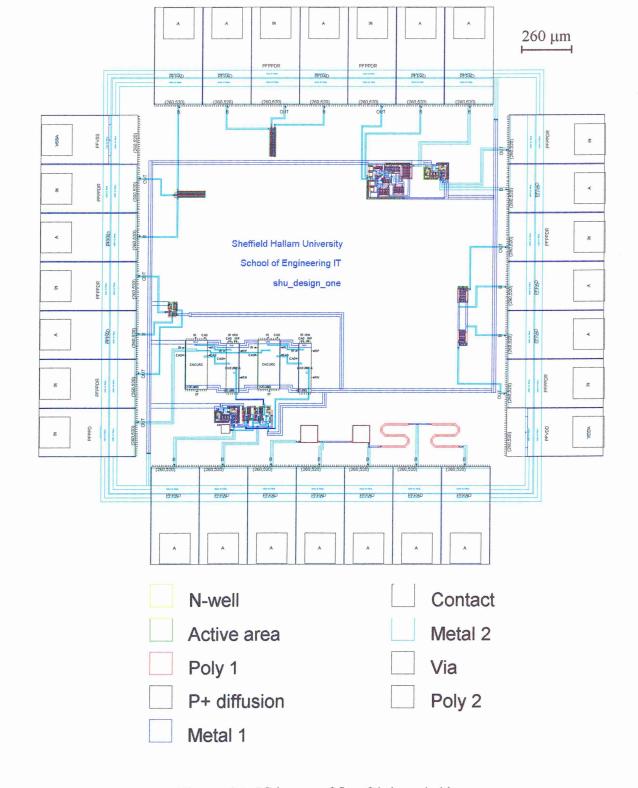

|   | 7.1.2 IC layout of PFM modulator                                              | 134 |

|   | 7.1.3 Simulation results                                                      | 138 |

|   | 7.2 The Fabricated PFM Modulator Chip                                         | 142 |

|   | 7.3 Measurements                                                              | 145 |

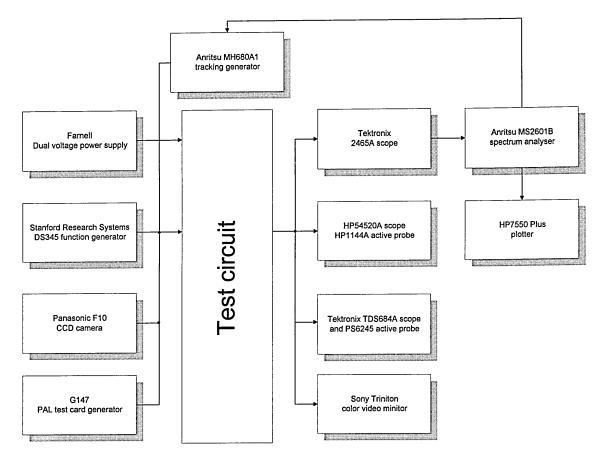

|   | 7.3.1 Measurement setup                                                       | 145 |

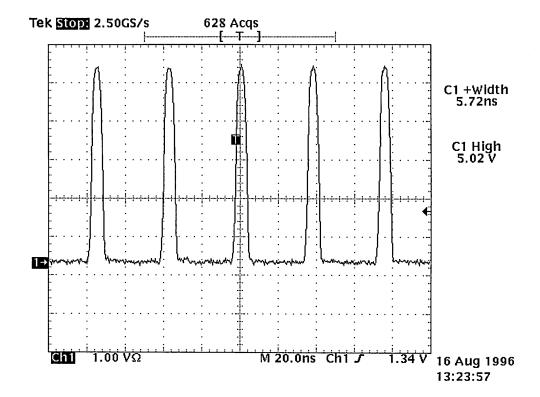

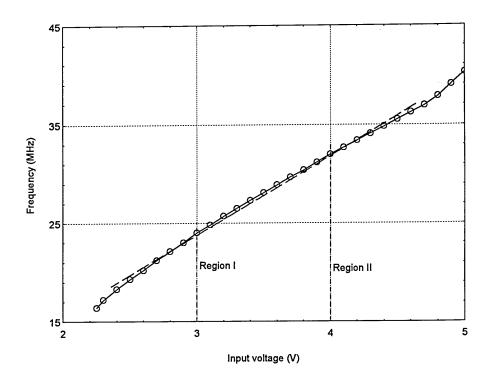

|   | 7.3.2 Measurement of pulse width and linearity                                | 146 |

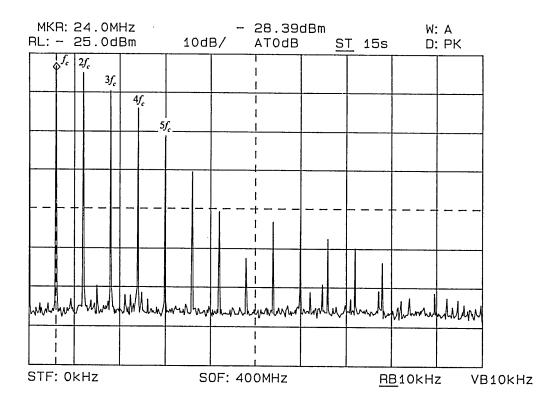

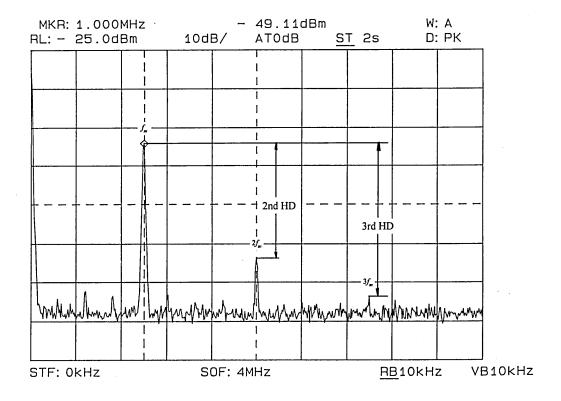

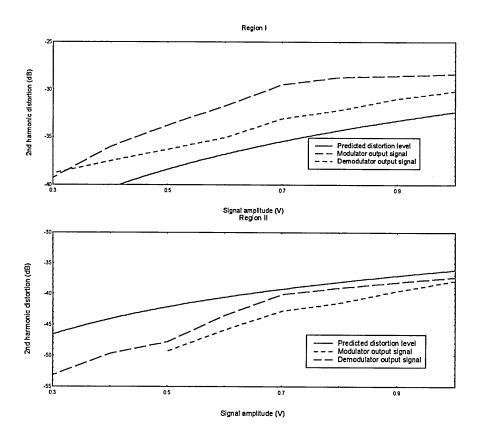

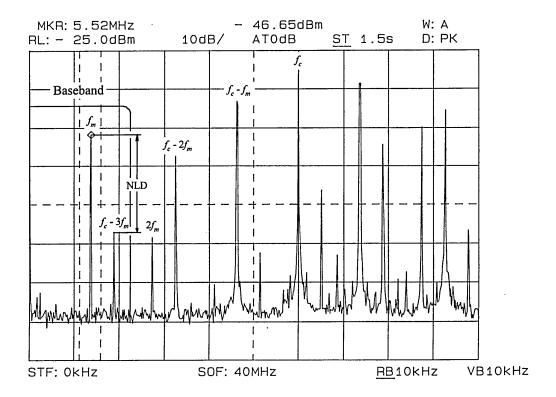

|   | 7.3.3 Harmonic and non-linear distortion measurements                         | 154 |

|   | 7.3.4 Qualitative and quantitative measurements of linearity                  | 159 |

| 7.3.5 Video transmission tests                                          | 162  |

|-------------------------------------------------------------------------|------|

| 7.4 Comparison of Simulation and Measurement Results                    | 165  |

| 7.5 Advantages of the Designed PFM Modulator                            | 167  |

| 7.6 PFM Modulator Specifications                                        | 170  |

| 7.7 Summary                                                             | 172  |

| 8 CONCLUSIONS AND SUGGESTIONS FOR FURTHER WORK                          | 173  |

| 8.1 Conclusions                                                         | 173  |

| 8.2 Suggestions for Further Work                                        | 176  |

| References                                                              | 178  |

| APPENDICES                                                              |      |

| Appendix A: Alcatel MIETEC 2.4 μm CMOS technology                       | A-1  |

| Appendix B: Measurement and calculations of capacitive loading          | A-5  |

| Appendix C: Extracted HSPICE netlist of PFM modulator chip layout       | A-10 |

| Appendix D: Full-custom IC design flow using Mentor Graphics IC Station | A-14 |

# CHAPTER 1 INTRODUCTION

# 1 Introduction

Since the invention of the electric telegraph in the 1830s communication engineering has revolutionised the way our society is exchanging information. All the early telegraph systems relied on electrically conductive wire connections between information source and destination. Wireless (radio) communications were demonstrated in England towards the end of the last century. The invention of the vacuum diode and later the vacuum triode had a major impact on the development of wireless communications. The subsequent development of semiconductors in the form of initially the transistor and later the integrated circuit (IC) has further revolutionised communication systems.

The modern day requirements for large volumes of information transfer has lead to demands for increasingly greater bandwidth transmission channels. For wireless communications this is achieved by increasing the carrier frequencies into the Gigahertz range but this may not be practicable for certain applications due to the increased system cost. Optical fibre, however, provides also the necessary transmission medium for wide bandwidths. Nowadays, with optical fibres having an attenuation of less than 1 dB/km very large distances can be covered and transmission rates of more than 1 Gbits/sec can be achieved.

Early optical fibre communication systems used either purely analogue or digital modulation techniques. Analogue modulation techniques could not deliver the required signal-to-noise ratio (SNR) over long distances and were effected by non-linearity associated with the optical transmission. Digital techniques could overcome these problems but required more hardware and were not bandwidth efficient. In addition, television (TV) signals required a very high data rate and resulted in high costs for fast digital transmission and switching circuitry. In the mid 1970s and early 1980s pulse time modulation (PTM), based on work published in 1947 [Cooke et al., 1947] received a renewal of interest. PTM characteristics are intermediate between purely analogue or digital implementations. Since the form of the modulated carrier is similar to a binary pulse pattern the received signal is not effected by optical source and channel non-linearities and can be routed through logic circuitry. In addition, no analogue to digital conversion is necessary reducing the system's cost. It has been shown that this technique can deliver a better SNR than purely analogue modulation while maintaining a better spectrum efficiency than purely digital techniques [Wilson et al., 1995].

Several PTM techniques have emerged over the years and been proven to be suitable for transmitting various kind of signals. Pulse position modulation (PPM) and pulse width modulation (PWM) have been proven by Holden [1975], Dibiase [1987] and Tanaka, Okamura [1991]. Other modulation techniques include pulse interval (PIM) and pulse interval and width modulation (PIWM) [Wilson *et al.*, 1992]. Pulse frequency modulation (PFM) and square wave frequency modulation (SWFM) have, in particular, been shown to be ideal for the transmission of TV and high definition TV (HDTV) signals over optical fibre [Heatley, 1982; Wilson *et al.*, 1991; Li *et al.*, 1992].

The development of ICs has contributed significantly to advances in communication systems. The evolution of ICs is almost unparalleled by any other engineering

discipline. The first integrated circuit was developed only 40 years ago and comprised a few transistors. Today, ICs containing 5 million transistors per chip are widely available. The development of IC design is characterised by ever increasing miniaturisation and functionality on one single chip. The physical size of modulation and demodulation circuits, for example, has shrunk with the increasing complexity of ICs.

This thesis investigates possible designs and the implementation of a CMOS single chip pulse frequency modulator. Design approaches are considered together with a review of circuit and silicon implementation techniques and novel solutions are determined and comparisons of simulated and practical performance given.

In Chapter 2 pulse time modulation techniques are introduced. General characteristics of each PTM scheme are given and modulation and demodulation techniques are presented. PWM, PPM, PFM and SWFM are compared with regard to non-linear distortion (NLD), harmonic distortion (HD) and signal-to-noise ratio performance. Reasons are given why PFM is a preferred modulation scheme for transmission of video or TV signals. The chapter concludes with more detailed theoretical aspects of PFM.

An overview of integrated circuit design is given in Chapter 3. Silicon IC technologies are compared and reasons are given for selecting CMOS as the preferred technology for implementing the PFM modulator. Furthermore, IC design methodologies are introduced and an overview of custom IC design is given. This is followed by a summary of the available IC technologies through EUROCHIP/EUROPRACTICE with

a performance evaluation of the Alcatel MIETEC 2.4 µm CMOS technology. This chapter concludes with a short introduction to the design environment employed.

Chapter 4 introduces full-custom IC layout with regard to CMOS technologies. The performance of folded MOS transistor layouts is theoretically analysed and the relationship between folding grade of the MOS transistor and important parasitic capacitances is investigated. Equations are given which allow the designer to trade-off design shape of the transistor and value of parasitic capacitances associated with the transistor and its IC layout. The importance of component matching in IC layouts is also discussed. Extraction of parasitic elements from the layout information is presented together with a brief evaluation of two different software extraction tools. During that investigation, it was found that one of the extraction tools, Mentor Graphic's IC Extract, had a faulty software routing calculating parallel resistivity.

The PFM modulator circuit design and description is given in Chapter 5 with subcircuit implementations, simulations and measurements presented in Chapter 6. Chapter 6 also investigates the accuracy of the SPICE transistor models provided. Furthermore, the capacitive loading of prototyping ICs by measurement equipment is investigated and a novel approach is described which allows the determination of this loading from transient measurement results.

Chapter 7 presents the final PFM modulator implementation. Results of measurements taken on the fabricated IC were used to determine its performance and suitability for transmission of video or TV signals. These measurements included time measurements

to determine pulse width and quality of transmitted signals, spectral measurements to determine spectral overlap, harmonic distortion and linearity and qualitative measurements to determine the system performance for video transmission. Differences between simulated and measured results are discussed. A comparison between the designed IC and commercially available PFM modulators is also carried out. This chapter concludes with the designed IC specification.

Conclusions resulting from the work undertaken are presented in Chapter 8 together with suggestions for future work.

# **CHAPTER 2**

PULSE TIME MODULATION TECHNIQUES

# 2 Pulse time modulation techniques

# 2.1 Communication Systems

In general terms, an information system consists of a source (transmitter) and a destination (receiver). In order for the information to be transferred between these two it is usually necessary to change its format to suit the transmission media. For example, information transfer between human beings may be converted into sound pressure waves for transmission through a gas (speech). Over longer distances the sound pressure waves may be converted directly into electrical potentials for transmission through copper cable or into light for transmission through optical fibre. The simple direct conversion process makes very inefficient use of the transmission media and often the characteristic of the information itself (such as wavelength or amplitude) makes it unsuitable for transmission.

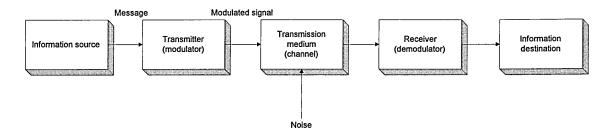

Figure 2.1: Block diagram of a communication system

The message is therefore usually modulated to enable efficient transmission through the selected media, as shown in Figure 2.1. Modulation also allows more than one message to be transmitted at a given time. Associated with the transmission media there will be attenuation and possibly contamination of the signal through noise and interference. If the transmission channel is very long the signal may need intermediate amplification

during its journey. At the receiving end the original signal must be recovered by demodulation. Recovering an exact copy of the waveform is almost impossible since the signal is always distorted to some degree by noise and non-linearity of the system. The quality of the transmission system is dependent upon how precisely the original message can be reproduced and this is normally measured in terms of the signal-to-noise ratio.

The first telegraphic system developed in the 1830s relied on a wired connection between source and destination. Wireless communication was first shown at the end of the last century. In today's communication technology, optical fibre cables are replacing copper cables because of the excellent features of optical fibres such as low transmission loss (< 1.0 dB/km), wide bandwidth, small physical size and immunity to electromagnetic interference [Ghassemlooy *et al.*, 1993]. To make full use of what is an almost ideal transmission channel and to produce a communication system which is cost effective as well as bandwidth efficient the choice of modulation format is of prime importance.

The various modulation schemes that exist can be grouped into three main categories, analogue, digital and pulse modulation. In analogue modulation the properties of a sinusoid carrier frequency, such as amplitude, frequency or phase are changed by the modulating signal. Examples are amplitude modulation (AM) where the amplitude of the carrier is proportional to the modulating signal, frequency modulation (FM) where the instantaneous frequency of the carrier is determined by the signal and phase

modulation (PM) where the instantaneous phase of the carrier is related to the input signal.

In digital modulation, the modulating signal is first converted into a digital form by sampling and quantizing the signal. This process will loose some information but this loss is minimised by selecting a quantization interval which is less than the sensitivity of the receiver. Quantization results in N preselected levels where each level covers a range of input signals. Numerical values will be assigned to these N levels which will then be converted into a binary format before being transmitted. Since the binary code consists only of logic 0s and 1s, the receiver has only to distinguish between these two states and this improves the overall performance of the system.

In pulse modulation, the carrier is, in most cases, a periodic sequence of constant amplitude pulses and the modulating signal is used to vary some properties of the pulse such as, width, position or repetition rate.

# 2.2 Comparison of Modulation Techniques

Since both, analogue and digital signals can be transmitted over fibre optics it is important to first compare advantages and disadvantages of analogue and digital modulation schemes.

In analogue modulation schemes the optical source is modulated in a continuous manner resulting in a variation of the intensity of the optical source. Known modulation

schemes (e.g. AM or FM) can be used to modulate the signal in the first instance followed by direct intensity modulation of the optical source. It is a very simple, bandwidth-efficient scheme. The disadvantage of this technique is that electro-optic converters are inherently non-linear and therefore introduce distortion. The non-linearity of a laser diode (LD), for example, gives rise to harmonics and intermodulation and it attenuates higher frequency components [Tucker et al., 1983; Lin et al., 1990]. The optical fibre introduces additional distortion [Royset et al., 1994; Walker, 1994] and therefore, the achievable signal-to-noise ratio is often very low [Senior et al., 1990].

Most of the problems associated with analogue transmission can be overcome by using digital modulation schemes such as pulse code modulation (PCM). This scheme is substantially immune to source non-linearity and has a better SNR performance than analogue schemes [Senior *et al.*, 1990]. However, digital systems require much more complex circuitry, resulting in an increased overall cost of the system. In addition, digital modulation requires a much larger bandwidth compared with analogue techniques. However, these latter problems can be overcome by employing code compression techniques but this is at the expense of further increase in complexity and cost [Wilson *et al.*, 1993; Rhomberg, 1981].

With the development of fibre transmission systems a third modulation technique, called pulse time modulation was reintroduced. First investigations into PTM techniques were carried out in the late 1940s [Cooke *et al.*, 1947] but it was not until the development of optical fibre systems in the late 1970s early 1980s that there was a revival of research interest and system development in that area [Rhomberg, 1981].

PTM can be used to overcome problems associated with purely analogue or digital methods. The characteristics of PTM techniques are intermediate between analogue and digital implementations. In PTM, the modulated carrier is a periodic sequence of pulses with a constant amplitude but variable pulse edge, width, position or repetition rate. Since the form of the generated signal is similar to a binary pulse pattern, the received signal is not affected by channel non-linearities and can also be routed through logic circuitry [Dibiase *et al.*, 1987].

PTM has the ability to trade-off performance with bandwidth which is particularly useful in fibre communication systems [Wilson et al., 1993]. This unique feature can be exploited when designing systems having different SNR requirements. Thus, low speed optical sources such as light emitting diodes (LEDs) may be used for short distance applications while optical amplification and soliton techniques may be employed for long distance, terrestrial or undersea routes. (A soliton is an optical pulse in which the natural dispersion of the optical fibre is compensated exactly by its non-linearity; this allows an isolated soliton to propagate over a large distance without dispersion [Senior et al., 1995]).

As PTM techniques employ a pulse format no consideration has to be given to LED or LD non-linearities as with direct intensity modulation schemes. Furthermore, some PTM schemes make use of very narrow pulses having a very high peak optical power with a low mean transmitted power, hence ensuring a good SNR performance whilst securing a long lifetime for the optical device.

Simple LEDs are often used for low cost, short distance applications whereas injection laser diodes (ILDs) are used for longer distances and high capacity systems [Wilson *et al.*, 1995]. ILDs are well suited for PTM schemes which vary the properties of a train of narrow pulses since these techniques exhibit a high optical peak power whilst having a low average power thus enhancing the lifetime of the ILDs.

# 2.3 Pulse Time Modulation Techniques

#### 2.3.1 PTM schemes

By using PTM the information is conveyed in a time dependent feature of a constant amplitude carrier as summarised in Table 2.1.

Table 2.1: PTM methods [Wilson et al., 1995]

| Variable                                                                                  |

|-------------------------------------------------------------------------------------------|

| Position Width (duration) Interval (space) Interval and width Frequency (repetition rate) |

|                                                                                           |

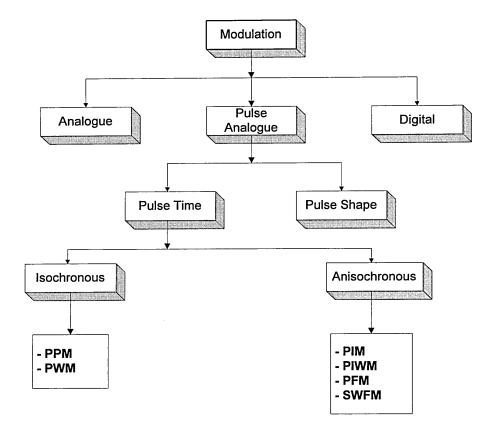

One possible classification of PTM techniques, based on the sampling waveform's fundamental spectral component under modulation conditions, has been described by Wilson *et al.*, [1993] and is shown in Figure 2.2. This classification does not include some newly investigated digital pulse time modulation techniques [Wilson *et al.*, 1995; Ghassemlooy *et al.*, 1995].

Figure 2.2: Modulation tree

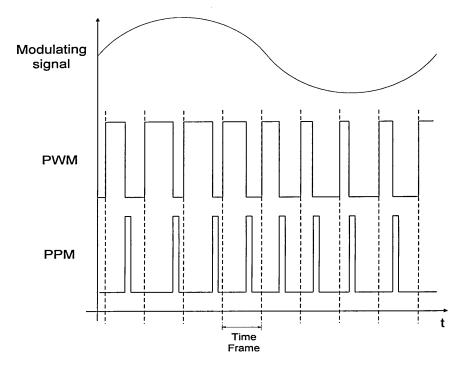

In PWM, sometimes referred to as pulse duration modulation (PDM), the width (duration) of the carrier signal is changed without effecting the time frame, hence the duty cycle is changed dependent upon the sampled modulating input signal. PPM may be generated by detecting the modulated edge of the PWM waveform. Therefore, the information is conveyed in the variable position of a narrow pulse within a predetermined time frame. Both modulation techniques may be classified as isochronous since the sampling time and hence the time frame, is constant (Figure 2.3) [Wilson et al., 1993].

In PIM the information is carried within the constantly changing intervals between narrow pulses, the interval being dependent upon the amplitude of the modulating

Figure 2.3: PWM and PPM techniques

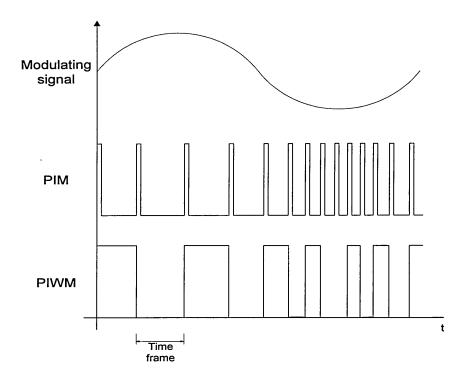

signal. PIWM is derived from PIM to form a waveform where the information is conveyed in both marks and spaces. The difference between this and PWM or PPM is that in PIM/PIWM the next time frame commences immediately after the current time frame has finished and no fixed time frame for sampling is employed (Figure 2.4). These modulation schemes are therefore described as anisochronous [Wilson *et al.*, 1993].

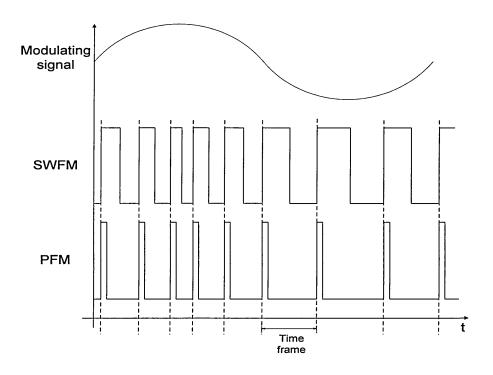

In PFM, the repetition rate of a pulse train with fixed pulse width changes according to the amplitude of the modulating signal. SWFM is closely related to PFM and analogue FM. In SWFM a square wave is used as carrier compared to a sine wave as in FM. Again, these two modulation schemes may be categorised as anisochronous since there is no fixed time frame (Figure 2.5) [Wilson *et al.*, 1993].

Figure 2.4: PIM and PIWM techniques

Figure 2.5: SWFM and PFM techniques

PWM and PPM are well know schemes and have been widely used in optical fibre applications [Holden, 1975; Dibiase, 1987; Providakes *et al.*, 1991; Wickramasinghe *et al.*, 1996]. They can easily be time multiplexed due to their fixed time frame and demultiplexing can be achieved with only moderate circuit complexity. Comparatively little work has been published on PIM and PIWM although these schemes offer certain benefits such as self-synchronising code for PIWM [Sato *et al.*, 1979; Wilson *et al.*, 1992]. PFM has been adopted for optical fibre transmission of video and broadcast quality TV signals as well as for CCTV systems. SWFM is being used for transmission of HDTV and other wideband instrumentation signals [Kanada *et al.*, 1982; Heatley *et al.*, 1984; Li *et al.*, 1992; Wickramasinghe *et al.*, 1995].

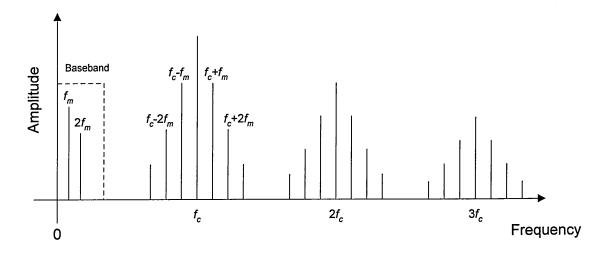

## 2.3.2 Modulation spectrum

All PTM techniques produce a modulation spectrum with some common features. Modulation will always produce a declining set of side tones centred around the carrier frequency and its harmonics. The side tones are separated by an amount equal to the modulating signal frequency. Some PTM techniques have the baseband components present in their modulation spectra as shown in Figure 2.6. This feature and the number and magnitude of the side tones present may be used to identify different PTM techniques.

Some PTM techniques require sampling of the signal prior to the modulation. The modulating signal can either be uniformly or naturally sampled. Naturally sampled modulators operate directly on the input signal whereas uniformly sampled modulators

may employ a sample and hold amplifier which samples the signal at predefined time intervals.

Figure 2.6: General PTM frequency spectrum

After converting the signal from optical to electrical, the PTM waveform is recovered by amplitude detection. Demodulation of PTM depends on the spectrum. If the spectrum contains the baseband component the signal is demodulated by employing a low pass filter. If no baseband component is present, then a conversion of this particular PTM signal into a PTM signal containing the baseband is required before low pass filtering it.

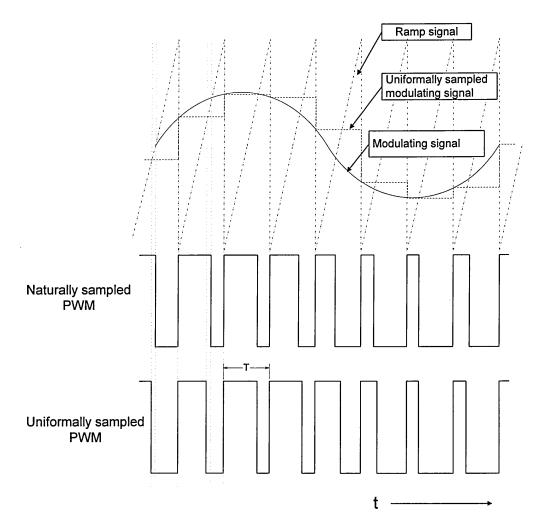

#### 2.3.2.1 Pulse width modulation

In PWM the duty cycle of a constant pulse frequency carrier signal is changed by the sampled modulating signal. The PWM waveform may be generated by comparing the uniformly or naturally sampled input signal with a linear ramp signal. Figure 2.7 shows the principle difference in uniformly and naturally sampling. If a triangular waveform is

used instead of a ramp signal a double edge modulated PWM waveform will be generated.

Figure 2.7: Trailing edge naturally and uniformly sampled PWM

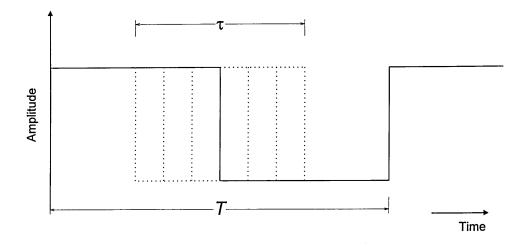

The modulation index M (0<M<1) may be defined such that the maximum modulation occurs when the peak-to-peak modulating signal amplitude is equal to the ramp signal amplitude [Wilson *et al.*, 1995]. The modulation index may therefore be expressed as follows:

$$M = \frac{\tau}{T} \tag{2.1}$$

where  $\tau$  is the pulse width deviation and  $T = 1/f_c$  with  $f_c$  being the carrier frequency (Figure 2.8). The unmodulated pulse width is T/2 (i.e. a square wave).

Figure 2.8: Modulated PWM waveform

The naturally sampled PWM modulation spectrum in which the trailing edge is modulated can be expressed as follows [Wilson *et al.*, 1993]:

$$v(t) = \frac{1}{2} - \frac{M}{2} \sin(\omega_m t) + \sum_{n=1}^{\infty} \frac{\sin(n\omega_c t)}{n\pi} - \sum_{n=1}^{\infty} \frac{J_0(n\pi M)}{n\pi} \sin(n\omega_c t - n\pi)$$

$$-\sum_{n=1}^{\infty} \sum_{k=\pm 1}^{\pm \infty} \frac{J_k(n\pi M)}{n\pi} \sin[(n\omega_c + k\omega_m)t - n\pi]$$

(2.2)

Here  $\omega_m$  and  $\omega_c$  are the modulating signal and carrier frequencies, respectively and  $J_k(x)$  is the Bessel function of the first kind, order k. Since the PWM signal clearly contains a baseband component (second term) it can be demodulated by employing a simple low-pass filter. Also, since neither the frequency nor the amplitude of the carrier signal is affected by the modulation index the technique may be classified as isochronous [Wilson *et al.*, 1995].

#### 2.3.2.2 Pulse position modulation

Pulse position modulation may be generated by detecting the modulated edge of the PWM waveform. In this case, the information is conveyed by the variable position of a narrow pulse within a predetermined time frame. The naturally sampled PPM modulation spectrum may by given as [Wilson *et al.*, 1993]:

$$v(t) = \frac{A\omega_{c}\tau}{2\pi} + AM\cos(\omega_{m}t)\sin(\omega_{m}\frac{\tau}{2})$$

$$+ \frac{2A}{\pi}\sum_{k=-\infty}^{\infty}\sum_{n=1}^{\infty}J_{k}(n\pi M)\frac{\sin[(n\omega_{c}+k\omega_{m})\frac{\tau}{2}]}{k}\cos[(n\omega_{c}+k\omega_{m})t]$$

(2.3)

Again, a baseband component (second term) is generated whose amplitude depends on pulse width and input frequency. But this is differentiated and, therefore, for demodulation it is essential to convert the signal into a PWM waveform before low pass filtering. The conversion process will require the clock signal which may be obtained by employing a phase locked loop [Wickramasinghe *et al.*, 1996].

#### 2.3.2.3 Pulse interval modulation

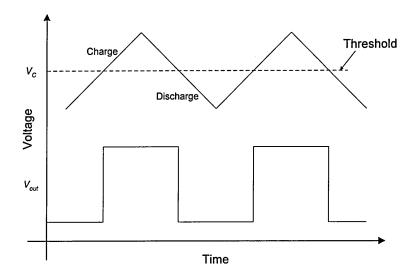

In pulse interval modulation, the amplitude of the modulating signal is encoded as a variable interval between narrow pulses. The PIM waveform may be generated by comparing the modulating input signal with a ramp signal. When the amplitude of the ramp reaches the amplitude of the modulating signal, a narrow pulse is generated and the ramp signal is reset to its initial value. The main difference between this and PWM or PPM is that the next time frame commences immediately after the current one has finished. Thus, no fixed time frame for sampling is employed.

The PIM modulation spectrum may be presented as follows [Wilson et al., 1995]:

$$v(t) = \left(\frac{\omega_{0}}{2\pi} \sum_{p=0}^{\infty} M^{p} \cos^{p}(\omega_{m}t)\right) \cdot \left\{1 + 2\sum_{k=\pm 1}^{\infty} \sum_{n_{1}=-\infty}^{\infty} \sum_{n_{2}=-\infty}^{\infty} J_{n_{1}}(kB_{1})J_{n_{2}}(kB_{2})\cos[(kA_{0}\omega_{0} + (n_{1} + 2n_{2})\omega_{m})t]\right\}$$

(2.4)

where

$$A_{p} = \sum_{r=0}^{\infty} \left(\frac{M}{2}\right)^{2r} \frac{(p+2r)!}{(p+r)!r!} \qquad (p=0,1,2)$$

and

$$B_{p} = \frac{2\omega_{0}}{p\omega_{m}} \left(\frac{M}{2}\right)^{p} A_{p} \qquad (p = 1,2)$$

where  $\omega_0$  is the unmodulated pulse train and  $\omega_m$  is the modulating signal frequency.

The last term of equation (2.4) indicates that the spectral profile around the carrier fundamental and all its harmonics is heavily dependent upon the modulation index. The first term indicates that, in addition to the baseband component itself, there is also a series of baseband harmonics present. The amplitude of the baseband component and its harmonics is a function of the modulation index (0 < M < 1) with the harmonics becoming negligible at lower modulation indices. In contrast to PPM, the amplitude of the baseband component is not influenced by the modulating frequency. Therefore, for low modulation indices (< 10%) demodulation may be achieved by low pass filtering. If the full modulating range is used, demodulation may be carried out by regenerating the original ramp signal employing the PIM pulse train to reset and initiate the ramp. This is followed by either low pass filtering for naturally sampled signals or passing the

signal through a sample-and-hold amplifier before low pass filtering if the modulating signal was uniformly sampled.

#### 2.3.2.4 Pulse interval and width modulation

Pulse interval and width modulation is derived from PIM and the information is conveyed in both mark and space. The PIWM spectral profile may be represented by [Wilson *et al.*, 1995]:

$$v(t) = \frac{V}{2} \left\{ 1 + \sum_{k=1}^{\infty} \sum_{n_1 = -\infty}^{\infty} \sum_{n_2 = -\infty}^{\infty} \frac{\sin\left(k\frac{\pi}{2}\right)}{k\frac{\pi}{2}} J_{n_1}(kB_1) J_{n_2}(kB_2) \cdot \cos\left[\left(kA_0 \omega_0 + \left(n_1 + 2n_2\right) \omega_m\right) t\right] \right\}$$

(2.5)

where

$$A_{p} = \sum_{r=0}^{\infty} \left(\frac{M}{2}\right)^{2r} \frac{(p+2r)!}{(p+r)!r!}$$

$$(p = 1,2)$$

and

$$B_{p} = \frac{2\omega_{0}}{p\omega} \left(\frac{M}{2}\right)^{p} A_{p}$$

where V is the PIWM signal amplitude and  $A_0$  is calculated from  $A_p$ , with p = 0.

The PIWM spectrum contains no baseband component and has a side tone pattern around the carrier fundamental and all its odd harmonics. The absence of the baseband component results in decreased transmission bandwidth requirements. Demodulation is carried out by first converting PIWM signals into PIM signals followed by a standard PIM demodulation technique.

21

#### 2.3.2.5 Pulse frequency modulation

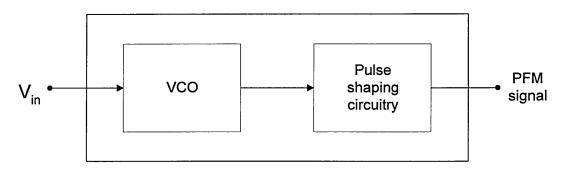

In pulse frequency modulation, the repetition rate of a pulse train of fixed pulse width changes according to the amplitude of the modulating signal. PFM waveforms can be generated by employing a voltage controlled oscillator (VCO) followed by pulse generating circuitry.

The PFM spectrum for a pulse train with pulse width  $\tau$ , repetition rate  $\omega_c$  and frequency deviation  $\Delta\omega$  when modulated with a sine wave of frequency  $\omega_m$  may be expressed as follows [Fitch, 1947]:

$$v(t) = \frac{A\omega_{c}\tau}{2\pi} \cdot \left\{ 1 + \frac{2\beta}{\omega_{c}\tau} \sin\left(\omega_{m}\frac{\tau}{2}\right) \cos\left(\omega_{m}t - \omega_{m}\frac{\tau}{2}\right) + 2\sum_{n=1}^{\infty} \sum_{k=-\infty}^{\infty} J_{k}(n\beta) \frac{\sin\left[\left(n\omega_{c} + k\omega_{m}\right)\frac{\tau}{2}\right]}{n\omega_{c}\frac{\tau}{2}} \cos\left[\left(n\omega_{c} + k\omega_{m}\right)t - k\omega_{m}\frac{\tau}{2}\right] \right\}$$

(2.6)

where  $\beta = (\Delta \omega/\omega_m)$  and A are modulation index and pulse amplitude, respectively. It can be seen that the unmodulated pulse carrier consists of the fundamental carrier frequency and its harmonics with amplitudes which follow a 'sinc = sin(x)/x' envelope determined by the pulse width  $\tau$ . Under modulation conditions, the spectrum contains the original baseband component (second term) as well as side tones around the carrier frequency (last term) and all its harmonics. The sinc function causes a slight asymmetry with the upper side tones being stronger than the lower. Due to the presence of baseband components, PFM signals can be demodulated after threshold detection and pulse regeneration by low-pass filtering.

#### 2.3.2.6 Square wave frequency modulation

Square wave frequency modulation is closely related to PFM and analogue frequency modulation. In SWFM a square wave is used as carrier in a similar manner to a sine wave in normal FM. The modulation spectrum may be expressed as [Chao, 1990]:

$$v(t) = AD \sum_{n=-\infty}^{\infty} \operatorname{sinc}(n\pi D) \sum_{k=-\infty}^{\infty} J_k(n\beta) e^{[j(n\omega_e + k\omega_m)t]}$$

(2.7)

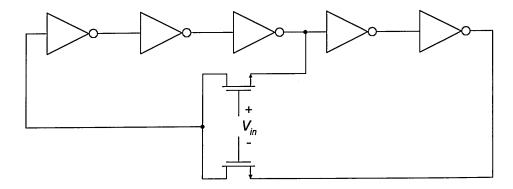

where *D* is the duty cycle. The modulation spectrum is similar to FM with a pattern of side tones around the carrier fundamental and all its odd harmonics. If the carrier waveform has a precise 50% duty cycle, no baseband component is present. Deviations from this duty cycle will cause a baseband component to be present as well as sidebands at even harmonics of the carrier frequency. The SWFM waveform may be generated by employing a voltage controlled multivibrator.

Demodulation can be achieved by converting the SWFM waveform into a PFM waveform followed by low-pass filtering. If double edge detection is employed (i.e. rising and falling edges) the resulting spectrum contains along with the baseband component sideband structures around all the even harmonics of the carrier frequency. The carrier frequency itself and all odd harmonics are not present. This allows the minimum carrier frequency to be lowered reducing the bandwidth requirements. In addition, detecting the rising and falling edges results in superior SNR performance compared to standard PFM [Heatley, 1985].

# 2.4 Comparison of PTM Schemes

A comparison of PTM techniques may be carried out with regard to distortion and SNR performance. Furthermore, for analogue signals the techniques may be evaluated by their ability to produce low distortion at low sampling ratios and high SNRs. The minimum carrier frequency can be estimated from spectral overlap between modulating signal and lower side tones of the carrier fundamental. Another consideration when evaluating different modulating techniques may be the modulator/demodulator circuit complexity influencing the overall transmission systems' cost [Wilson *et al.*, 1995].

Several PTM techniques have been implemented and they all result in different system complexity, bandwidth requirements and SNR performance. A trade-off has to be made for conflicting requirements leading to an optimised system. Some video transmission systems employing PIM or PIWM were reported in the late 1970s [Ueno et al., 1978; Sato et al., 1979; Okazaki, 1979]. But these two modulation techniques have not received much attention since they showed no performance advantages compared to PPM and required more circuit complexity compared to PFM and SWFM [Senior et al., 1995]. For this reason, only PWM, PPM, PFM and SWFM will be considered further.

The performance of modulation schemes may be compared with respect to a certain application. The application will give the minimum requirements, such as SNR or NLD, the system has to fulfil for a successful recovery of the transmitted signal.

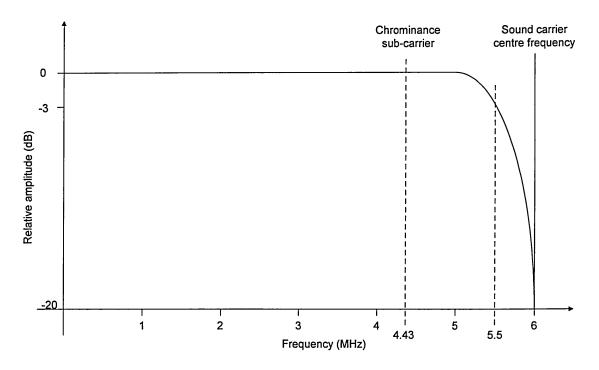

The circuit to be designed must be capable of modulating a standard PAL video signal. Figure 2.9 shows the frequency components of the standard United Kingdom TV signal which has a total bandwidth of 6.05 MHz [DTI, 1984].

Figure 2.9: Video signal spectrum

Important frequency components are the chrominance or colour sub-carrier and the sound carrier centre frequencies. The frequency deviation of the sound carrier under modulation condition is 50 kHz. From here on the video signal will be represented by a 5.5 MHz sine wave indicating its highest frequency component and the audio carrier signal by a 6 MHz sine wave. This avoids the impossible task of carrying out a spectral analysis of the transmitted signal for a complicated multi-tone modulating signal.

Important criteria are the SNR performance and the overall linearity of the system. It has been shown that transmission systems achieving an unweighted SNR of at least 40 dB with a non-linearity of less than 1% (-40 dB) are sufficient for video and TV signals [Sato *et al.*, 1985; Gutierrez-Martinez, 1991; Ghassemlooy *et al.*, 1993].

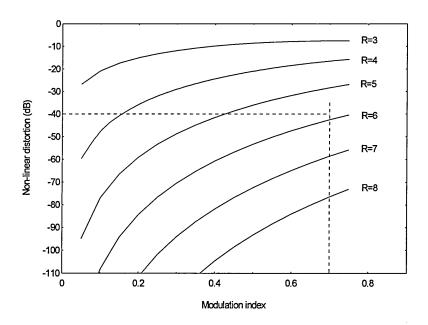

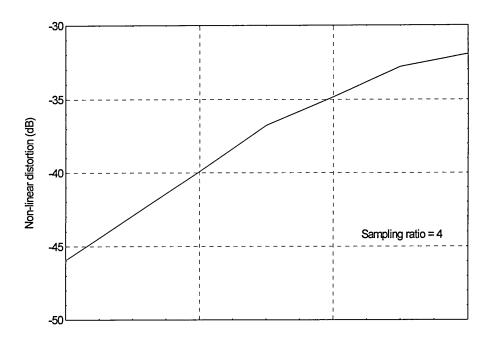

#### 2.4.1 Non-linear distortion

All PTM techniques produce a modulation spectrum with some common features. One of those features are the side tones around a modulated carrier frequency. Depending upon the ratio between carrier and modulating signal frequencies (sampling ratio), some of the lower carrier side tones will enter the baseband region causing non-linear distortion. These distortion levels can be estimated from the spectral profile. For PWM and narrow pulse PPM, the non-linear distortion level represents the ratio between side tone and recovered modulating signal amplitude and can be expressed as [Wilson *et al.*, 1995]:

$$NLD_{PWM/PPM} = 20\log\frac{2J_k(\pi M)}{\pi M}$$

(2.8)

Figure 2.10: Distortion level of PWM and PPM

Figure 2.10 shows a the graphical representation of equation (2.8). A distortion level of -40 dB can be achieved at a sampling ratio of 4 and a modulation index of 0.16, increasing to 6 for a modulation index of 0.7.

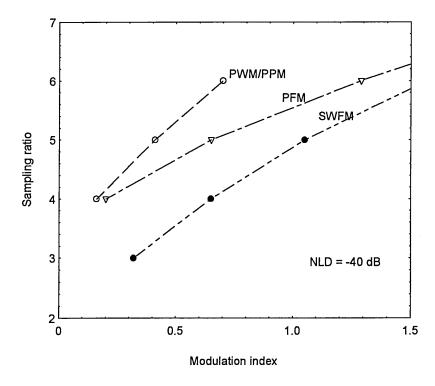

A similar analysis for PFM and SWFM results in:

$$NLD_{PFM} = 20\log \frac{2J_{k}(M)\sin[\pi(f_{c} + kf_{m})\tau]}{\pi f_{m}M\tau}$$

(2.9)

$$NLD_{SWFM} = 20\log \frac{J_k(2M)\sin[\pi(2f_c + kf_m)\tau]}{\pi f_m M\tau}$$

(2.10)

where  $f_m$  is the modulating frequency,  $f_c$  the carrier frequency and  $\tau$  the pulse width. Figure 2.11 shows a comparison of equations (2.8) to (2.10). Each curve represents a non-linear distortion level of -40 dB and can be used to define modulation index and sampling ratio for the various modulation schemes. The best performance is clearly obtained using SWFM followed by PFM. Furthermore, it can be seen that PWM/PPM require a higher sampling ratio than SWFM or PFM resulting in higher bandwidth requirements.

Figure 2.11: Sampling ratio versus modulation index for -40 dB distortion level

# 2.4.2 Signal-to-noise ratio performance

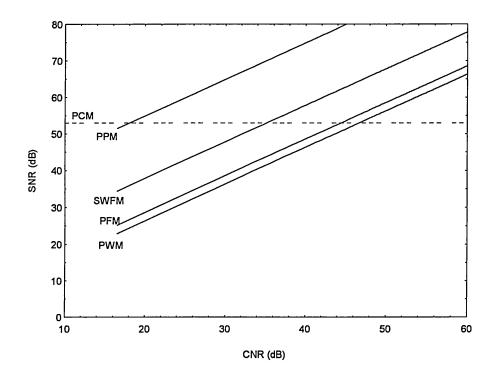

In addition to the non-linear distortion arising from spectral overlap the relationship between the output SNR and carrier-to-noise ratio (CNR) needs to be investigated. This relationship describes the interaction between SNR performance and the received pulse edge speed, as dictated by the channel bandwidth  $B_t = 1/\tau$ . An unweighted improvement factor *IF*, given by SNR minus CNR (in dBs), above threshold is proportional to the square of the ratio of transmission channel bandwidth to carrier frequency. The proportionality constant differs for each PTM technique [Chao, 1990; Wilson *et al.*, 1995] and can be expressed as follows:

$$PWM IF = \frac{\pi^2}{8} \left( \frac{MB_t}{f_s} \right)^2 (2.11)$$

$$PPM IF = \frac{\pi^2}{4} \left(\frac{MB_t}{f_c}\right)^2 (2.12)$$

$$PFM IF = \frac{3}{4} \left(\frac{MB_t}{f_c}\right)^2 (2.13)$$

$$SWFM IF = \frac{3}{2} \left(\frac{MB_t}{f_c}\right)^2 (2.14)$$

The minimum carrier frequency and bandwidth requirements for each modulation scheme is given in Table 2.2 with  $f_m = 6$  MHz, M = 0.7 and  $\tau = 7$  ns ( $f_g$  is the guardband) [Chao, 1990]. Except for PPM, all of the other schemes have a fairly similar bandwidth requirement and SWFM has the lowest carrier frequency due to a surpressed carrier fundamental.

Table 2.2: Bandwidth requirements for PTM schemes

| PTM scheme | Channel bandwidth $(B_t)$ (MHZ) | Carrier frequency (f <sub>c</sub> ) (MHz) |

|------------|---------------------------------|-------------------------------------------|

| PWM        | $f_m \pi M + 3f_m + 2f_g = 39$  | 21                                        |

| PPM        | $1/\tau = 143$                  | 21                                        |

| PFM        | $3f_m + 2Mf_m + 2f_g = 38$      | 20                                        |

| SWFM       | $2f_m + 2Mf_m + 2f_g = 32$      | 14                                        |

Figure 2.12 shows the output SNR versus CNR for different PTM schemes applying equations (2.11) to (2.14) with values taken from Table 2.2. This is a valuable comparison since it takes into account the different sampling ratios and bandwidth requirements of each technique. Different values for pulse width or modulating frequency will result in slightly different curves.

Figure 2.12: SNR versus CNR for various PTM schemes

It is clear that PCM offers improved SNR at lower CNRs than PTM. Above threshold detection, the SNR stays constant regardless of change in CNR values at the receiver [Chao, 1990]. But this is achieved at the expense of wider system bandwidth required for transmission. Another drawback is the increased circuit complexity requiring analogue to digital conversion at the modulator side and digital to analogue conversion at the demodulator side.

PPM has the best SNR performance of the PTM techniques considered but at the expense of wider transmission bandwidth and increased circuit complexity due to clock recovery at the demodulator. SWFM and PFM both offer good SNR performance, slightly better then PWM, while maintaining low sampling ratios and low cost.

These considerations make PFM and SWFM the preferred choice for transmitting TV signals through optical fibre cable. If a laser diode is used as an optical coupling device, PFM should be preferred due to its high peak and low average optical power ensuring a longer lifetime of the device.

# 2.5 Theoretical Aspects of PFM

#### 2.5.1 PFM frequency spectrum and spectral overlap

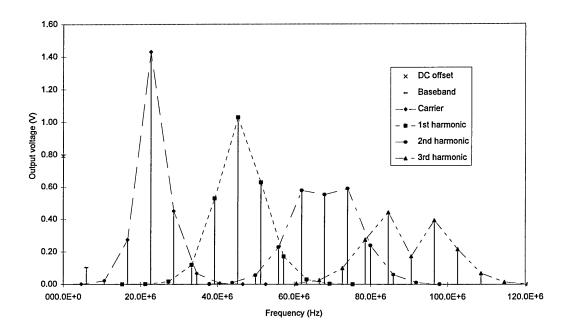

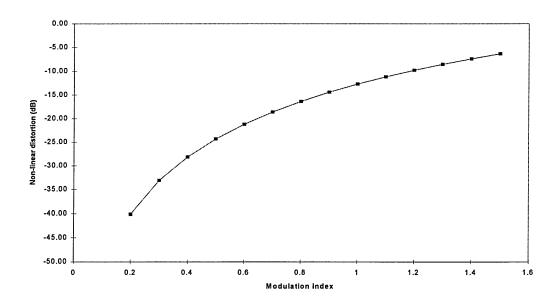

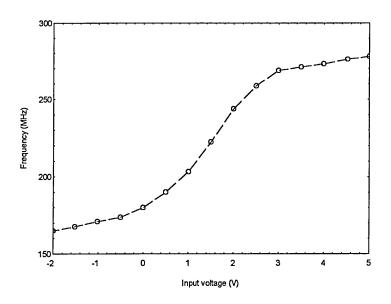

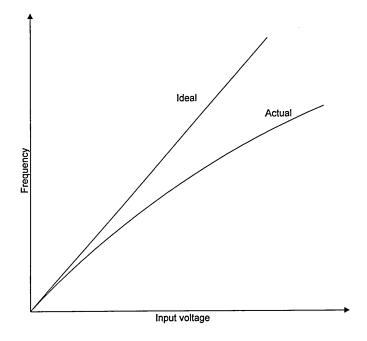

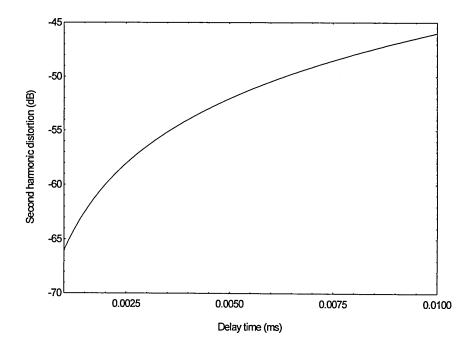

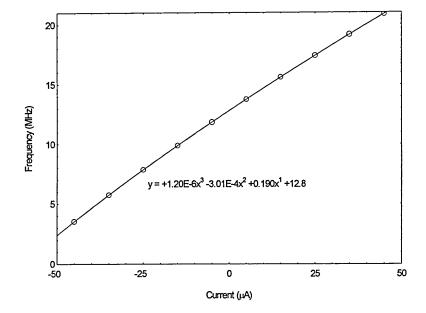

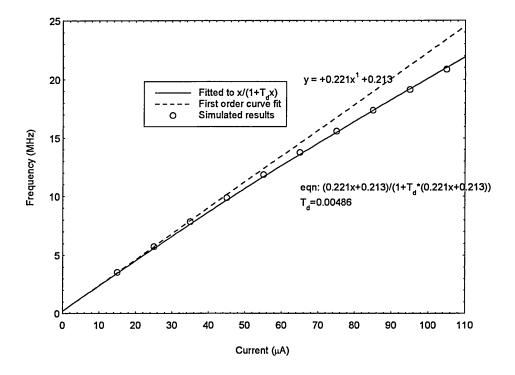

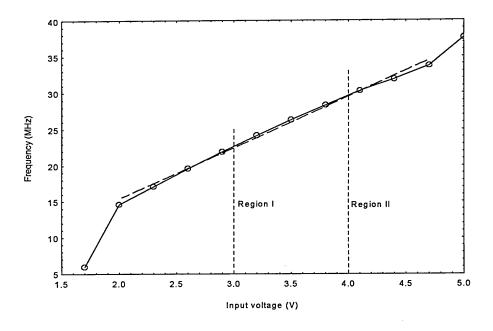

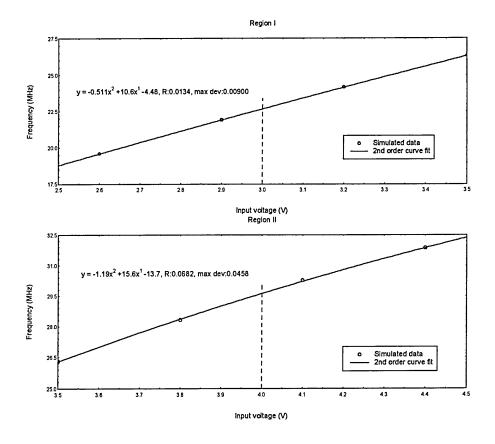

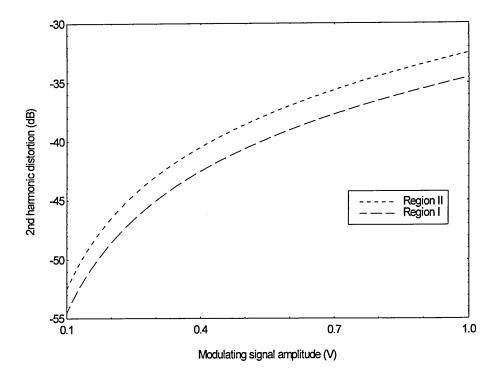

In pulse frequency modulation the repetition frequency of a train of pulses is determined by the modulating signal voltage. The spectrum of a PFM pulse train when modulated with a sine wave has been given in equation (2.6). Figure 2.13 shows a typical frequency spectrum derived from this equation and it can be clearly seen that the lower side tones of the carrier frequency especially distort the baseband component. The level of non-linear distortion will depend on the modulation index and sampling ratio. Figure 2.14 shows calculated distortion levels for a sine wave of 6 MHz and a carrier frequency of 22 MHz. The graph indicates that a smaller modulation index results in lower non-linear distortion levels.

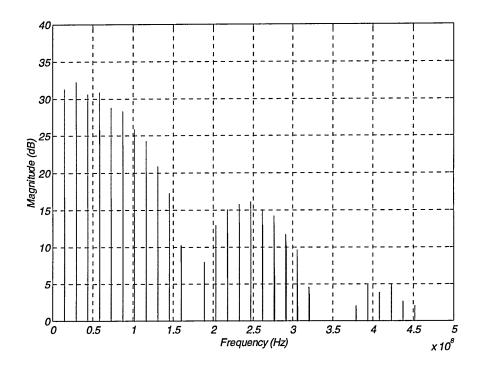

Figure 2.13: PFM frequency spectrum

Figure 2.14: Non-linear distortion due to spectral overlap versus modulation index

#### 2.5.2 Modulation and demodulation of PFM

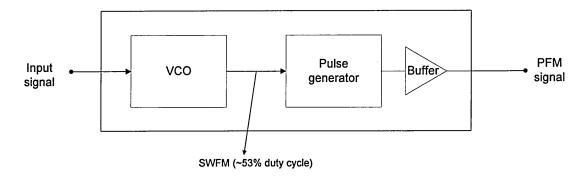

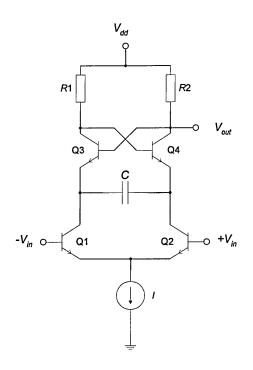

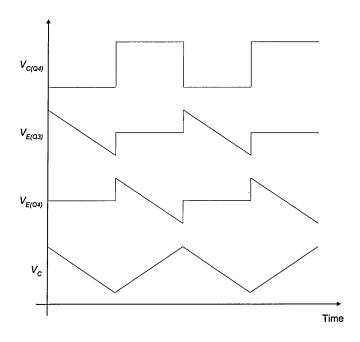

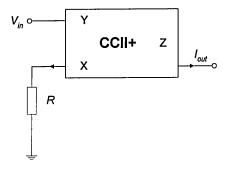

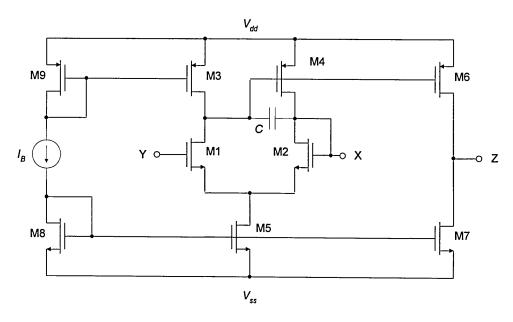

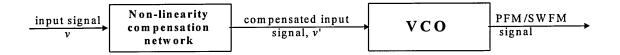

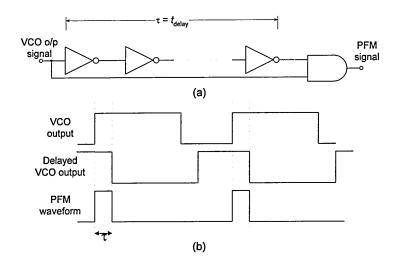

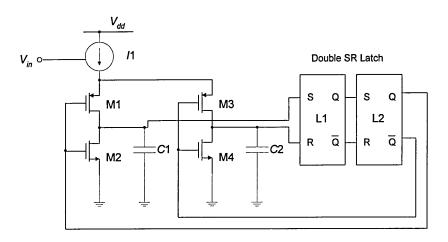

PFM can be generated by employing a voltage controlled oscillator followed by pulse generating circuitry (Figure 2.15). If a VCO with sinusoidal output is used, threshold detection may be employed to change the output waveform into a square wave. If a 50% duty cycle can be achieved, this waveform would represent a SWFM signal. PFM is generated from the VCO output signal by using the pulse generating circuitry which detects rising, falling or both edges and generates a pulse of fixed width.

Figure 2.15: PFM modulator circuit

Since the PFM spectrum contains a baseband component, it can simply be demodulated using a low-pass filter. However, there is an alternative demodulation technique based on regeneration schemes where the received PFM pulse train is passed through a threshold detector, a constant width pulse generator and low pass filter.

By using the second method a greater SNR performance can be achieved as may be expected since the original transmitted signal is reconstructed before demodulation. The first scheme, on the other hand, provides a very simple and cost effective means of demodulation since only a low-pass filter is needed.

#### 2.6 Summary

The development of optical fibre has renewed an interest in pulse time modulation techniques in the late 1970s and early 1980s. Since then, different modulation techniques have been investigated and some optical fibre communication systems are now being offered commercially [Optilas, 1995].

This chapter has reviewed the different PTM techniques and has given reasons why PFM is particularly favoured for the transmission of video signals through optical fibre [Heatley et al., 1984; Heker et al., 1988; Li et al., 1992]. PFM has a lower SNR performance than PPM but it makes more efficient use of the available channel bandwidth. Demodulation is less complex than PPM requiring no clock regeneration.

Most PFM modulators consist of a VCO generating SWFM followed by some form of pulse generating circuitry. Thus several ICs are usually necessary to build up a PFM modulator. This thesis describes an investigation carried out to combine all the elements of a pulse frequency modulator on one chip thus making it easier to design PFM systems. The key advantages identified are reduced cost due to easier implementation and increased reliability due to fewer components needed to assemble such a system. Further advantages are greater system miniaturisation and better protection against reverse engineering.

# CHAPTER 3 INTEGRATED CIRCUIT DESIGN

# 3 INTEGRATED CIRCUIT DESIGN

# 3.1 IC Design Overview

The history of integrated circuits so far has been very short but has been characterised by ever increasing performance and decreasing minimum dimensions. Since the first IC was produced by Kilby at Texas Instruments in 1958 [Kilby, 1976], the number of transistors per chip has increased dramatically to over 5 million in the latest processor chips. A procedure that more closely resembles today's ICs was reported by Robert Noyce of Fairchild at the beginning of 1959. Both scientists laid the foundation for what has become to be known VLSI design [Geiger et al., 1990].

Silicon has replaced Germanium as the most widely used semiconductor material and, nowadays, other materials such as Gallium-Arsenide are used for special applications. Advances in technology such as improved materials or photolithography have made it possible to increase the number of functions implemented on one IC. These improvements have been matched by engineers, developing circuits which were not realisable on breadboards and having a much higher functionality. With the continuing increase in computing power, advanced computer aided design tools (CAD) have been evolved further speeding up the design cycle.

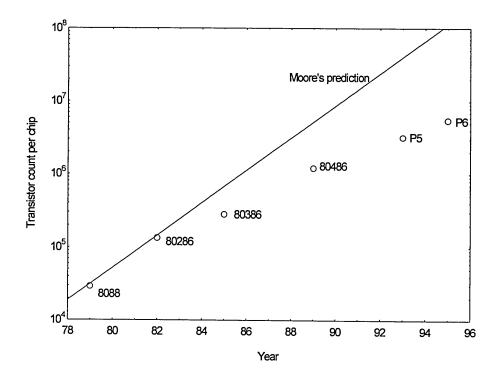

It was predicted by Moore, an electronics engineer, that the number of transistors per chip would grow exponentially [Moore, 1979]. This statement, which has come to be known as Moore's law, predicted the industrial trend towards higher integration remarkably well until the middle eighties. After this, due to the increasing complexity

and difficulties in testing of very large circuits, the transistor count per chip has not reached predicted values. However, the latest generation of microprocessor chips now contain more than 5 million transistors (Figure 3.1) [http1, 1996].

Figure 3.1: Transistor count per chip for the Intel x86 series

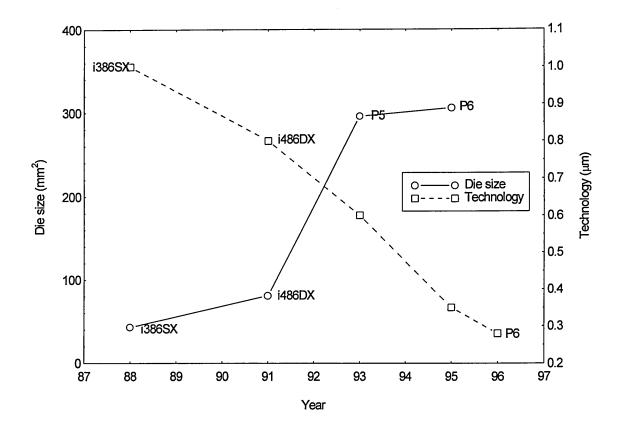

Although the individual feature size of transistors has been reduced significantly (with dimensions down to  $0.28~\mu m$  in modern processes) the phenomenal increase in transistor count has resulted in an increase of die area per chip (Figure 3.2) [http2, 1996].

The capital cost required to produce these state of the art integrated circuits has also grown due to the much more sophisticated photolithographic equipment needed to create the designs and due to increased clean room costs to improve the yield of large wafers.

Figure 3.2: Technology advances for the Intel x86 series

# 3.2 Silicon Integrated Circuit Technologies

#### 3.2.1 Technology overview

With silicon as semiconductor material, three different technologies can be categorised:

- 1. Bipolar

- 2. Complementary metal oxide semiconductor (CMOS)

- 3. BiCMOS (combination of the two above)

Table 3.1 lists general features of those three technologies. The choice of technology will depend on several issues related to the purpose of the product such as frequency range, operating speed, power consumption and cost.

Table 3.1: Advantages of silicon technologies

| Bipolar         | CMOS                 | BiCMOS                   |

|-----------------|----------------------|--------------------------|

| Greater current | Smaller area         | Combines advantages of   |

| drive per unit  | Higher yield         | both worlds              |

| area            | Lower parasitic      | Superior system-level    |

| Better matching | capacitances         | performances             |

| Superior linear | Lower power          | innovative structures    |

| performance     | consumption          | (npn-PMOS merging        |

| Low sensitivity | Near ideal switching | smart power applications |

| to process      | device               |                          |

| variations      | Bi-directional       | But 40% Cost Increase    |

|                 | • inherent memory    |                          |

|                 | capability           |                          |

In general, the use of bipolar technology will result in higher speed and drive capabilities and better transconductance compared to CMOS technology but this is at the expense of higher power consumption and higher sensitivity to supply voltage changes. An advantage of CMOS is that its higher density allows a higher functionality per chip area. For analogue applications, bipolar offers a high gain per stage, higher bandwidth and output swing, better linearity and the implementation of precision passive components. Some of the disadvantages of CMOS for analogue purposes can be overcome by ingenious circuit designs such as cascading stages to increase the gain of amplifiers. Advantages of CMOS include a higher input impedance than bipolar and a near ideal switching characteristic making it well suited for digital designs. It also

provides a logic swing approaching the value of the supply voltage and has a superior noise voltage margin. However, bipolar devices can achieve a higher maximum switching speed [Hurst, 1992]. The difference in switching speed will reduce with the introduction of smaller geometry sizes since the speed of a CMOS transistor depends on the length of the channel, whereas the speed of a bipolar transistor depends on the width (thickness) of the base-emitter junction [Laker *et al.*, 1994].

BiCMOS combines the advantages of purely bipolar and CMOS technologies. It offers the designer the advantages of both technologies such as low noise and high switching speed of bipolar devices while maintaining active CMOS power dissipation levels. For example, an op-amp with high input impedance, large gain and high drive capability could use MOSFETs as input devices and bipolar transistors in the output stage. In addition, innovative structures such as npn-PMOS merged devices can be built allowing novel circuit designs. The disadvantage of employing BiCMOS is the increased cost since up to 18 masks are required in processing [Hurst, 1992].

The relatively lower cost of CMOS designs compared to bipolar and BiCMOS makes this technology the preferred choice even if the analogue performance is not superior. But this disadvantage can often be compensated by innovative circuit techniques. Furthermore, mixed signal circuits can benefit from the advantages that CMOS can offer for the digital part of the designs.

#### 3.2.2 Theoretical aspects of bipolar and CMOS transistors

#### 3.2.2.1 Bipolar transistor

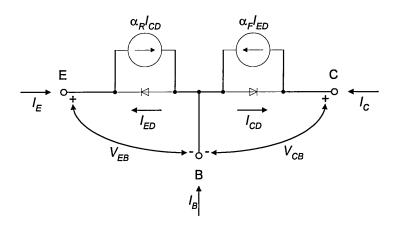

A bipolar transistor is based on two pn junctions which share a common semiconductor layer. The behaviour of the bipolar transistor can be described by the *Ebers-Moll* model. Figure 3.3 shows *Ebers-Moll* circuit model of a npn bipolar transistor [Millman *et al.*, 1987].

Figure 3.3: Ebers-Moll large signal representation of a npn transistor

The component  $\alpha_R I_{CD}$  is that fraction of  $I_{CD}$  that is coupled through the base to the emitter. Likewise,  $\alpha_F I_{ED}$  is the portion of  $I_{ED}$  coupled into the collector. The emitter  $(I_E)$  and collector  $(I_C)$  currents can now be determined from Figure 3.3 and represent the *Ebers-Moll equations* [Millman *et al.*, 1987]:

$$I_{E} = -I_{ES} \left( e^{-\frac{V_{EB}}{v_{T}}} - 1 \right) + \alpha_{R} I_{CS} \left( e^{-\frac{V_{CB}}{v_{T}}} - 1 \right)$$

$$\tag{3.1}$$

$$I_{c} = \alpha_{F} I_{ES} \left( e^{-\frac{V_{EB}}{v_{T}}} - 1 \right) - I_{CS} \left( e^{-\frac{V_{CB}}{v_{T}}} - 1 \right)$$

(3.2)

with  $v_T = kT/q$  where k is the Boltzmann constant, T is the temperature and q is the charge of an electron. The four components  $I_{ES}$ ,  $I_{CS}$ ,  $\alpha_F$  and  $\alpha_R$  are functions of doping density and transistor geometry. Realising that the sum of the terminal currents must be zero, the base current may be written as:

$$I_{\scriptscriptstyle B} = -(I_{\scriptscriptstyle E} + I_{\scriptscriptstyle C}) \tag{3.3}$$

#### 3.2.2.2 CMOS transistor

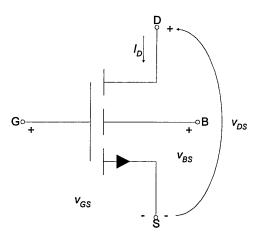

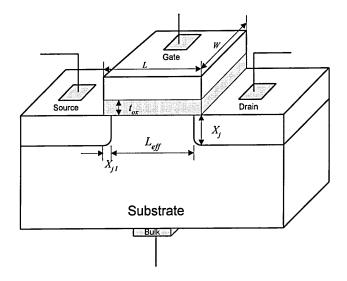

The metal oxide semiconductor field effect transistor (MOSFET) is the building block of the CMOS technology. Here, the conductivity of a channel is controlled by an electric field developed between an insulated 'gate' electrode and the conducting channel. The gate/oxide/channel combination forms a capacitance known as the gate capacitance. The voltage applied to the gate controls the conductivity of the channel. A current can flow through the channel provided a positive voltage is applied to one end of the channel and a negative to the other end.

Figure 3.4: Variable and sign convention for an n-type MOS transistor

Depending upon the value of  $v_{GS} - V_T$  ( $V_T$  is the threshold voltage of the transistor), various regions of operation of the MOS transistor can be determined.

Cut-off region  $(v_{GS} - V_T \le 0)$ :

$$I_{D}=0 ag{3.4}$$

Ohmic region  $(0 < v_{DS} \le v_{GS} - V_T)$ :

$$I_{D} = k \frac{W}{L} \left[ 2(v_{GS} - V_{T})v_{DS} - v^{2}_{DS} \right] (1 + \lambda v_{DS})$$

(3.5)

where W is the channel width, L the channel length,  $\lambda$  is the channel length modulation parameter and k the transconductance parameter. The transconductance parameter  $k = \mu_n C_{ox}/2$ , where  $\mu_n$  is the electron mobility and  $C_{ox}$  is the gate capacitance. Both parameters are process dependent.

Saturation region (0 <  $v_{GS}$  -  $V_T \le v_{DS}$ ):

$$I_{D} = k \frac{W}{L} (v_{GS} - V_{T})^{2} (1 + \lambda v_{DS})$$

(3.6)

#### 3.2.2.3 Comparison of bipolar and MOS transistor

By comparing the basic transistor equations for bipolar and CMOS devices some design principles can be concluded. The current flow through the bipolar device is controlled by a current whilst the current through a MOS transistor is controlled by a voltage. Furthermore, the characteristic of a MOS transistor is strongly dependent upon its geometry resulting in different circuit configurations for bipolar and CMOS technologies. In CMOS, for instance, the designer can change the performance of an operational amplifier by changing the transistor geometries. This is not easily achieved in bipolar [Sansen, 1994].

# 3.3 IC Design Methodologies

The increased functionality of ICs has made it necessary to develop design methodologies to simplify design problems and enable members of a design team to work together simultaneously. The design strategies can be divided into:

- 1. Bottom up design

- 2. Top down design

- 3. Combination of both

In the bottom up approach the designer starts at the bottom by specifying the technology and then developing the system from transistor or gate level. Using the second approach, the circuit is designed starting from a system level description derived from the specification. This approach is normally used in digital designs resulting in an increased productivity. The design is repeatedly split into groups of simpler substructures until the lowest level (simple gates) is reached. These may then be implemented in silicon using precompiled standard cells. This approach is also well suited for the application of hardware description languages (HDL). Efforts have been made to allow the use of the top down approach in analogue designs but the requirements for those circuits are too stringent and cannot, at present be met with this design methodology [Szepesi et al., 1994].

The third methodology combines the features of the previous two. It may be used in designs where analogue and digital parts are included. It enables the designer to decompose the design into functional blocks which are already fully understood. The

bottom up approach is then applied to implement those functional blocks in silicon [Schwarz, 1993].

# 3.4 Custom Integrated Circuit Design

The circuit requirements for every electronic product will be very specific and unique to that product. A designer would traditionally use standard electronic components and sub-assemblies to generate the product. Using custom integrated circuits (circuits made for a specific product and containing all the functionality of that product) gives several advantages, such as fewer components, a smaller physical size, better reliability due to fewer connections between components. For some applications the reduced power and performance enhancements may also be of importance.

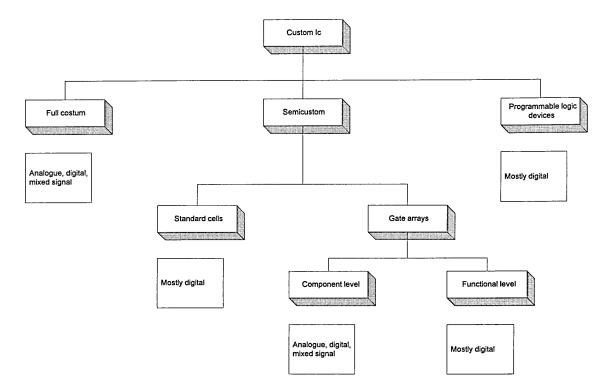

Different categories of custom ICs can be distinguished. In **full-custom** design the chip layout is developed and fully optimised for a particular application at mask level. **Standard cell** ICs rely on a precompiled library of standard circuit elements which can be automatically placed and wired by CAD tools. **Gate arrays** are prefabricated ICs with circuit elements already in place. Only the final interconnections between those cells have to be custom designed and made. The last two categories are also called semi-custom designs and mostly used for digital circuits [Davidse, 1994].

Full-custom designs are usually more expensive and time consuming than semi-custom designs and will only be economical for large volume production due to reduced silicon area. In semi-custom designs, gate arrays will be more cost efficient compared to

standard cells due to reduced cost involved for the mask layout but depending upon the production volume, the reduced die area for standard cell designs may make this approach more cost efficient.

Programmable logic devices (**PLDs**) are a special group of custom ICs. PLDs are able to realise any required logical function within the capacity of the device. Early PLDs were restricted to the implementation of Boolean functions which could be written in a sum-of-product form. Modern devices include flip-flops which may be used as memory elements. More recently field programmable gate arrays (**FPGAs**) have become widespread. These complex VLSI circuits consist of circuit cells and interconnecting segments which may be programmed to create any digital function required. They are ideally suited for the production of prototypes and also for cost effective chip design, especially for low volume applications [Kang *et al.*, 1996]. Currently PLDs and FPGAs are only generally available for digital custom ICs [Hurst, 1992].

Figure 3.5 shows the custom IC overview. It can be seen that the semi-custom ICs are mostly used for digital designs, although some research has gone in the application of transistor arrays for analogue applications [Declercq, 1994].

# 3.5 Computer Aided Design Tools

Increased computer performance has enabled significant advances in the computer aided design tools. The first IC designs were totally hand drawn using large drawing boards.

Figure 3.5: Custom integrated circuits overview

The mask layouts were again cut by hand using dimensionally stable plastic sheets.

This procedure was very costly and ineffective due to many errors occurring in the layout.

With increases in computing power, the designer has seen a corresponding increase in support from CAD tools which have improved substantially over the years. Earlier problems such as verification and validation of IC designs could be automated and simulation times could be decreased.

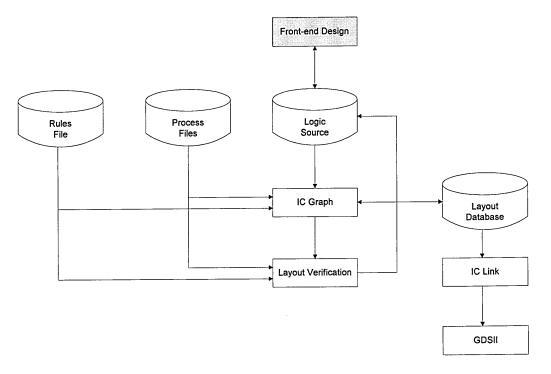

Nowadays, CAD systems are truly hierarchical and all design phases access a common database. Thus, the computer helps the designer in all aspects of design management

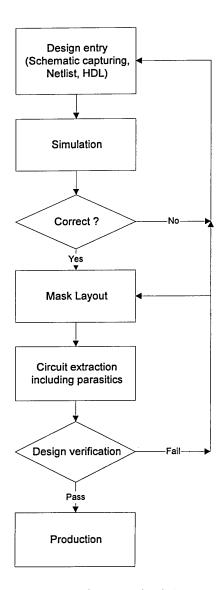

integrating standard design tools in a common framework. Figure 3.6 shows the general design methodology adopted using CAD tools in a common framework.

# 3.6 EUROPRACTICE IC Technologies

#### 3.6.1 EUROPRACTICE

The proposed IC has been fabricated through the EUROCHIP/EUROPRACTICE program. EUROCHIP was part of the ESPRIT VLSI DESIGN ACTION and provided its academic member institutions with a range of services including purchase and support of CAD software, access to chip fabrication, discounts on test equipment and training. The program terminated in September 1995 and was followed by EUROPRACTICE which aimed to stimulate wider exploitation of state-of-the-art technologies by European Industry. The IC Manufacturing Service (ICMS) coordinated by IMEC (Belgium), is the EUROPRACTICE service for low cost IC prototyping, volume and testing.

Taking into account cost and the considerations discussed in section 3.2, it was decided to investigate the usage of the Alcatel MIETEC 2.4  $\mu m$  CMOS process for this work. Although the usage of the MIETEC 0.7  $\mu m$  CMOS technology would have been more suitable the prototyping cost would have at least quadrupled. Also, the Mentor Graphics' analogue design kit was only made available in late 1995. General information about the MIETEC 2.4  $\mu m$  CMOS technology can be found in Appendix A.

Figure 3.6: Design methodology using standard CAD tools in a common framework

ICMS offers access to CMOS, BiCMOS and GaAs processes from different foundries including technologies ranging from 2.4 μm digital/analogue CMOS and 0.5 μm digital CMOS to 0.8 μm BiCMOS. An ASIC bipolar array for fast turn-around analogue circuits is also offered together with GaAs processes. An up-to-date list can be found on IMEC's WWW page [http3, 1996].

#### 3.6.2 Performance consideration for the MIETEC 2.4 $\mu$ m

#### technology

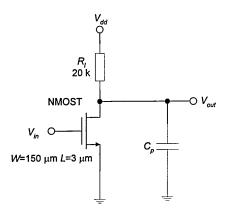

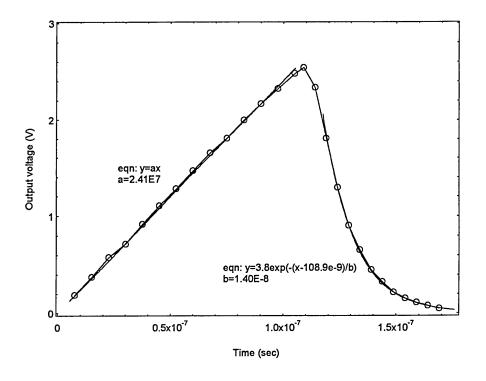

One of the prime criteria to satisfy is whether the chosen technology can deliver the speed required for modulating video signals. This requirement can be proven by analytical expression, simulation and practical measurement. This chapter presents results from analytical expressions and initial simulations; practical measurements are presented in Chapters 6 and 7.

#### Maximum frequency of operation

Laker and Sansen [1994] have shown that the maximum operating frequency  $f_{max}$  of a CMOS transistor may be written as:

$$f_{\text{max}} = \frac{1}{2\pi} \frac{\mu}{L_{\text{eff}}^{2}} (v_{GS} - V_{T})$$

(3.7)

where  $\mu$  is the channel mobility,  $L_{eff}$  is the effective channel length and  $v_{gs}$  and  $V_T$  are the gate-source and threshold voltage, respectively. The maximum frequency will be in the Gigahertz region for the chosen technology and should therefore be sufficiently high. But this is the maximum frequency of a single transistor where neither interconnections, parasitic elements nor subsequent stages are taken into account.

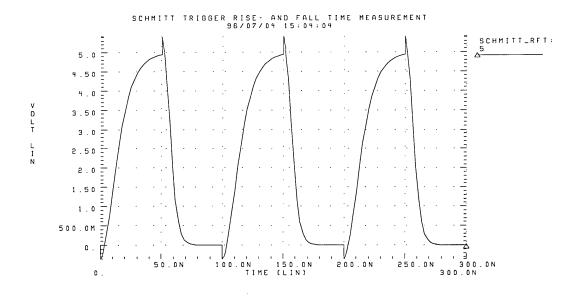

In order to prove the feasibility of this technology further, a digital circuit was simulated and its rise and fall times were measured. A Schmitt trigger was chosen as a test circuit [Filanovsky *et al.*, 1994]. With a capacitive load of 0.5 pF the rise and fall times were

24 ns and 11 ns, respectively, resulting in a possible operating frequency of 28 MHz which should be sufficient to meet the requirements as set in section 2.4 (Figure 3.7).

Figure 3.7: Simulated Schmitt trigger output waveform

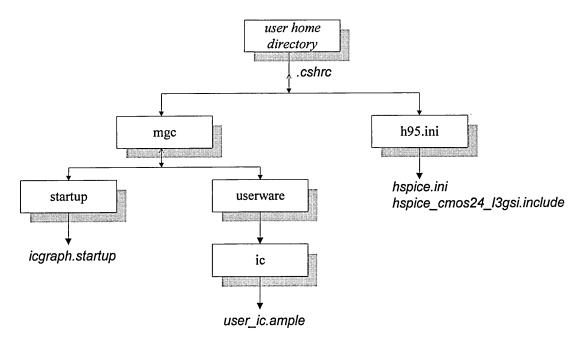

# 3.7 Design Environment

All the IC design work was carried on a HP712/60 workstation running Mentor Graphics (MG) version A1F and META HSPICE version 95. Although an analogue simulator (ACCUSIM) is included in the MG framework this was not used due to the fact that it was based on an earlier version of SPICE (2G6) and frequently showed convergence problems for even simple circuits. HSPICE has built-in routines which avoid the problems encountered with ACCUSIM. In addition, HSPICE netlists are easily generated from IC Station (the IC mask layout editor of MG).

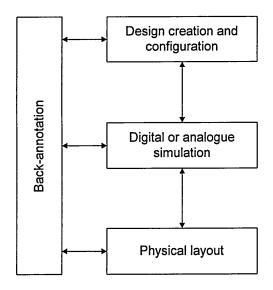

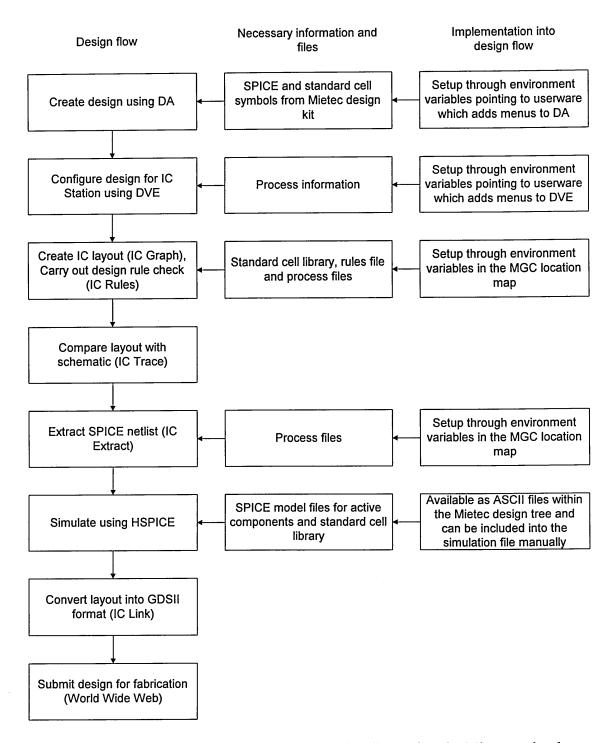

The design flow which has been adopted combines both the top down and bottom up approach. The PFM modulator is split into several functional blocks using the top down

method whereas each functional block is designed employing the bottom up method. Schematic capturing and mask layout is done using Design Architect (DA) and IC Station and simulations are carried out by generating a netlist and transferring it into HSPICE.

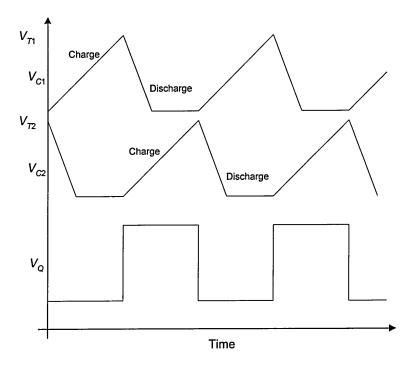

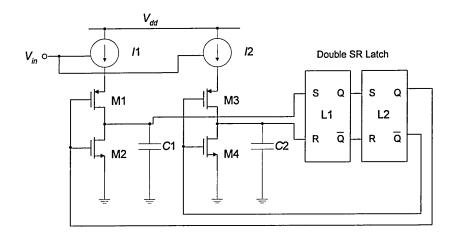

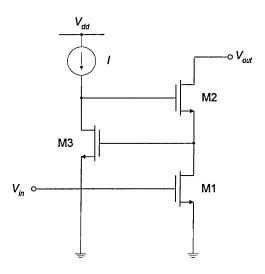

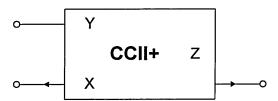

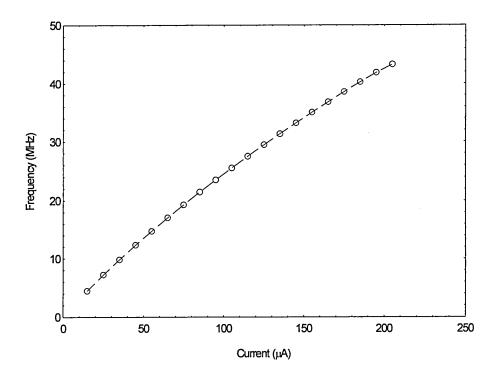

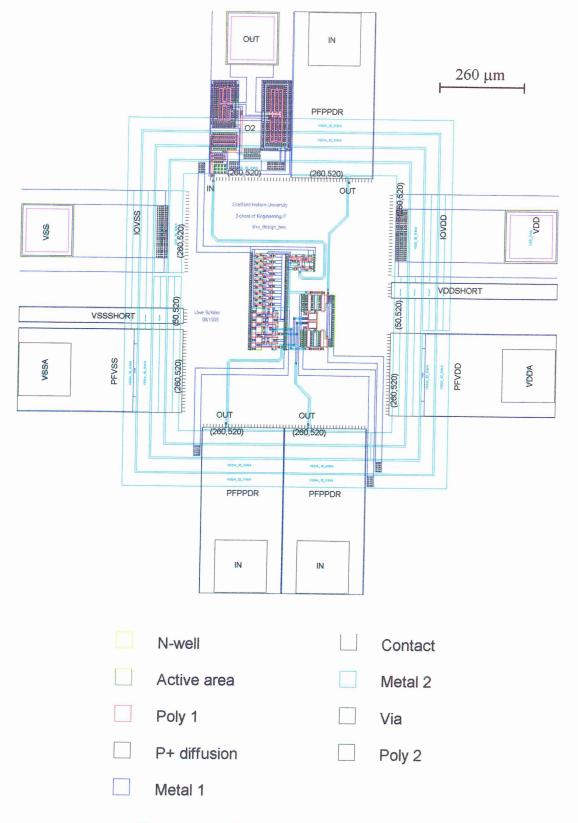

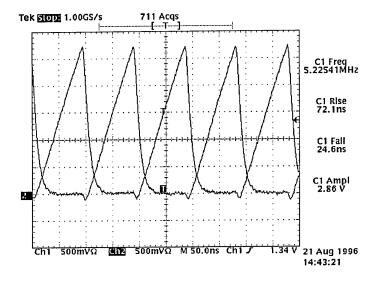

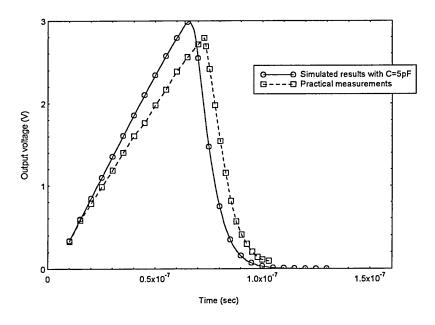

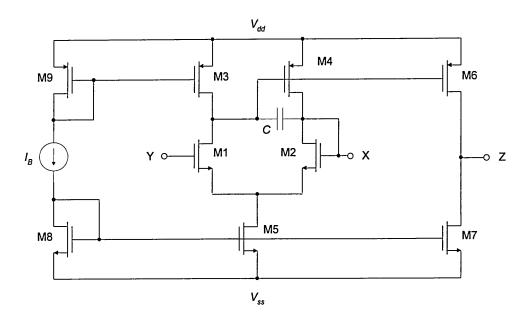

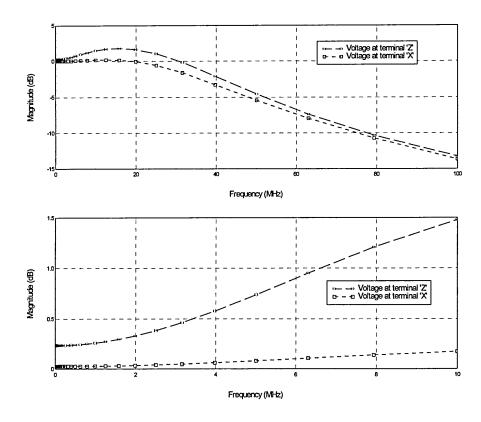

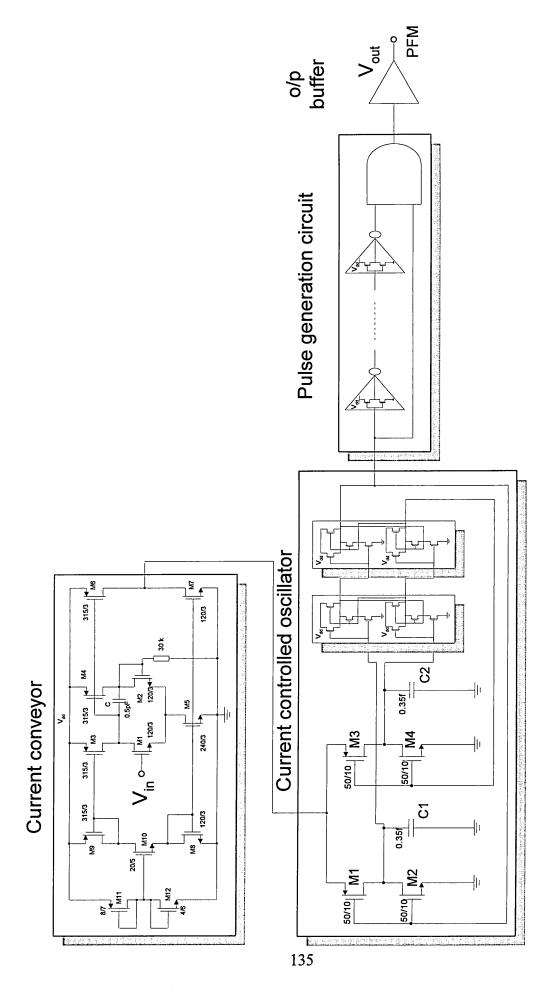

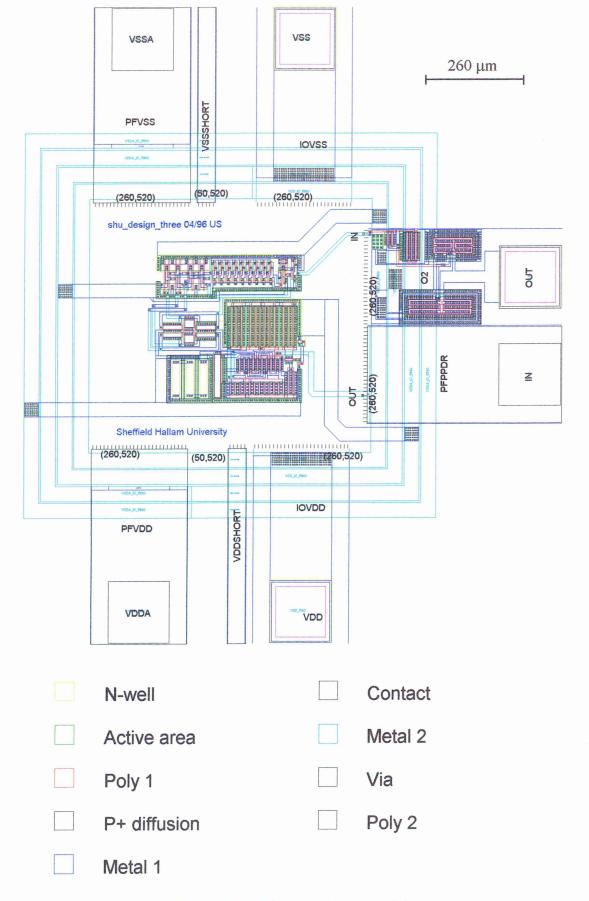

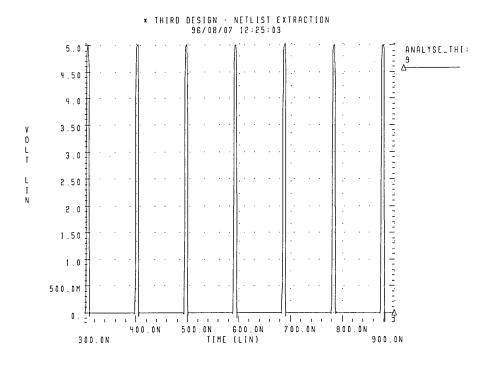

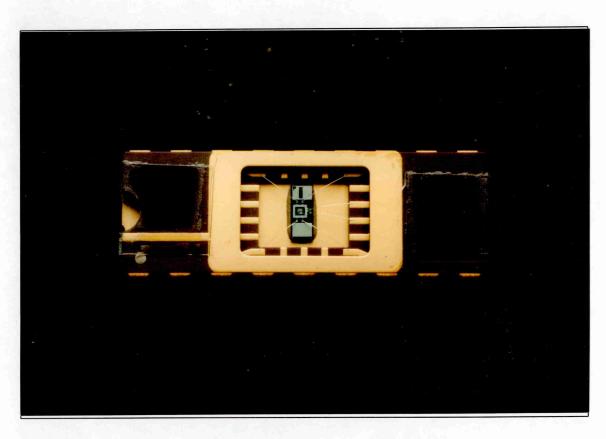

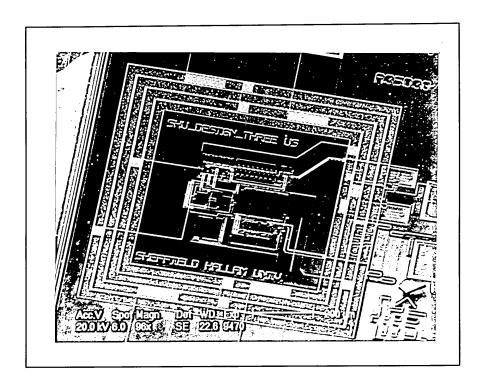

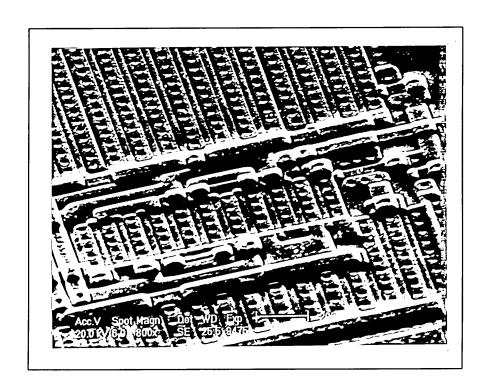

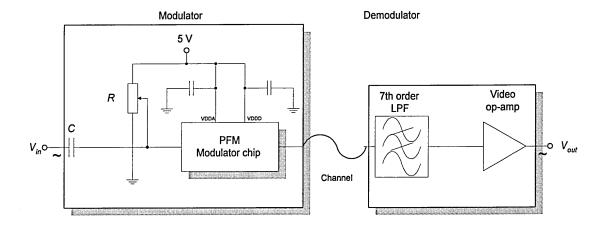

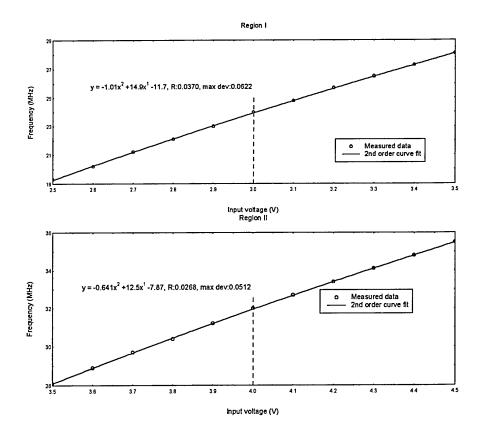

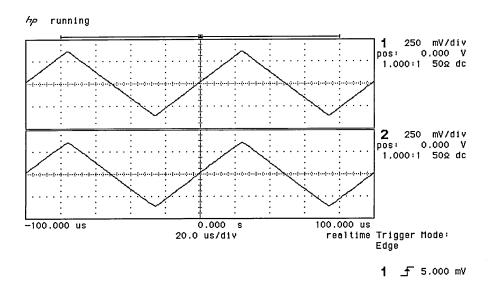

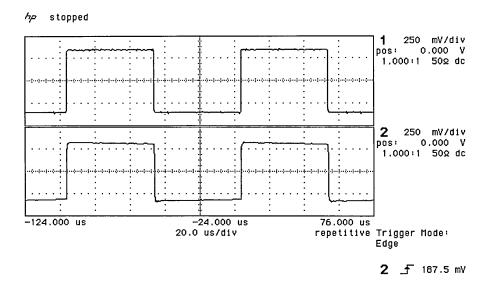

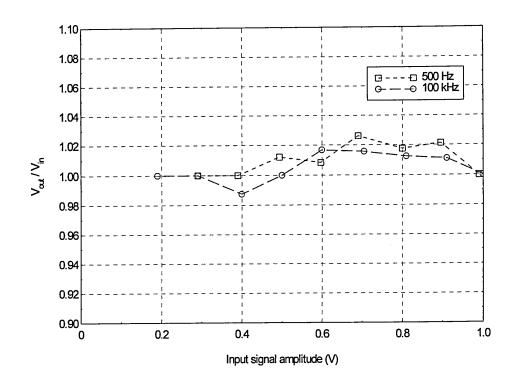

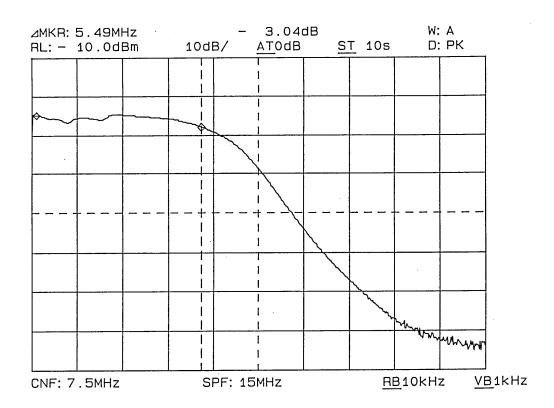

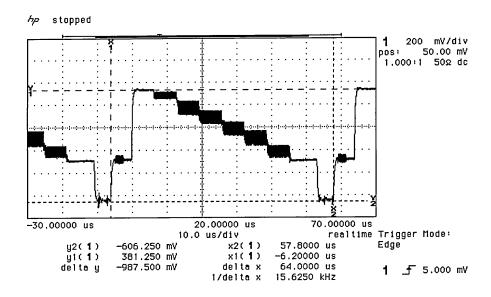

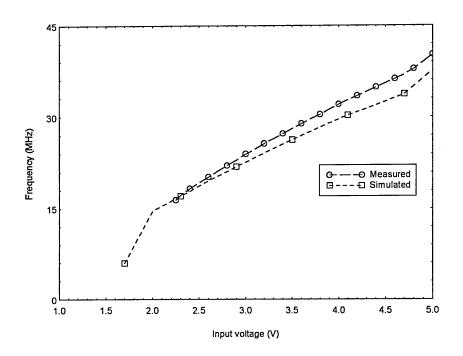

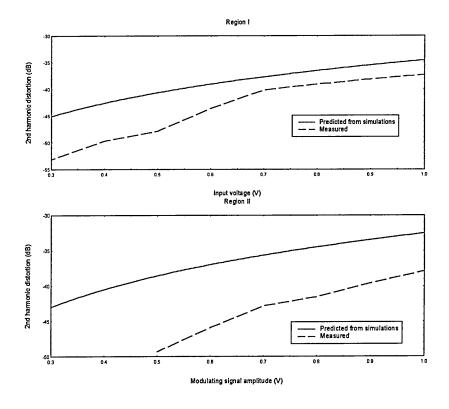

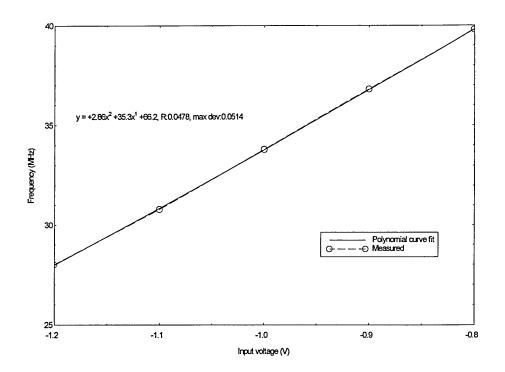

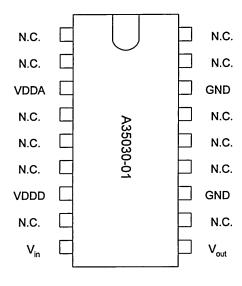

Figure 3.8: Adopted design flow