Parallel processing of frame-based networks.

SAEEDI, Mohammed H.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/20308/

# A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/20308/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

Sheffield Hallam University

Hallamshire Business Park Library

103 Replet Street

Steffield 511

273021

**Sheffield City Polytechnic Library**

REFERENCE ONLY

ProQuest Number: 10700954

## All rights reserved

## INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

## ProQuest 10700954

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

# Parallel Processing of Frame-Based Networks

by

## Mohammed Hashem Saeedi MSc

A thesis submitted in partial fulfilment of the requirements of the council for National Academic Awards for the degree of Doctor of Philosophy.

Sponsoring Establishment

School of Computing and

Management Sciences,

Sheffield Hallam University

April 1993

#### ABSTRACT

This Project involved the development of a simulation of a rectangular array of Processing Elements (PE's), with a dedicated frame based knowledge representation language. The main objective of the Project was to analyse and quantify the gain in speed of execution in a parallel environment, as compared with serial processing.

The computational model of the language consisted of two main components: the knowledge base, and the replicated/distributed inference engine. The knowledge base was assumed to represent real world knowledge, in that it consisted of a large volume of information, which was divided into domains and hierarchies.

When a query is made, appropriate portions of the knowledge base are mapped to the array of PEs on a one-to-one basis (one frame/PE), where each PE is capable of performing any relevant operations itself.

The execution of a query is based on the propagation of messages across the array of PEs, where each message is contained in a data packet. Each packet holds the query-frame, created by interacting with the user, together with other relevant information used for knowledge manipulation.

The main inference mechanism in the system is based on the parallel inheritance of properties, where each data packet carries inherited data from higher level to lower level frames, within the appropriate hierarchies. As each packet arrives at a PE which contains a relevant frame, a series of matching, and consequently, inheritance operations are performed.

An algorithm, superimposed at the highest level of the system, computes time delays in relation to the overall architecture of the machine. There are two main operations for which time penalties are calculated: frame-processing and communication. The frame processing involves matching and inheritance operations, and the communication operation involves message passing and data packet traversal.

During each execution cycle, the time penalties for both processing and communication are computed and stored in a file. These files are then used by a graphics package which transforms the numerical data into a set of graphs. These graphs are utilised in the analysis of the behaviour of the simulation. The analysis of the test-runs, and of their associated graphs, has yielded positive and encouraging results, demonstrating that there can be an average of a 35 fold gain in the speed of execution.

## **ACKNOWLEDGEMENTS**

This project was financed by ALVEY/SERC research grant GR/D 40081 - IKBS/ARCH/068/131 with ICL plc as an "industrial uncle".

I would like to thank my first and second supervisors: John Brown and Ian Morrey, for all their help and advice. I would also like to thank my dear wife who has been a great support throughout the lifetime of this project.

# TABLE OF CONTENTS

| 1.0 .CHAPTER ONE: INTRODUCTION                              |          |

|-------------------------------------------------------------|----------|

| 1.1INTRODUCTION                                             | 1        |

| 1.2PROJECT OBJECTIVES                                       | 8        |

|                                                             |          |

| 2.1 CHAPTER TWO: THE KNOWLEDGE REPRESENTATION PARADIGM      |          |

| 2.1INTRODUCTION                                             | 10       |

| 2.2SEMANTIC NETWORKS                                        | 11       |

| 2.3 .FRAMES                                                 | 14       |

| 2.31FRAME-BASED INFERENCE                                   | 17       |

| 2.4 .KNOWLEDGE REPRESENTATION LANGUAGES                     | 17       |

| 2.41KL-ONE                                                  |          |

| 2.411INHERITANCE IN KL-ONE                                  | 20       |

| 2.412 PROCEDURAL ATTACHMENT IN KL-ONE                       | 2.1      |

| 2.42KEE .22                                                 |          |

| 2.421GENERAL FORMAT OF UNITS IN KEE                         | 23       |

| 2.422 INHERITANCE IN KEE                                    | 24       |

| 2.423PROCEDURAL ATTACHMENT IN KEE                           | 26       |

| 2.5 PRODUCTION SYSTEMS                                      |          |

| 2.51DATABASE IN PRODUCTION SYSTEMS                          | 20<br>28 |

| 2.52RULES                                                   |          |

| 2.53INFERENCE ENGINE                                        | ∠c       |

| 2.53MATCHING RULES AGAINST DATA                             | 27<br>20 |

| 2.532UNCERTAINTIES                                          |          |

| 2.533CONFLICT RESOLUTION                                    |          |

| 2.54PRODUCTION SYSTEMS CHARACTERISTICS                      | 2 1      |

| 2.54PRODUCTION 5151EWS CHARACTERISTICS                      | 52       |

| 2.55THE EFFICIENCY OF PRODUCTION SYSTEMS                    |          |

| 2.56THE RETE ALGORITHM                                      |          |

| 2.57BLACKBOARD DATA STRUCTURE                               |          |

| 2.6CONCLUDING REMARKS                                       | 33       |

| 2.0 OHADED THEE DADALLE ADOMESTICE FOR AL                   |          |

| 3.0 CHAPTER THREE: PARALLEL ARCHITECTURES FOR AI            | 2.0      |

| 3.1INTRODUCTION                                             | 38       |

| 3.2TAXONOMY OF PARALLEL ARCHITECTURE MACHINES               |          |

| 3.3KNOWLEDGE BASED MACHINES                                 | 42       |

| 3.4ASSOCIATIVE NETWORKS MODELS                              | 42       |

| 3.41A BRIEF DISCUSSION ON NEURAL NETS                       | 43       |

| 3.42 THE NETL SYSTEM                                        | 46       |

| 3.421THE PARALLEL NETWORK SYSTEM                            |          |

| 3.422 CREATING DESCRIPTIONS                                 | 48       |

| 3.423INHERITANCE AND MARKER BIT PROPAGATION                 | 49       |

| 3.43 THE CONNECTION MACHINE                                 | 51       |

| 3.44 THE BOLTZMANN MACHINES                                 | 52       |

| 3.45 SNAP                                                   | 53       |

| 3.5RULE-BASED MODELS                                        | 54       |

| 3.51DADO Machine                                            | 55       |

| 3.52 NO-VAN MACHINE                                         | 55       |

| 3.6THE SHEFFIELD MACHINE                                    | 56       |

| 3.61 FINAL REVIEW OF THE SM'S PARALLEL ARCHITECTURE         | 60       |

| 3.62 COMPARISON WITH THE EXISTING PARALLEL MACHINES         | 61       |

|                                                             |          |

| 4.0 CHAPTER FOUR: KNOWLEDGE REPRESENTATION AND ITS MANIPULA | ATION    |

| IN THE SHEFFIELD MACHINE                                    |          |

| 4.1INTRODUCTION                                             | 68       |

| 4.2THE KNOWLEDGE BASE                                       | 68       |

| 4.3SIZE ESTIMATION OF A FRAME-BASED NETWORK                 | 71       |

| 4.4FRAMES STRUCTURE AND THEIR RELATIONSHIPS                 | 73       |

| 4.5 CONTROL MECHANISM and KNOWLEDGE MANIPULATION            |          |

| 4.6INFERENCE IN THE SM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 4.61 PARALLEL PROPAGATION OF MESSAGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 79                                                                                                   |

| 4.62PARALLEL INHERITANCE OF PROPERTIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                      |

| 4.7OUERIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87                                                                                                   |

| 4.71DIFFERENT QUERY LANGUAGES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88                                                                                                   |

| 4.72 OUERIES IN THE SM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 94                                                                                                   |

| 4.72 QUERIES IN THE SM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 95                                                                                                   |

| 4.73THE RELATIONAL DATA MODEL V THE SM'S FRAME-BASED MODEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                      |

| 5.0 CHAPTER FIVE : THE SHEFFIELD MACHINE SIMULATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                      |

| 5.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105                                                                                                  |

| 5.2OVERALL OPERATIONS OF THE SIMULATED SM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 106                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                      |

| 5.3 COMPONENTS OF THE SIMULATION PROGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                      |

| 5.4INITIALISATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                      |

| 5.5INTERFACE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                      |

| 5.6QUERYING THE SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 110                                                                                                  |

| 5.61 FRAME-RELATED CONJUNCTIVE QUERIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 112                                                                                                  |

| 5.611 OPTION ONE: QUERYING FOR A FULL DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 113                                                                                                  |

| 5.612OPTION TWO: QUERYING WITH PARTIAL DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                      |

| 5.62 DOMAIN-RELATED CONJUNCTIVE QUERIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |

| 5.621DOMAIN RELATED QUERIES OPTION TWO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                      |

| 5.7BENCHMARK KNOWLEDGE BASE AND ADT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 122                                                                                                  |

| 5.71BENCHMARK KNOWLEDGE BASE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 122                                                                                                  |

| 5.72 APPLICATION DEVELOPMENT TOOL (ADT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 125                                                                                                  |

| 5.8DISK-UNIT, HASHING, RETRIEVAL AND MAPPING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 126                                                                                                  |

| 5.81DISK-UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 126                                                                                                  |

| 5.82 THE HASHING ALGORITHM AND HASHING TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 129                                                                                                  |

| 5.821STRUCTURE OF HASH TABLES AND THEIR COMPONENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 131                                                                                                  |

| 5.83 RETRIEVAL AND MAPPING OF APPROPRIATE HIERARCHIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 133                                                                                                  |

| 5.9 RECTANGULAR ARRAY OF PEs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                      |

| 5.91 PEs, THEIR FUNCTIONS AND CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10/                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 136                                                                                                  |

| 5.91FES, THEIR FUNCTIONS AND CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 136                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 136                                                                                                  |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                      |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137                                                                                                  |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137                                                                                           |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140                                                                                    |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140                                                                                    |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>140                                                                             |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>140<br>141                                                                      |

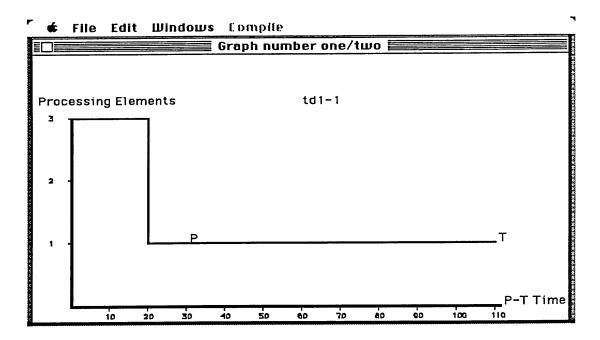

| 6.0 CHAPTER SIX: BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 137<br>137<br>140<br>140<br>141                                                                      |

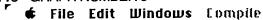

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>140<br>141<br>141<br>R-                                                         |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>141<br>141<br>R-<br>143                                                         |

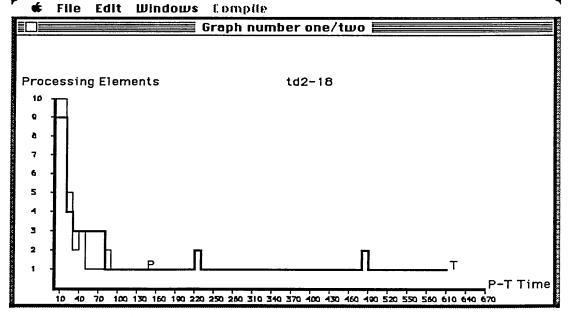

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>141<br>141<br>R-<br>143<br>144                                                  |

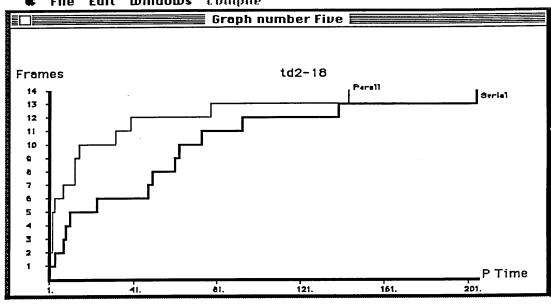

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>140<br>141<br>141<br>R-<br>143<br>144<br>147                                    |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>140<br>141<br>141<br>R-<br>143<br>144<br>147                                    |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>140<br>140<br>141<br>141<br>R-<br>143<br>144<br>147<br>148                                    |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>140<br>140<br>141<br>141<br>R-<br>143<br>144<br>147<br>148                                    |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>141<br>141<br>R-<br>143<br>144<br>147<br>148<br>148                             |

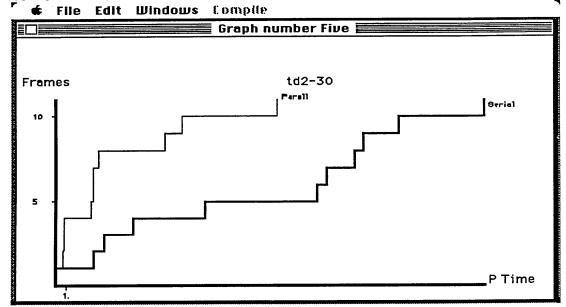

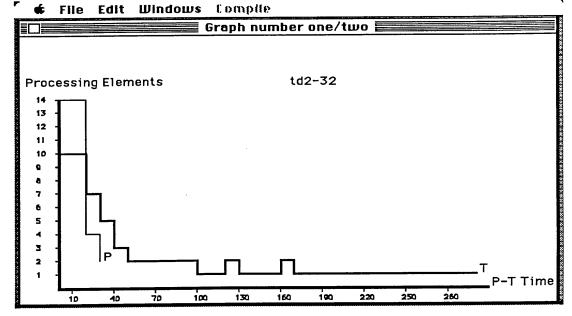

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137 137 140 141 141 R 143 144 147 148 148 149 150 152                                                |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION 6.2TIME DELAYS 6.21 LOADING AND COMPARISON 6.22 TRANSFERRING DATA PACKETS 6.3 VERIFICATION OF TIME-DELAY CALCULATIONS 6.31 VERIFICATION OF PROCESSING TIME 6.32 VERIFICATION OF CALCULATING PACKET'S SIZE AND ITS TRANSFEITIME 6.33 A TEST-RUN EXAMPLE 6.4 GRAPHICS PACKAGE 6.41 GRAPH NUMBER ONE 6.42 GRAPH NUMBER 1/2 6.43 GRAPH NUMBER 5 6.5 EVALUATION AND CONCLUSIONS 6.51 QUERY-OBJECT NUMBER 1'S TEST-RUNS                                                                                                                                                                                                                   | 137 137 140 141 141 R 143 144 147 148 148 149 150 152                                                |

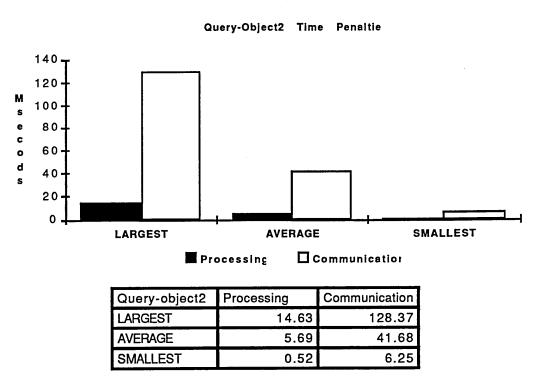

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137 137 140 140 141 141 R 143 144 147 148 148 149 150 152 154                                        |

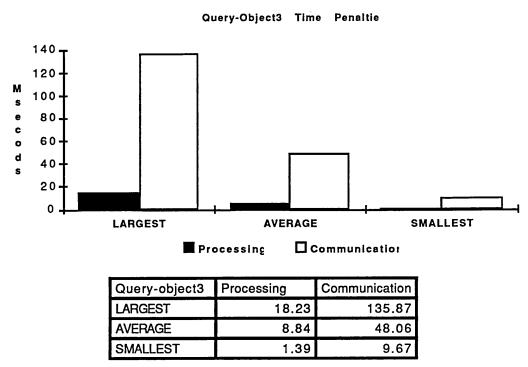

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>141<br>141<br>R-<br>143<br>144<br>147<br>148<br>148<br>149<br>150<br>152<br>154 |

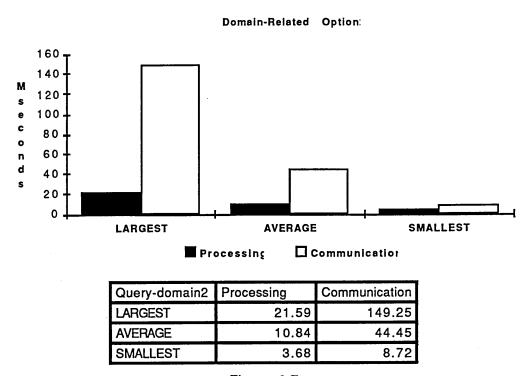

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>141<br>141<br>R-<br>143<br>144<br>147<br>148<br>148<br>149<br>150<br>152<br>154 |

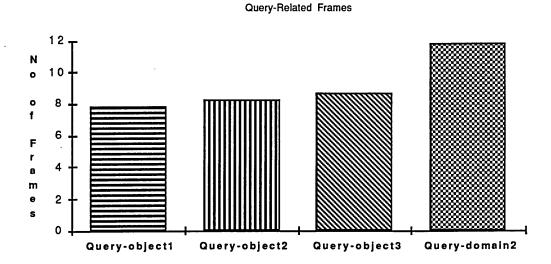

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br>137<br>140<br>141<br>141<br>R-<br>143<br>144<br>147<br>148<br>148<br>149<br>150<br>152<br>154 |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION 6.2TIME DELAYS. 6.21LOADING AND COMPARISON 6.22TRANSFERRING DATA PACKETS 6.3VERIFICATION OF TIME-DELAY CALCULATIONS 6.31VERIFICATION OF PROCESSING TIME 6.32VERIFICATION OF CALCULATING PACKET'S SIZE AND ITS TRANSFEITIME 6.33A TEST-RUN EXAMPLE 6.4GRAPHICS PACKAGE 6.41GRAPH NUMBER ONE 6.42GRAPH NUMBER 1/2 6.43GRAPH NUMBER 5 6.5EVALUATION AND CONCLUSIONS 6.51QUERY-OBJECT NUMBER 1'S TEST-RUNS 6.52QUERY-OBJECT NUMBER 2'S TEST-RUNS 6.53QUERY-OBJECT NUMBER 3'S TEST-RUNS 6.54TEST-RUNS FOR DOMAIN RELATED QUERIES OPTION TWO 6.55CONCLUSIONS                                                                              | 137 137 140 141 141 R 143 144 147 148 148 149 150 152 156 156                                        |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION 6.2TIME DELAYS 6.21LOADING AND COMPARISON 6.22TRANSFERRING DATA PACKETS 6.3VERIFICATION OF TIME-DELAY CALCULATIONS 6.31VERIFICATION OF PROCESSING TIME 6.32VERIFICATION OF CALCULATING PACKET'S SIZE AND ITS TRANSFEITIME 6.33A TEST-RUN EXAMPLE 6.4GRAPHICS PACKAGE 6.41GRAPH NUMBER ONE 6.42GRAPH NUMBER 1/2 6.43GRAPH NUMBER 5 6.5EVALUATION AND CONCLUSIONS 6.51QUERY-OBJECT NUMBER 1'S TEST-RUNS 6.52QUERY-OBJECT NUMBER 2'S TEST-RUNS 6.53QUERY-OBJECT NUMBER 3'S TEST-RUNS 6.54TEST-RUNS FOR DOMAIN RELATED QUERIES OPTION TWO 6.55CONCLUSIONS 7.0CHAPTER SEVEN : CONCLUSIONS AND FUTURE WORK 7.1CONCLUSIONS                 | 137 137 140 140 141 141 R 143 144 147 148 149 150 152 154 155                                        |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION 6.2TIME DELAYS. 6.21LOADING AND COMPARISON 6.22TRANSFERRING DATA PACKETS 6.3VERIFICATION OF TIME-DELAY CALCULATIONS 6.31VERIFICATION OF PROCESSING TIME 6.32VERIFICATION OF CALCULATING PACKET'S SIZE AND ITS TRANSFEITIME 6.33A TEST-RUN EXAMPLE 6.4GRAPHICS PACKAGE 6.41GRAPH NUMBER ONE 6.42GRAPH NUMBER 1/2 6.43GRAPH NUMBER 5 6.5EVALUATION AND CONCLUSIONS 6.51QUERY-OBJECT NUMBER 1'S TEST-RUNS 6.52QUERY-OBJECT NUMBER 2'S TEST-RUNS 6.53QUERY-OBJECT NUMBER 3'S TEST-RUNS 6.54TEST-RUNS FOR DOMAIN RELATED QUERIES OPTION TWO 6.55CONCLUSIONS                                                                              | 137 137 140 140 141 141 R 143 144 147 148 149 150 152 154 155                                        |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION 6.2TIME DELAYS. 6.21LOADING AND COMPARISON 6.22TRANSFERRING DATA PACKETS 6.3VERIFICATION OF TIME-DELAY CALCULATIONS 6.31VERIFICATION OF PROCESSING TIME 6.32VERIFICATION OF CALCULATING PACKET'S SIZE AND ITS TRANSFEITIME 6.33A TEST-RUN EXAMPLE 6.4GRAPHICS PACKAGE 6.41GRAPH NUMBER ONE 6.42GRAPH NUMBER 1/2 6.43GRAPH NUMBER 5 6.5EVALUATION AND CONCLUSIONS 6.51QUERY-OBJECT NUMBER 1'S TEST-RUNS 6.52QUERY-OBJECT NUMBER 2'S TEST-RUNS 6.53QUERY-OBJECT NUMBER 3'S TEST-RUNS 6.54TEST-RUNS FOR DOMAIN RELATED QUERIES OPTION TWO 6.55CONCLUSIONS 7.0CHAPTER SEVEN : CONCLUSIONS AND FUTURE WORK 7.1CONCLUSIONS 7.2FUTURE WORK | 137 137 140 140 141 141 R 143 144 147 148 149 150 152 156 156                                        |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION 6.2TIME DELAYS 6.21LOADING AND COMPARISON 6.22TRANSFERRING DATA PACKETS 6.3VERIFICATION OF TIME-DELAY CALCULATIONS 6.31VERIFICATION OF PROCESSING TIME 6.32VERIFICATION OF CALCULATING PACKET'S SIZE AND ITS TRANSFEITIME 6.33A TEST-RUN EXAMPLE 6.4GRAPHICS PACKAGE 6.41GRAPH NUMBER ONE 6.42GRAPH NUMBER 1/2 6.43GRAPH NUMBER 5 6.5EVALUATION AND CONCLUSIONS 6.51QUERY-OBJECT NUMBER 1'S TEST-RUNS 6.52QUERY-OBJECT NUMBER 2'S TEST-RUNS 6.53QUERY-OBJECT NUMBER 3'S TEST-RUNS 6.54TEST-RUNS FOR DOMAIN RELATED QUERIES OPTION TWO 6.55CONCLUSIONS 7.0CHAPTER SEVEN : CONCLUSIONS AND FUTURE WORK 7.1CONCLUSIONS                 | 137 137 140 140 141 141 R 143 144 147 148 149 150 152 156 156                                        |

| 6.0 CHAPTER SIX : BENCHMARKING AND EVALUATION 6.1INTRODUCTION 6.2TIME DELAYS. 6.21LOADING AND COMPARISON 6.22TRANSFERRING DATA PACKETS 6.3VERIFICATION OF TIME-DELAY CALCULATIONS 6.31VERIFICATION OF PROCESSING TIME 6.32VERIFICATION OF CALCULATING PACKET'S SIZE AND ITS TRANSFEITIME 6.33A TEST-RUN EXAMPLE 6.4GRAPHICS PACKAGE 6.41GRAPH NUMBER ONE 6.42GRAPH NUMBER 1/2 6.43GRAPH NUMBER 5 6.5EVALUATION AND CONCLUSIONS 6.51QUERY-OBJECT NUMBER 1'S TEST-RUNS 6.52QUERY-OBJECT NUMBER 2'S TEST-RUNS 6.53QUERY-OBJECT NUMBER 3'S TEST-RUNS 6.54TEST-RUNS FOR DOMAIN RELATED QUERIES OPTION TWO 6.55CONCLUSIONS 7.0CHAPTER SEVEN : CONCLUSIONS AND FUTURE WORK 7.1CONCLUSIONS 7.2FUTURE WORK | 137 137 140 140 141 141 143 144 147 148 149 150 156 156 156                                          |

| APPENDIX B: BENCHMARK KNOWLEDGE BASE App-B | page 1                        | 1           |

|--------------------------------------------|-------------------------------|-------------|

| APPENDIX C: TEST-RUNSApp-C                 | page 1                        | 1           |

| APPENDIX D : GRAPHS                        | page 22<br>page 12<br>page 23 | 2<br>2<br>3 |

| APPENDIX E : JOIN IN FRAMESApp-E           | page 1                        | 1           |

# TABLE OF FIGURES

| Figure 1.1, A graphical representation of a search space                                   | 4    |

|--------------------------------------------------------------------------------------------|------|

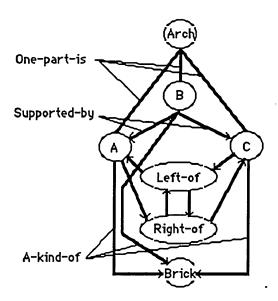

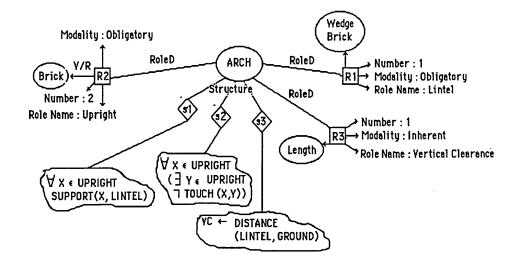

| Figure 2.1, Structured Description of an Arch                                              |      |

| Figure 2.2, showing an example of semantic net                                             |      |

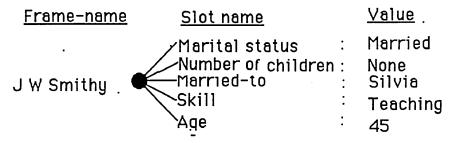

| Figure 2.3, an example of a frame                                                          |      |

| Figure 2.4, a KL-ONE concept for a simple arch                                             |      |

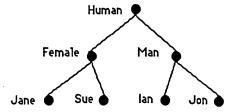

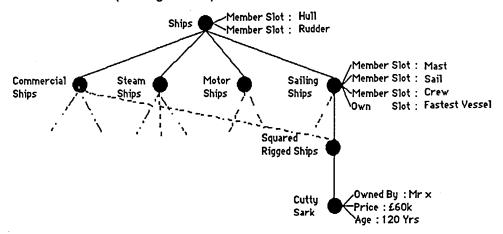

| Figure 2.5, Shows a classified hierarchy                                                   |      |

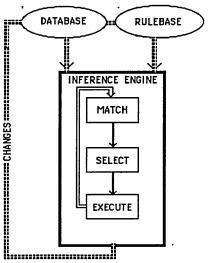

| Figure 2.6, Computational model of production system                                       | .27  |

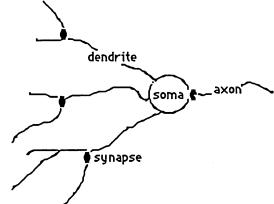

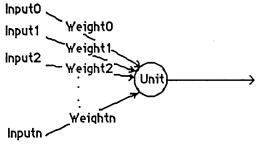

| Figure 3.1, Basic features of a biological neuron                                          | .44  |

| Figure 3.2, McCulloch-Pitts neuron                                                         | .45  |

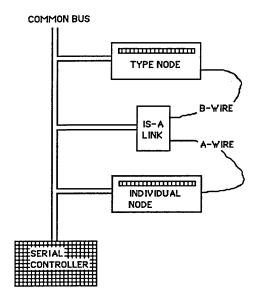

| Figure 3.3, the basic hardware components in NETL                                          | .47  |

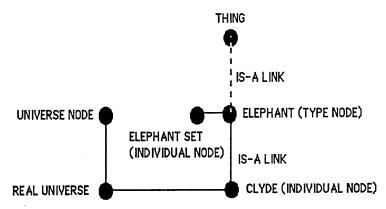

| Figure 3.4, a description for an individual concept                                        |      |

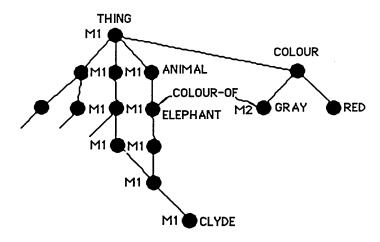

| Figure 3.5, an example of marker propagation                                               | .50  |

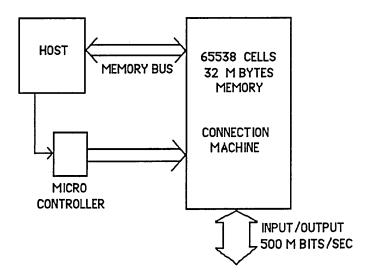

| Figure 3.6, the architecture of the Connection Machine                                     |      |

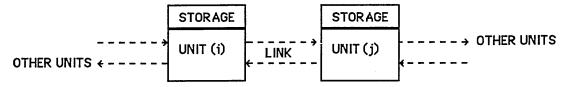

| Figure 3.7, the basic physical units in Boltzmann machine                                  |      |

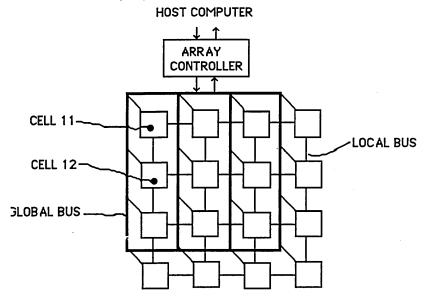

| Figure 3.8, the architecture of SNAP                                                       | .54  |

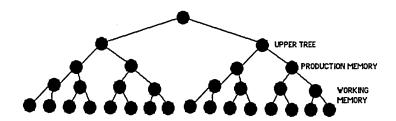

| Figure 3.9, the architecture of DADO Machine                                               | .55  |

| Figure 3.10, the hardware organisation of NO-VAN machine                                   | .56  |

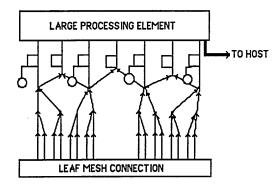

| Figure 3.11 the SM architecture at the start of the project                                | .57  |

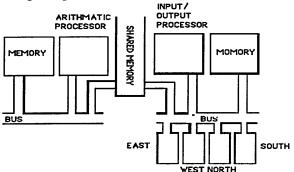

| Figure 3.12, a Processing Element in the SM                                                | .58  |

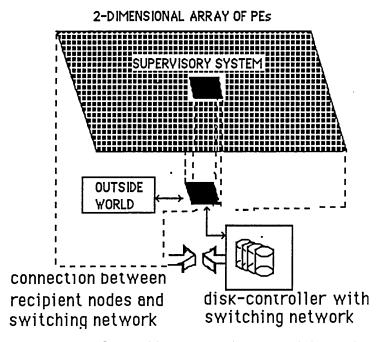

| Figure 3.13, the new architecture of the SM                                                | .59  |

| Figure 3.14, characteristics of some of the knowledge based machines                       | .61  |

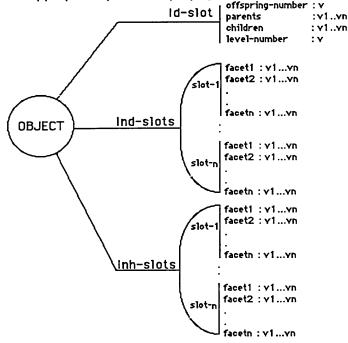

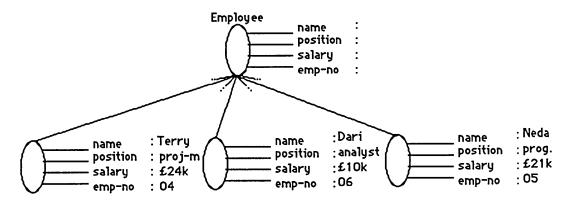

| Figure 4.1, a schematic representation of a frame                                          | .73  |

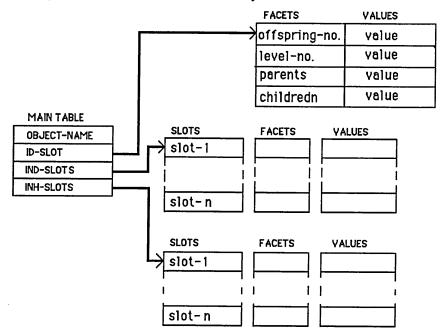

| Figure 4.2, The implemented version of frame structure                                     | .74  |

| Figure 4.3, representation of a slot with its facets                                       | .75  |

| Figure 4.4, Low level frame structure                                                      | .75  |

| Figure 4.5 Data packet propagation                                                         | .81  |

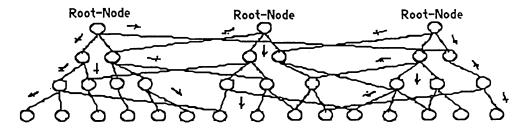

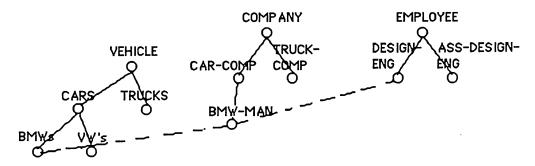

| Figure 4.6, fragments of three different hierarchies                                       | .84  |

| Figure 4.7, an example of a frame in the knowledge base                                    | .86  |

| Figure 4.8, an example of upward pointers                                                  |      |

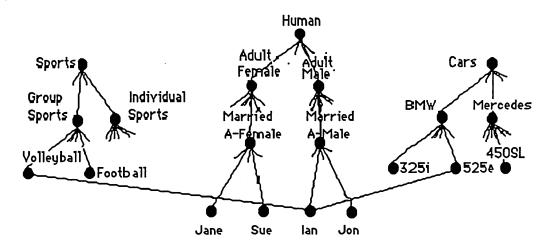

| Figure 4.9, an example of a different hierarchies                                          |      |

| Figure 4.10, a simple relation 'employee'                                                  |      |

| Figure 4.11, the representation of a simple relation in frame-based                        |      |

| hierarchy                                                                                  | 00   |

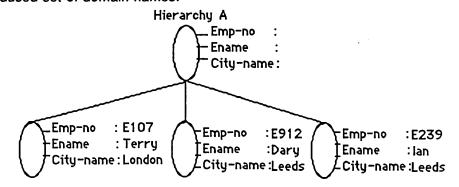

| Figure 4.12, relation A1                                                                   | 01   |

| Figure 4.13, relation B1                                                                   | 02   |

| Figure 4.14, the result of equijoin on relations A and B                                   | 02   |

| Figure 4.15, the result of natural join on relations A and B                               | 02   |

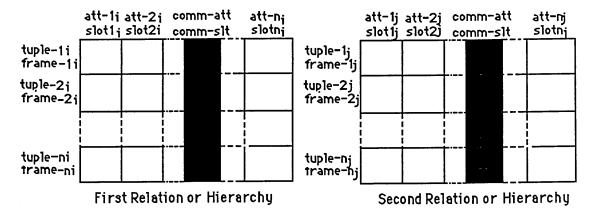

| Figure 4.16, a simple relation 'A' is represented as a hierarchy of frames. 1              | 03   |

| Figure 4.17, a simple relation 'B' is represented as a hierarchy of frames. 1              | .03  |

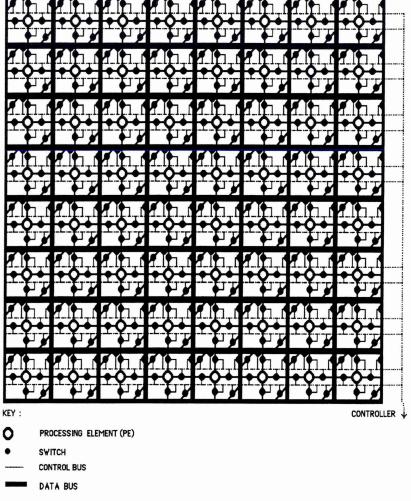

| Figure 5.1, the block diagram of the SM system1                                            | 05   |

| Figure 5.2, The main components of the simulation program                                  | .08  |

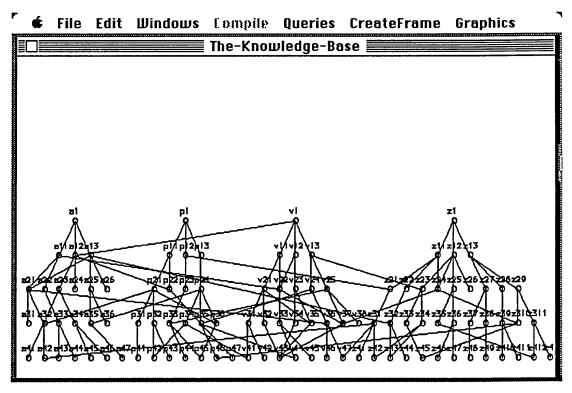

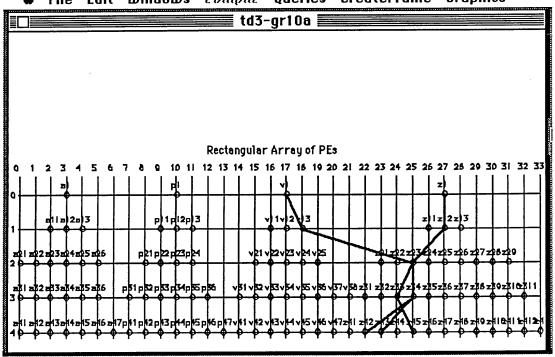

| Figure 5.3, a screen dump of a simulation run1                                             | 10   |

| Figure 5.4, the query system1                                                              | 11   |

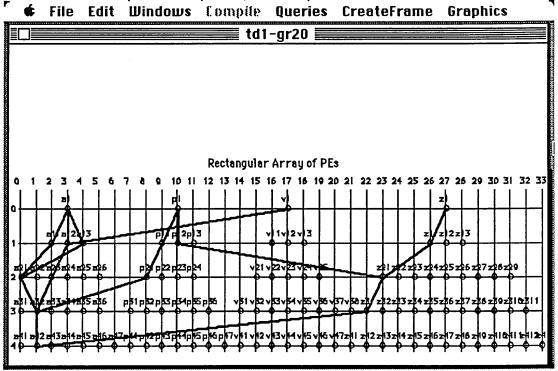

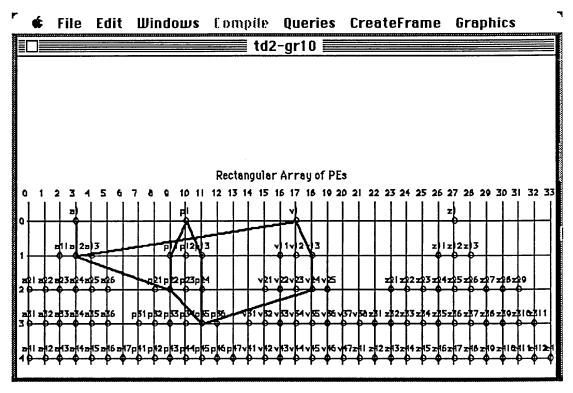

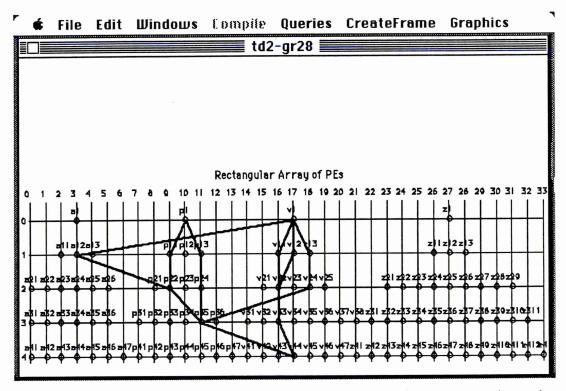

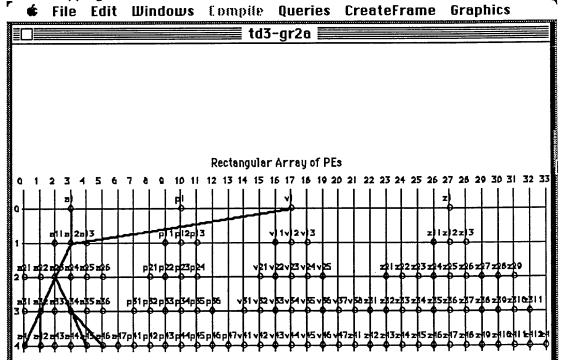

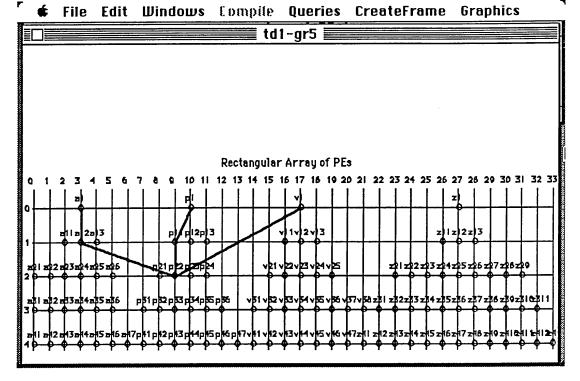

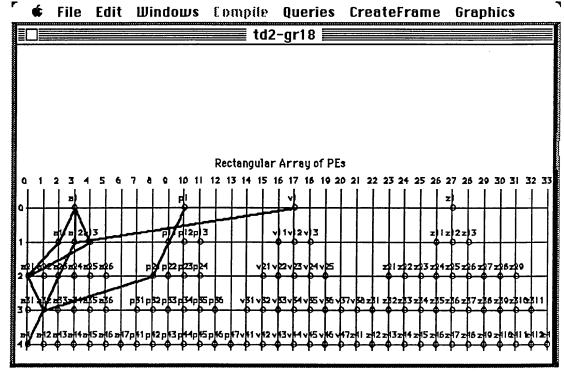

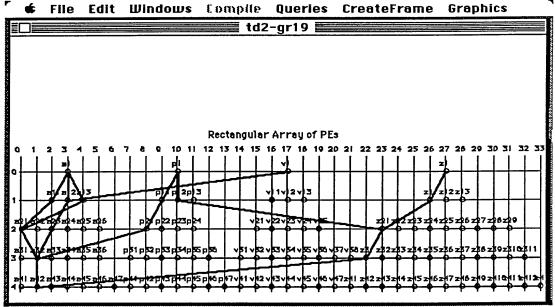

| Figure 5.5, a screen dump of a run-time graph showing all the relevant                     |      |

| propagation paths1 Figure 5.6, a screen dump of a run-time graph showing all the relevant  | 14   |

| Figure 5.6, a screen dump of a run-time graph showing all the relevant                     |      |

| propagation paths,                                                                         | 16   |

| Figure 5.7, a screen dump of a run-time graph showing all the relevant                     |      |

| propagation paths1                                                                         | 19   |

| propagation paths1 Figure 5.8, a screendump of a run-time graph for domain related queries |      |

| type two 1                                                                                 | 21   |

| Figure 5.9, a screen dump of the bench mark knowledge base                                 | 24   |

| Figure 5.10, disk storage in the simulation1                                               | 28   |

| Figure 5.11, the structure of the disk_index                                               | 32   |

| Figure 5.12, the structure of the controller-copy1                                         |      |

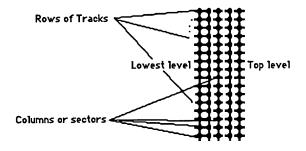

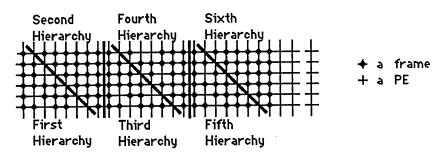

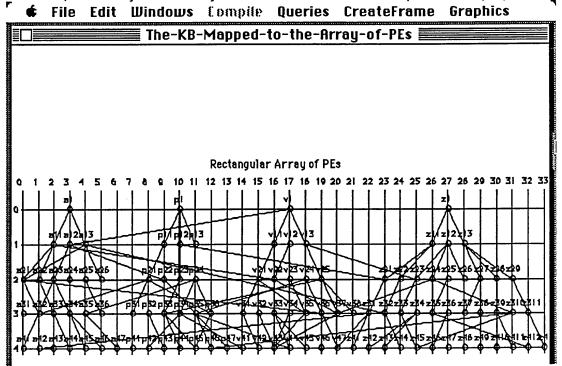

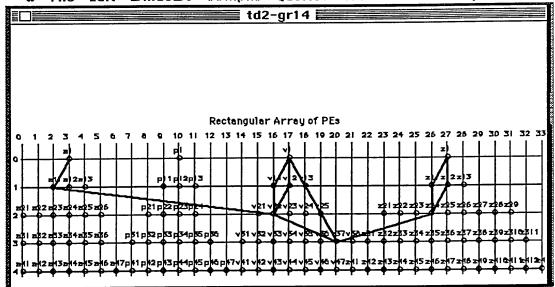

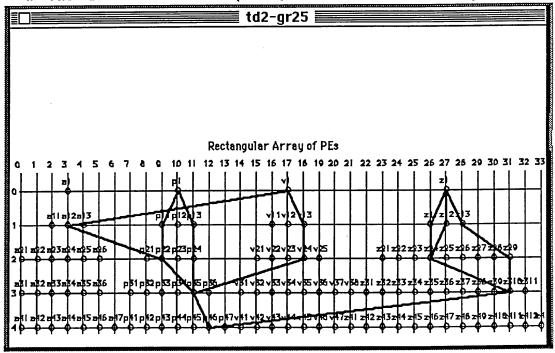

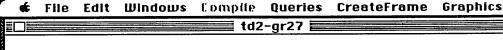

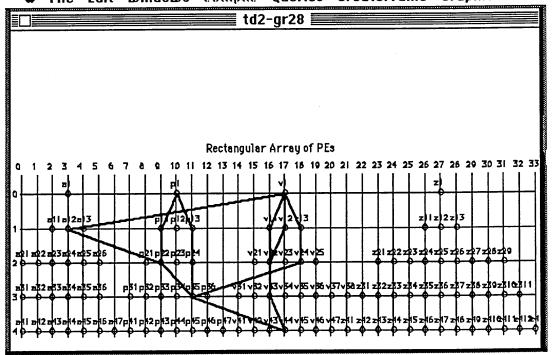

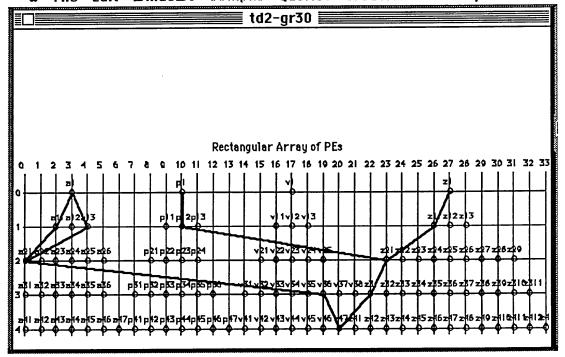

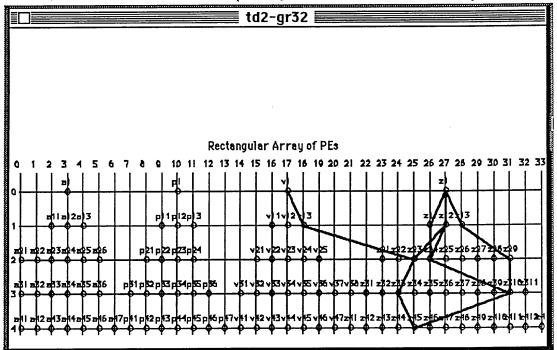

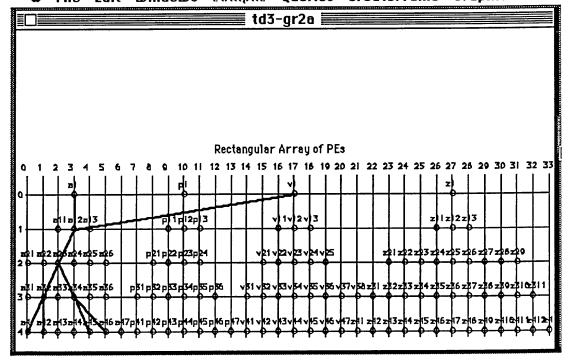

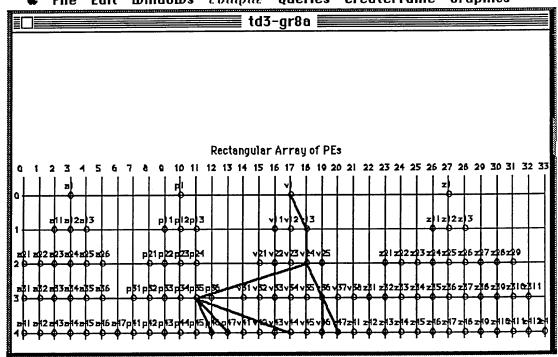

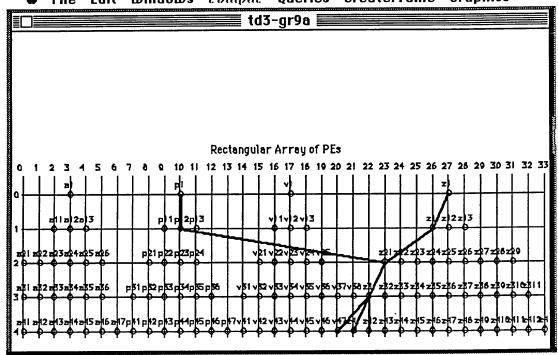

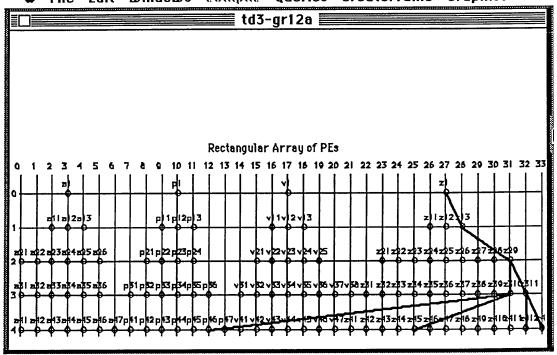

| Figure 5.13, mapping of several hierarchies                                                | 34   |

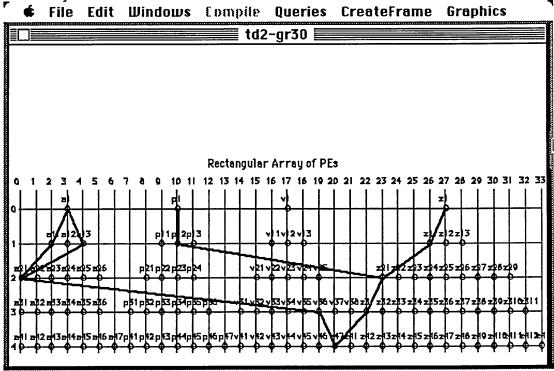

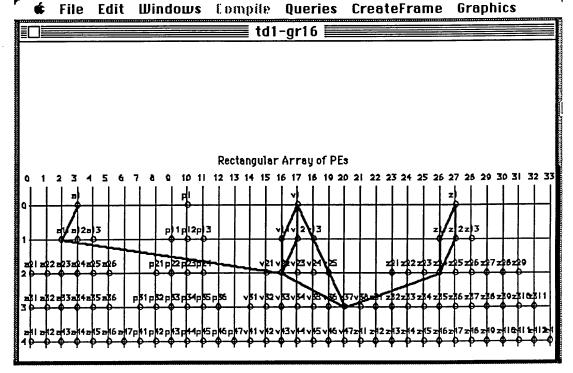

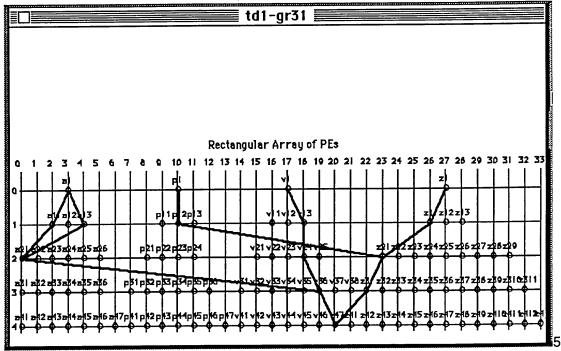

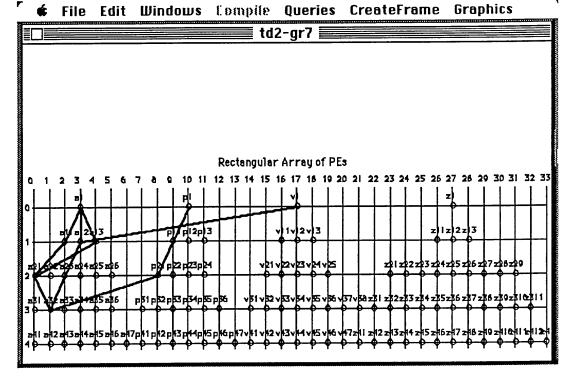

| Figure 5.14, a screen dump of graphics representation of a rectangular a                   | rray |

| of PEs                                                                                     |      |

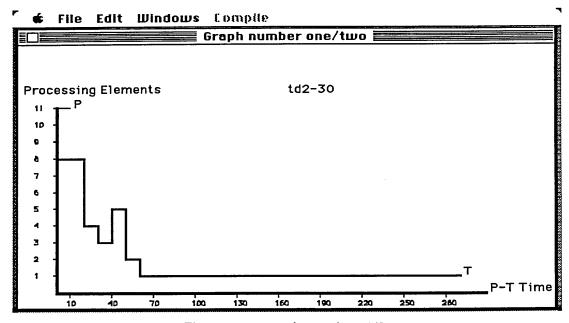

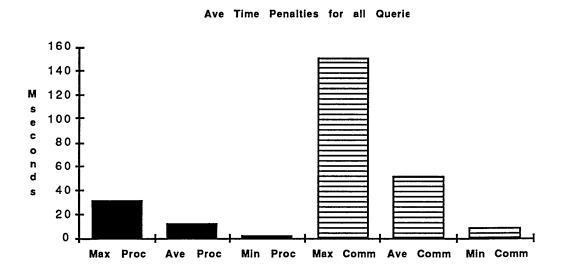

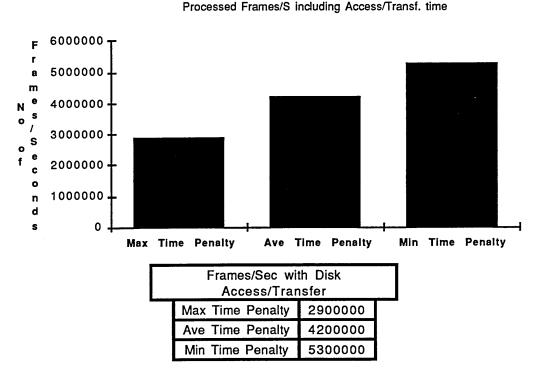

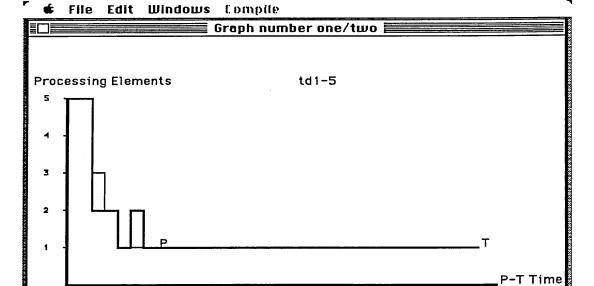

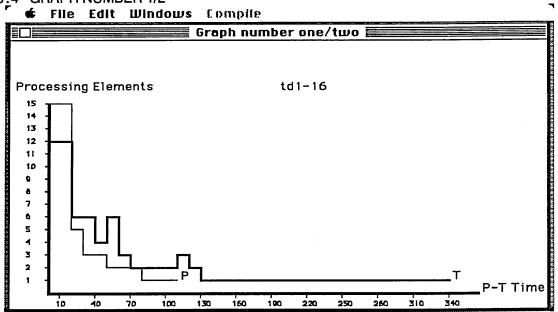

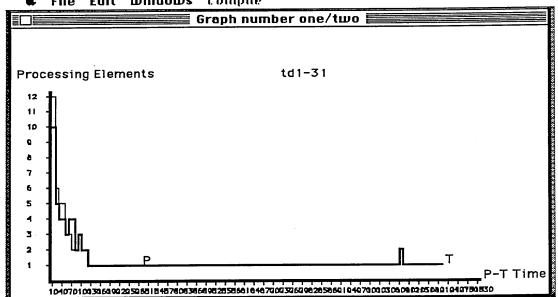

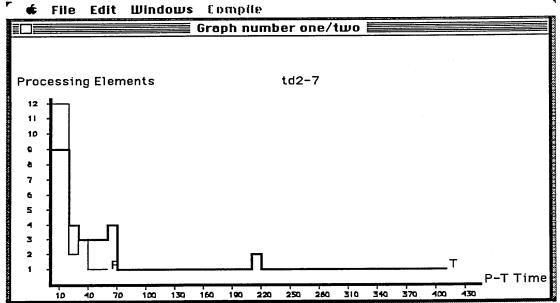

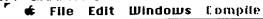

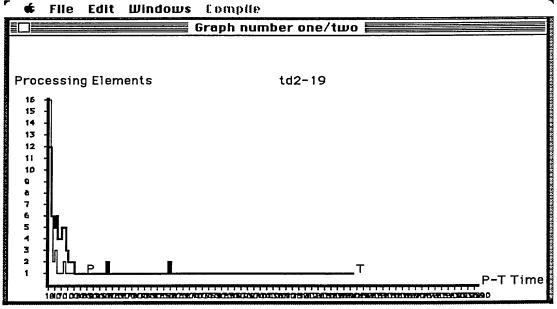

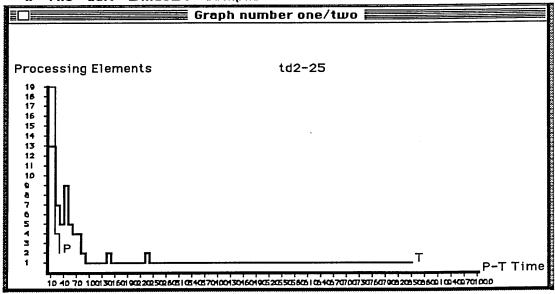

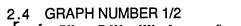

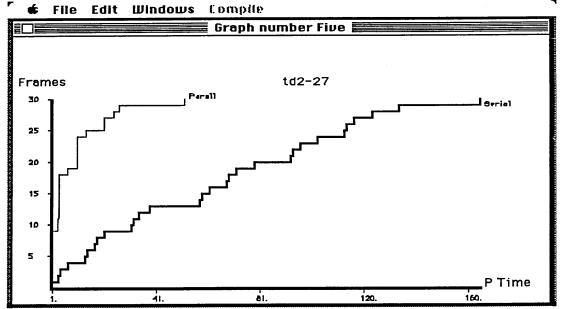

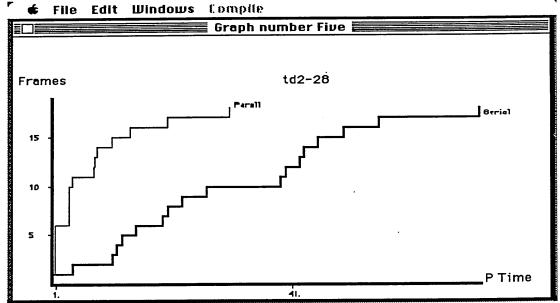

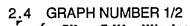

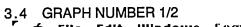

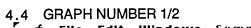

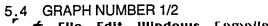

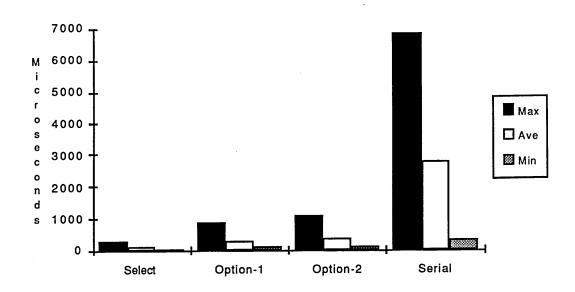

| Figure 6.1, graph number one                                                    | 148            |

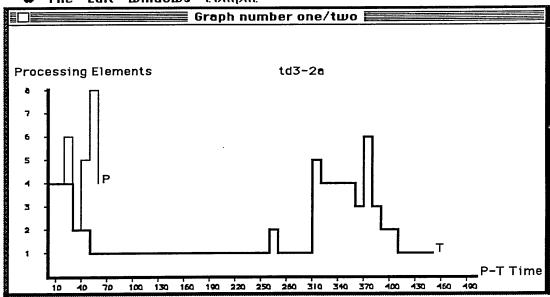

|---------------------------------------------------------------------------------|----------------|

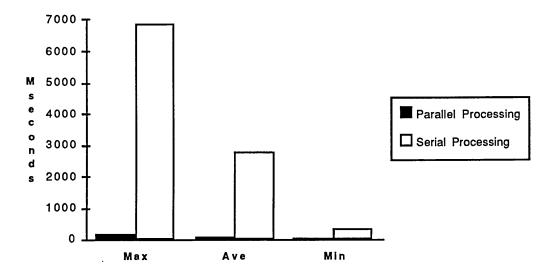

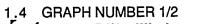

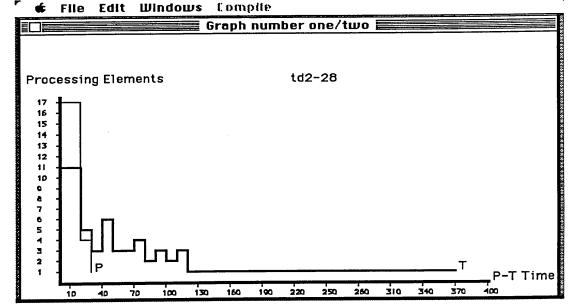

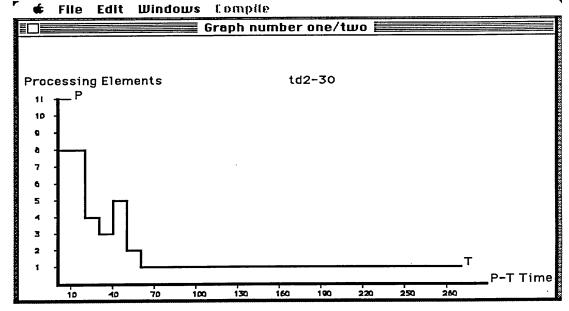

| Figure 6.2, graph number 1/2                                                    | 149            |

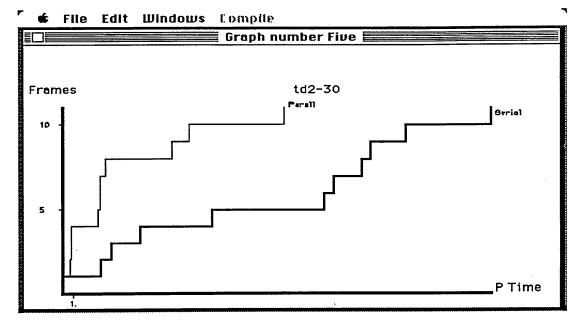

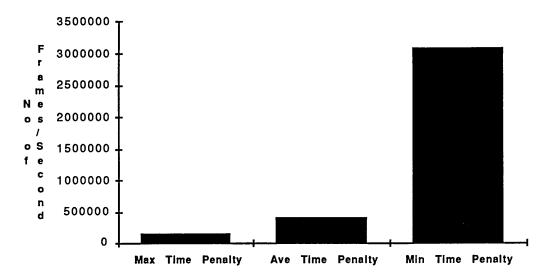

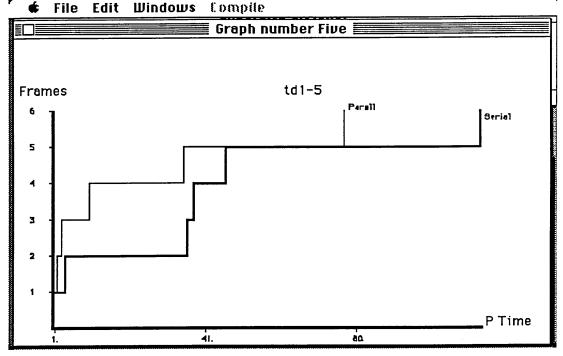

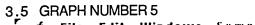

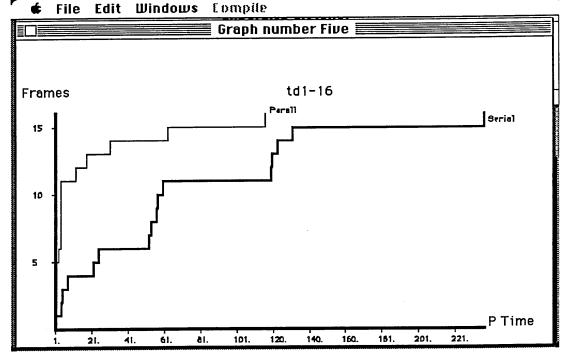

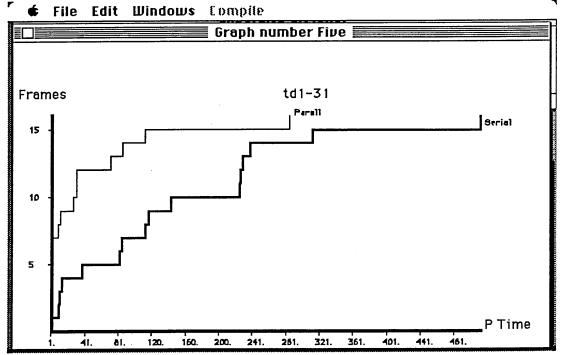

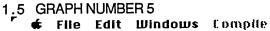

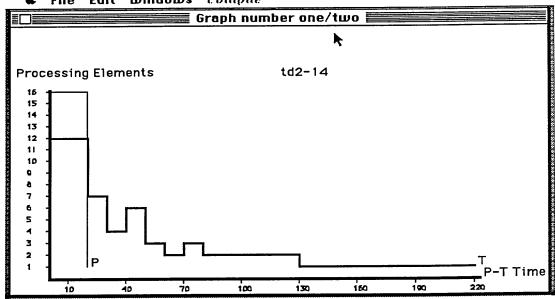

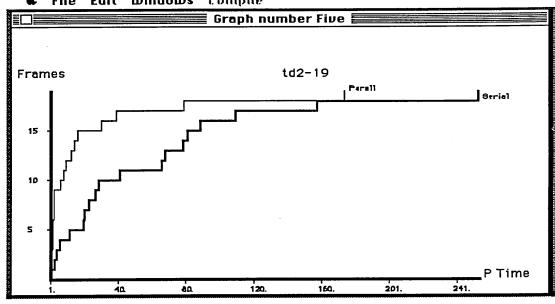

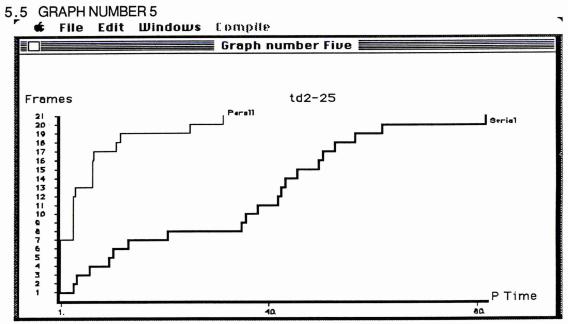

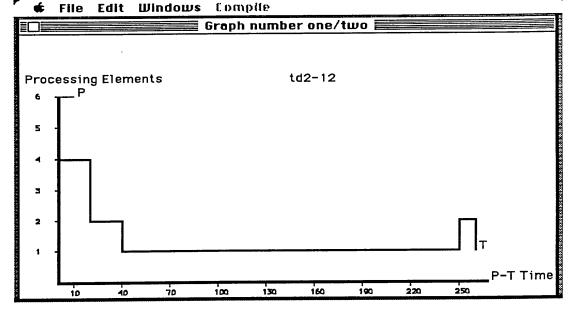

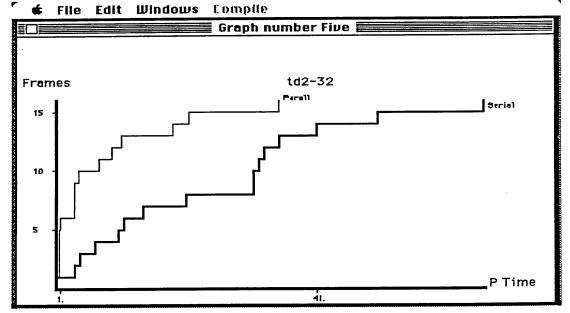

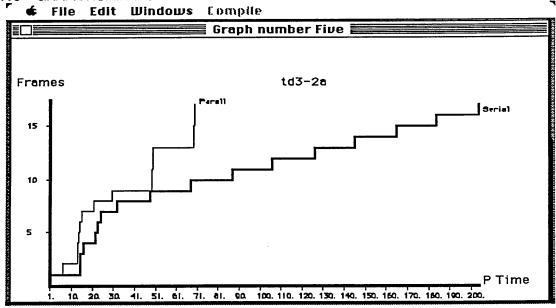

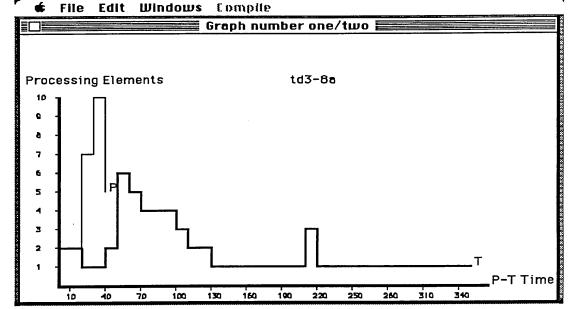

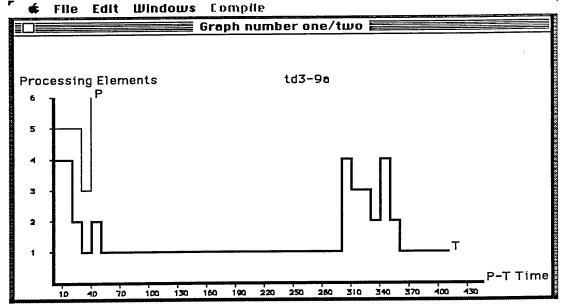

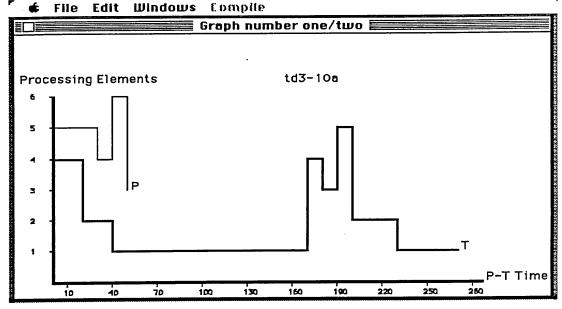

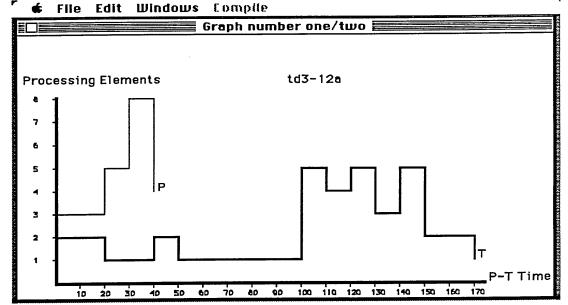

| Figure 6.3, graph number 5                                                      |                |

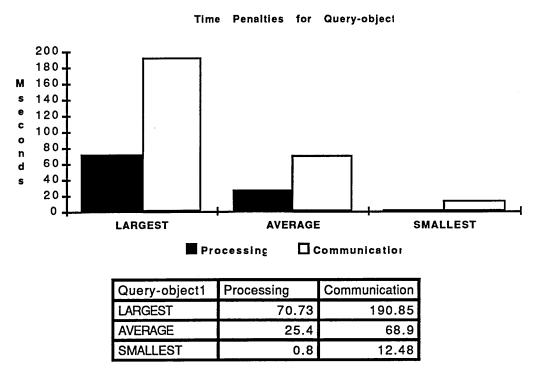

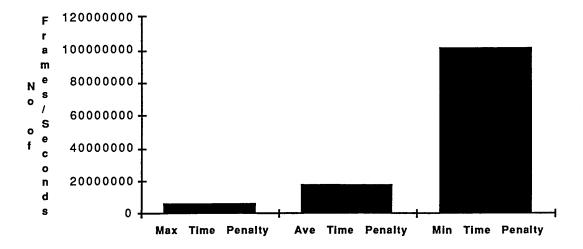

| Figure 6.4                                                                      |                |

| Figure 6.5                                                                      |                |

| Figure 6.6                                                                      |                |

| Figure 6.7                                                                      | 156            |

| Figure 6.8, the average number of query-related frames in                       | 4 different    |

| queries                                                                         | 157            |

| Figure 6.9, a range of average time penalties for communon query-related frames |                |

| Figure 6.10, a comparison of serial/parallel processing of the                  | he same number |

| of frames                                                                       | 159            |

| Figure 6.11                                                                     |                |

|                                                                                 |                |

| Figure 6.12                                                                     | 161            |

#### 1.1 INTRODUCTION

We have come a long way in the history of mankind in terms of achievement in technological, sociological, political and many other aspects of life. achievements are a result of man's endeavour from the ancient to the present time, and due to his innovation and creativity. In the East, people used the abacus as a mechanical calculator for their commercial applications (Metropolis 1980), whereas in the West, it was only after the introduction of the Arabic numeral system that the medieval European was able to perform complicated calculations. It was around the 16th century that, instead of using empirical knowledge, mariners used mathematically based charts to find their destinations (Pratt 1987). After the renaissance and the establishment of modern science, the idea that thinking might be provided by a machine, was born. This idea was later put in practice -albeit in a limited form- by people including Leibniz's calculator and the Analytical Engine created by Babbage (Hyman 1991). Zuse in Berlin in 1936, Atanasoff in Ohio in 1937, and the Bell Telephone laboratories in New York (Schutzer 1987), and many other individuals and organisations, were theorising on, and in some cases, developing, new calculating machines. During the second world war, and the dire necessities associated with it, machines, mostly electromechanically based, were developed for tasks including deciphering radio traffic, and the calculation of firing tables for artillery. This led to the development of machines such as ENIAC in USA and ENIGMA in Britain (Metropolis 1980). Associated with the rapid development of machines in this century, was "electricity". The crucial role that electricity played was to replace the heavy mechanical components (eg metal rods and cogs etc.) with cables and switches (Andriole 1985) and thus, a substantial increase in the speed of processing was gained.

Although the automation of the mind has long been an ambition for man, all the efforts up to the beginning of this century were 'only' leading to automation of calculation ie, the development of machines for faster mathematical computation, namely addition, subtraction, division and multiplication. It was only later, with the tremendous advancements in mathematics, electrical and electronic engineering, psychology and philosophy that the concept of automation of thought was perceived, by pioneers like Alan Turing, Emil Post and Alonzo Church, to be a possibility (Cohen 1981). Turing's idea was to build, not an automated reasoner, nor a machine capable of understanding the universal language of algebra, but a machine that would have powers coextensive with that of human brain. This idea was shared by many pioneers involved with automated computational theories, including John von Neumann, but his perspective

was influenced by the technological limitations imposed on developing such machines. He took charge of the next development of a new machine based on ENIAC, called EDVAC. In this machine, a new concept of fundamental importance was developed<sup>1</sup>, that of the "stored program" (Albus 1981).

The development of digital computers continued, and along with it, the desire to imitate human thinking grew. In this development, the mathematicians had the most important role, and their main interest was to develop a machine which was able to make a contribution to mathematics. Another group: engineers, were interested in modern computers and, at a practical level, understood them well. The concept of automatic data-handling was an attractive idea for people in commerce, and those who were interested in non-mathematical applications in computing. There were others, who had the intention of utilising computers for intellectual purposes. At the beginning of the twentieth century, a certain amount of research was done on the nervous system in the context of psychology; in particular, behaviourism. This field of research became known as "cybernetics".

The members of the cybernetics group were from different backgrounds and disciplines, including mathematicians and engineers, whose programs were drawn together under the inspiration of Weiner in 1940s. The main research projects in cybernetics, then, was concerened with the application of control engineering concepts to the understanding of physiological and neurophysiological processes. This work involved people like Weiner, Rosenblueth, McCulloch, Pitts and others (Pratt 1987). With the observations made by Cajal, through his work involving anatomy of the nervous system (Rumelhart 1987), the cybernetics group were able to theorise on the concepts and properties that he produced. As a result of Cajal's work, it was possible to work on systems made up of a number of neurons, and use their interconnections and the properties they offered. The interconnections of neurons and specified properties attributed to each neuron were seen as nerve-nets (or neural net of today), and a substantial amount of work was done by people like McCulloch and Pitts, which greatly contributed to today's understanding of neural nets (Aleksander 1990).

In Dartmouth college, in 1956, a conference was organised by a young mathematician, John McCarthy and his colleague Marvin Minsky from MIT. In this conference McCarthy proposed a study of Artificial Intelligence which would describe the creation of a machine that will simulate human's intelligence (Charniak 1987). Since 1956, the term "Artificial Intelligence" ("Al") has been used for every aspect of developing

Note that there is a controversy about the origin of this idea of " stored program". For further details see (Pratt 1987), pp167.

systems that had something to do with human thought processing. Visual perception and pattern recognition, natural language understanding, problem solving and game playing, are some of the fields which were rapidly developing under Al's umbrella. It has been claimed that modern perspectives in psychology, embodied in congnitive psychology, owes its existence and reputation to Al (Winston 1977). Newell and Simon (Newell 1972, Newell 1976) were two of the pioneers that brought this new perspective to psychology, and exerted a strong influence both in this field and in other subfields of Al.

After developing machines with stored programs however, there were opportunities for people working in the AI community, to implement different applications. But while the complexities of these applications increased, their requirements remained the same; that is, an embodied program, a large amount of memory, and high speed.

Since 1950, in the succeeding decades, the complexity and consequently the widening of applications in Al, made it apparent that the serial machines, or von Neumann machines, could not meet their requirements. The main characteristic of these applications is the amount of knowledge that they require. Given the time constraints, it would be impossible to explore the information, which is a pre-requisite to any consequent inferences and conclusions. The realisation of this concept was the main encouragement for a big international push, that started in 1981. At this time, large computing research and development projects had been started by almost two dozen nations. EEC's ESPRIT (European Strategy Research Program in industrial Information Technology), UK's ALVEY, Japan's ICOT (Institute for New Generation Computer Technology), MCC (Computer Technology Corporation) and DARPA (Defence Advance Research Project Agency) in the USA and national programs in Soviet Union and other Eastern Bloc Nations, geared up to pursue advanced computing technology and developing machines for diverse Al applications (A datamation Staff Report 1985, Delgado-Frias 1987). Despite the substantial decrease in financial support for the continuation of this research and development, all these initiatives pushed the state of the art forward in many directions, covering a wide range of branches in Al and in computer science generally. Some of these applications are :

- a) Knowledge representation paradigm,

- b) Knowledge based systems,

- c) Natural language understanding and speech processing,

- d) Robotics<sup>2</sup>,

- e) Theorem proving,

This is not a common view. This field involves AI, electrical, mechanical and optical engineering.

- f) Automatic programming,

- g) Perception.

The first two application areas of AI, knowledge representation and knowledge based systems (eg, expert systems), are undoubtedly the most important areas that have influenced computers, their architectures and languages. In many automated problem solving systems (eg expert systems), there are three main sections: the knowledge base, that is the representation of empirical human knowledge in a specific domain; the inference engine, employed to deduce facts or induce hypotheses in the given domain; and the interface between the outside world and the system.

In order to automate any problem solving, there are two main principles that have to be considered; searching, and knowledge representation. The representation of knowledge involves specific formatting of the information retrieved from the application domain and their relevant expert(s), which should be represented correctly. Representation should be simple and easy to understand, so that it can be modified and updated. A bad representation will always produce difficulties in its manipulation (eg, Roman numbering systems).

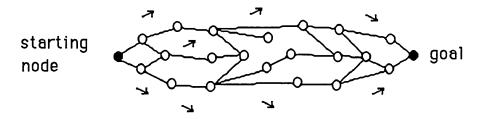

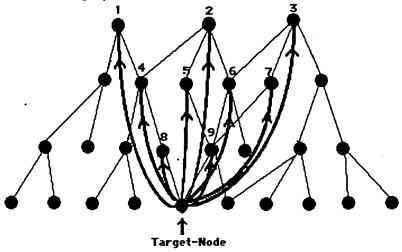

The methods of searching or exploring the knowledge representing the application domain, are also extremely important. A method should, given a number of options, indicate which is to be selected in order to reach the goal. The problem of search is to find the next appropriate move (like chess). In a search space which encapsulates the problem domain, we start from a node (see figure 1.1) and try to get to the goal state.

Figure 1.1, a graphical representation of a search space.

In the process of searching, each time that a move is taken, there is a new series of options available for selection. This causes a problem, in particular in a complex search space, in that the number of options become so great that they cannot all, within a given time constraint, be exhaustively investigated. This is called the combinatorial explosion. In AI, many attempts have been made to find the most economical way of arriving at the goal state (Kanal 1988). It must be noted that in a complex problem, because of the great number of options available, even finding the most relatively economical option is still a challenge. As an example, in order to find the shortest route

between two towns in an 'n' town map, there are (n - 1)! possibilities to explore (say 10 towns has 9! which is 362880 possibilities).