# Sheffield Hallam University

A Petri net-occam based methodology for the development of dependable distributed control software.

GRAY, Peter A.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/19716/

# A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/19716/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

Sheffield Hallam University

# **REFERENCE ONLY**

ProQuest Number: 10697018

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 10697018

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code Microform Edition © ProQuest LLC.

> ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

A Petri Net-Occam Based Methodology for the Development of Dependable Distributed Control Software

Peter Andrew Gray BSc MTech MSc

A thesis submitted in partial fulfilment of the requirements of Sheffield Hallam University for the degree of Doctor of Philosophy

December 1995

### Abstract

Analysis of flexible manufacturing cells (FMCs) shows their requirement for flexible, correct, reliable, safe and distributed control. A comparison of the state of the art in software engineering for parallel systems, and an examination of safety related systems, reveal a need for formal and rigorous techniques at all stages in the software life cycle. However, parallel software, safety related software and formal techniques are complex. It is better to avoid faults rather than eliminate or tolerate them, and although less flexible, avoidance is often simpler to implement.

There is a need for a tool which overcomes many of these complexities, and this thesis discusses and defines such a tool in the form of a methodology. The novelty of the work is in the combination of the core goals to manage these issues, and how the strategies guide the user to a solution which will not deadlock and which is comprehensible.

Place-transition Petri nets are an ideal representation for designing and modelling the interaction of concurrent (and distributed) processes. Occam is a high level real time parallel language designed to execute on one or a network of transputers. Transputers are processing, memory and communication building blocks, and, together with occam, are shown to be suitable for controlling and communicating the control as the DCS in FMCs.

The methodology developed in this thesis adopts the mathematically based tools of Petri nets, occam and transputers, and, by exploiting their structural similarities, incorporates them in a steps and tasks to improve the development of correct, reliable and hence safe occam code. The four steps: identify concurrent and sequential operations, produce Petri net graphs for all controllers, combine controller Petri net graphs and translate Petri net graphs into occam; are structured around three core goals: Petri net/occam equivalence, comprehensibility and pro-activity; which are manifest in four strategies: output-work-backwards, concurrent and sequential actions, structuralise and modularise, and deadlock avoidance.

The methodology assists in all stages of the software development life cycle, and is applicable to small DCSs such as an FMC. The methodology begins by assisting in the creation of DCS requirements from the manufacturing requirements of the FMC, and guides the user to the production of dependable occam code. Petri nets allow the requirements to be specified as they are created, and the methodology's imposed restrictions enable the final Petri net design to be translated directly into occam. Thus the mathematics behind the formal tools is hidden from the user, which should be attractive to industry.

The methodology is successfully applied to the example FMC, and occam code to simulate the FMC is produced. Due to the novelty of the research, many suggestions for further work are given.

# Contents

| 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 Research Applicability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                      |

| 1.2 Traditional Production Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                      |

| 1.3 Flexible Production                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2                                                                                                                                      |

| 1.4 Shortening Order-to-delivery and Manufacturing Lead Time                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                                                                                                                                      |

| 1.5 Shortening Time-to-market and Product Development Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4                                                                                                                                      |

| 1.6 Integrated Flexible Production Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |

| 1.7 Fast Reconfiguration Requirement in FMSs                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6                                                                                                                                      |

| 1.8 The Research and Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7                                                                                                                                      |

| 2. The Flexible Manufacturing Cell and Its Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9                                                                                                                                      |

| 2.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

| 2.2 Flexibility and Cellular Manufacturing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |

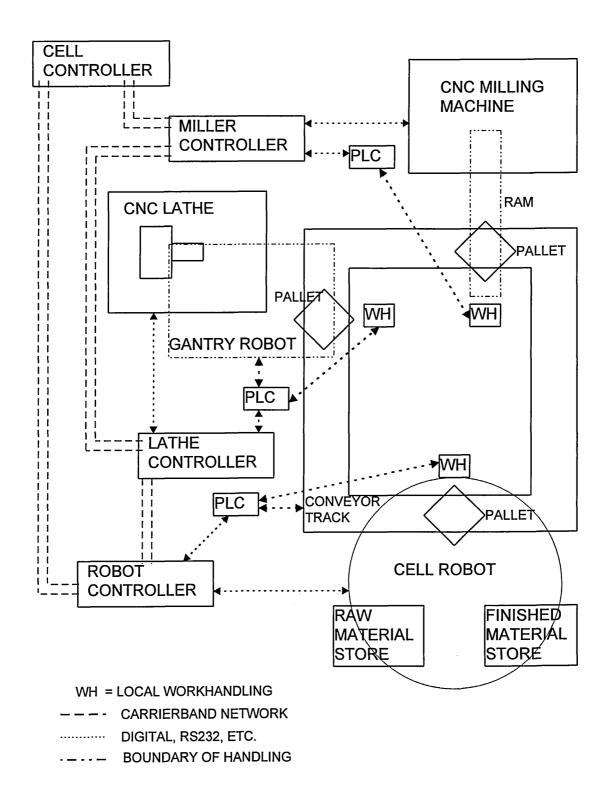

| 2.3 Description of Existing PC Based Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

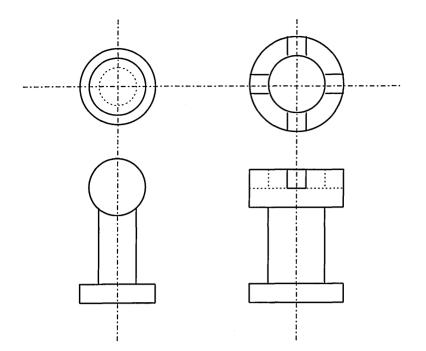

| 2.3.1 Choice of Component                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                                                                                                     |

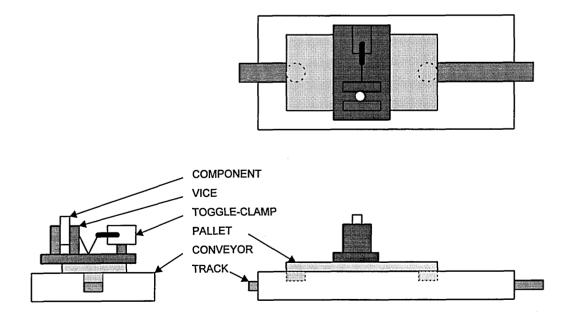

| 2.3.2 Conveyor Track                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |

| 2.3.3 Pallets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

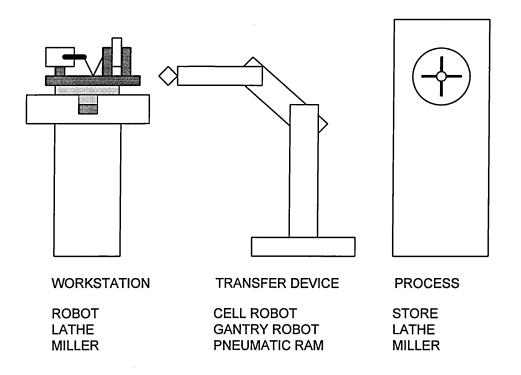

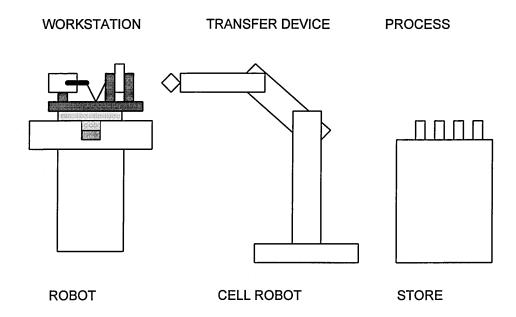

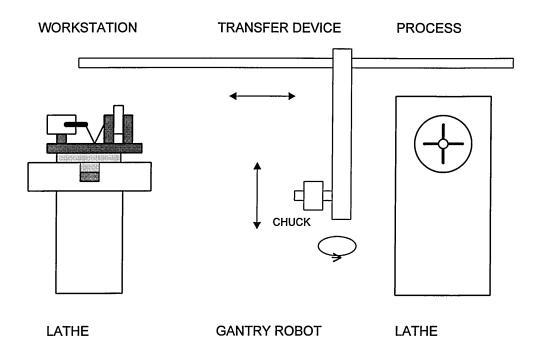

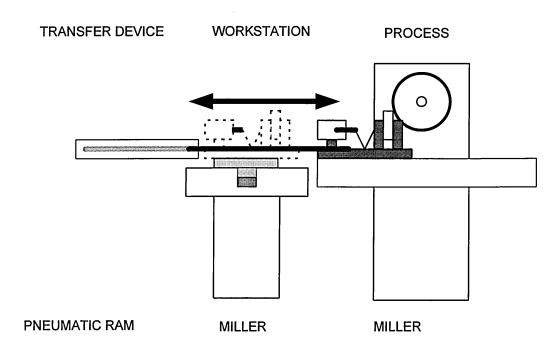

| 2.3.4 Transfer and Local Work Handling Equipment                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                        |

| 2.4 Control and Communication of Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                        |

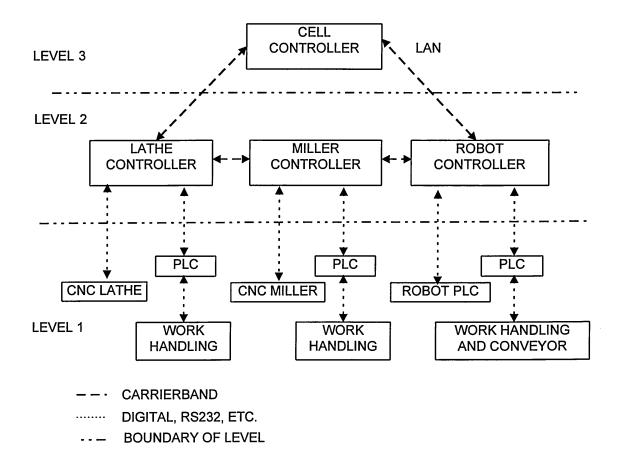

| 2.5 The Control of the Existing PC Based FMC                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21                                                                                                                                     |

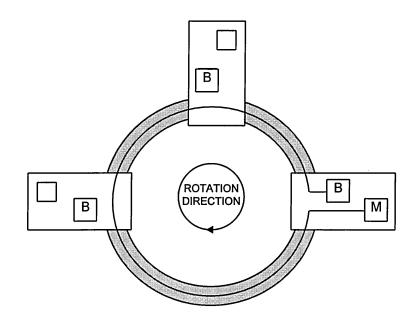

| 2.6 The Communication of the Existing FMC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                        |

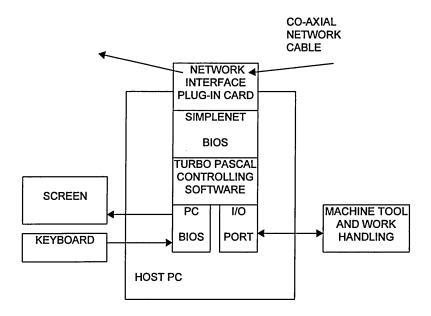

| 2.6.1 The LAN and PC Hardware and Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

| 2.6.2 LAN Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25                                                                                                                                     |

| 2.6.2 LAN Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27                                                                                                                                     |

| 2.7 Summary of Problems and Manufacturing Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27<br><i>29</i>                                                                                                                        |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li> <li>3. Tools and Techniques in Dependable Distributed Control</li> <li>3.1 Introduction</li> </ul>                                                                                                                                                                                                                                                                                                                                                   | 27<br><i>29</i><br>29                                                                                                                  |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br><i>29</i><br>29<br>29                                                                                                            |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br><i>29</i><br>29<br>29<br>29                                                                                                      |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>29<br>29<br>30                                                                                                       |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>29<br>29<br>30<br>32                                                                                                 |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>29<br>30<br>32<br>33                                                                                                 |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>30<br>32<br>33<br>34                                                                                                 |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>30<br>32<br>33<br>34<br>34                                                                                           |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>30<br>32<br>33<br>34<br>34<br>36<br>38                                                                               |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>30<br>32<br>33<br>34<br>34<br>36<br>38                                                                               |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li> <li>3. Tools and Techniques in Dependable Distributed Control.</li> <li>3.1 Introduction.</li> <li>3.2 Dependability.</li> <li>3.2.1 Software Engineering.</li> <li>3.2.2 Correctness.</li> <li>3.2.2.1 Validation and Verification</li> <li>3.2.3 Reliability.</li> <li>3.2.4 Safety</li> <li>3.2.4.1 Safety Standards</li> <li>3.2.4.2 Safety Integrity Level.</li> <li>3.2.4.3 Hazard Analysis.</li> <li>3.2.5 Software and Hardware</li> </ul>   | 27<br>29<br>29<br>29<br>30<br>32<br>33<br>34<br>34<br>36<br>38<br>38                                                                   |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li> <li>3. Tools and Techniques in Dependable Distributed Control.</li> <li>3.1 Introduction.</li> <li>3.2 Dependability.</li> <li>3.2.1 Software Engineering.</li> <li>3.2.2 Correctness.</li> <li>3.2.2.1 Validation and Verification</li> <li>3.2.3 Reliability.</li> <li>3.2.4 Safety</li> <li>3.2.4.1 Safety Standards.</li> <li>3.2.4.2 Safety Integrity Level.</li> <li>3.2.4.3 Hazard Analysis.</li> <li>3.2.5 Software and Hardware.</li> </ul> | 27<br>29<br>29<br>29<br>30<br>32<br>33<br>34<br>36<br>38<br>38<br>38                                                                   |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li> <li>3. Tools and Techniques in Dependable Distributed Control.</li> <li>3.1 Introduction.</li> <li>3.2 Dependability.</li> <li>3.2.1 Software Engineering.</li> <li>3.2.2 Correctness.</li> <li>3.2.2.1 Validation and Verification</li> <li>3.2.3 Reliability.</li> <li>3.2.4 Safety</li> <li>3.2.4.1 Safety Standards</li> <li>3.2.4.2 Safety Integrity Level.</li> <li>3.2.4.3 Hazard Analysis.</li> <li>3.2.5 Software and Hardware</li> </ul>   | 27<br>29<br>29<br>29<br>29<br>30<br>32<br>33<br>34<br>34<br>34<br>38<br>38<br>38<br>40<br>40                                           |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li> <li>3. Tools and Techniques in Dependable Distributed Control.</li> <li>3.1 Introduction.</li> <li>3.2 Dependability.</li> <li>3.2.1 Software Engineering.</li> <li>3.2.2 Correctness.</li> <li>3.2.2.1 Validation and Verification</li> <li>3.2.3 Reliability.</li> <li>3.2.4 Safety</li></ul>                                                                                                                                                      | 27<br>29<br>29<br>29<br>30<br>32<br>33<br>34<br>34<br>36<br>38<br>38<br>40<br>40                                                       |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li> <li>3. Tools and Techniques in Dependable Distributed Control.</li> <li>3.1 Introduction.</li> <li>3.2 Dependability.</li> <li>3.2.1 Software Engineering.</li> <li>3.2.2 Correctness.</li> <li>3.2.2.1 Validation and Verification</li> <li>3.2.3 Reliability.</li> <li>3.2.4 Safety</li></ul>                                                                                                                                                      | 27<br>29<br>29<br>29<br>30<br>32<br>33<br>34<br>33<br>34<br>36<br>38<br>40<br>40<br>40<br>40                                           |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>29<br>30<br>32<br>33<br>34<br>33<br>34<br>36<br>38<br>38<br>40<br>40<br>40<br>42                                     |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>30<br>32<br>33<br>34<br>33<br>34<br>38<br>38<br>40<br>40<br>40<br>42<br>42                                           |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>30<br>32<br>33<br>34<br>33<br>34<br>36<br>38<br>38<br>40<br>40<br>40<br>42<br>42<br>43                               |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li> <li>3. Tools and Techniques in Dependable Distributed Control.</li> <li>3.1 Introduction.</li> <li>3.2 Dependability</li></ul>                                                                                                                                                                                                                                                                                                                       | 27<br>29<br>29<br>29<br>29<br>30<br>32<br>33<br>34<br>36<br>33<br>34<br>36<br>38<br>38<br>38<br>40<br>40<br>42<br>42<br>42<br>43<br>43 |

| <ul> <li>2.7 Summary of Problems and Manufacturing Requirements</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27<br>29<br>29<br>29<br>30<br>32<br>33<br>34<br>33<br>34<br>36<br>38<br>40<br>40<br>40<br>40<br>42<br>43<br>445<br>45                  |

| 3.3.2.3 High Level Petri Nets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.3.2.4 State Transition Diagrams (STDs)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.4 Occam and its Dependability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.4.1 The Occam Language and Programming Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <del>4</del> 0<br>//                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.4.2 The Occam Toolset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.4.3 Occam Safety                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.4.4 Deadlock Correctness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5 A Comparison of Transputers and other Shop Floor Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

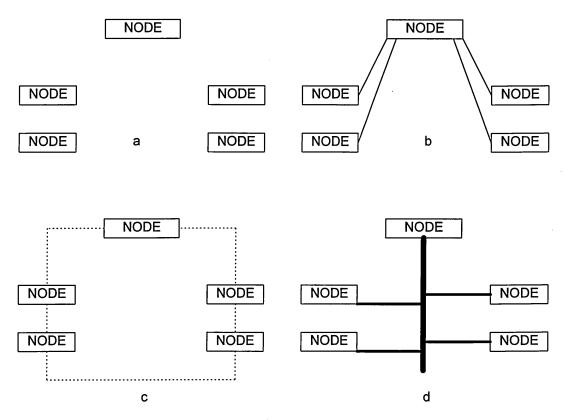

| 3.5.1 Distributed Control Systems and Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.5.2 Models of Communication and Synchronisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.3 Communication Standards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.4 Shop-floor Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.5 The Transputer and Occam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.5.5.1 Transputer Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.5.2 Transputer Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.5.3 Transputer Communication Reliability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.5.5.4 Occam and Transputer Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.5.5 Booting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.5.6 Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

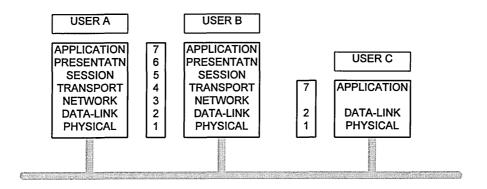

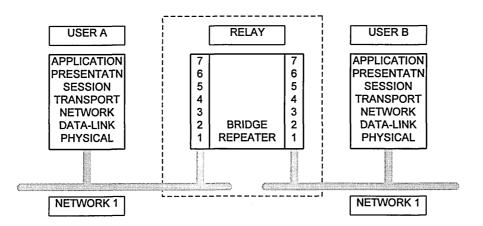

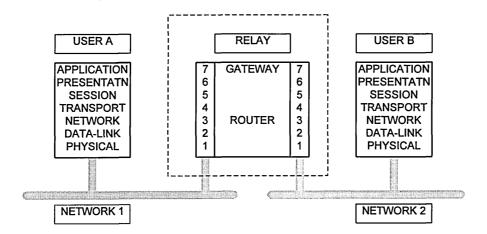

| 3.5.5.7 The Transputer and the OSI 7 Layer Reference Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.6 FIP (Factory Instrumentation Protocol)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

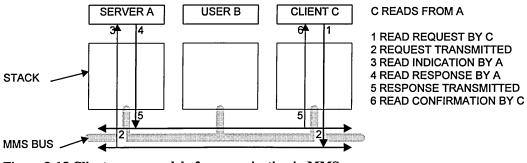

| 3.5.7 Mini-Map with MMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.8 9Tiles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.5.9 A Comparison Shop-floor Control Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

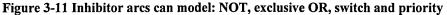

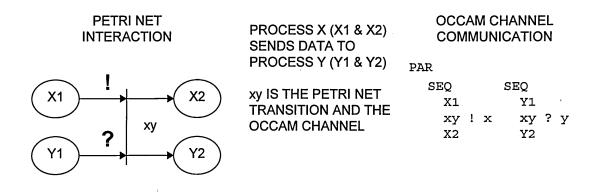

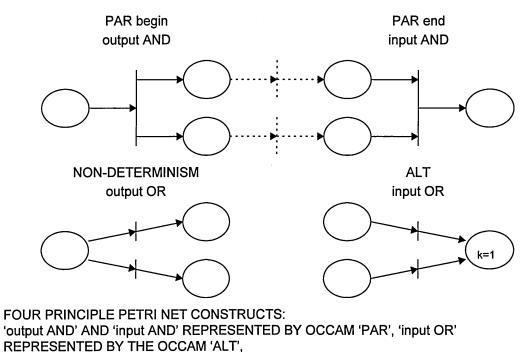

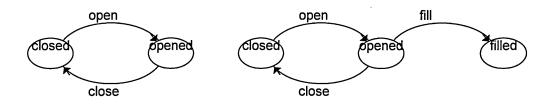

| 3.6 Similarities between Petri Nets and Occam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

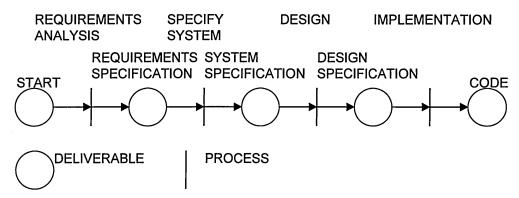

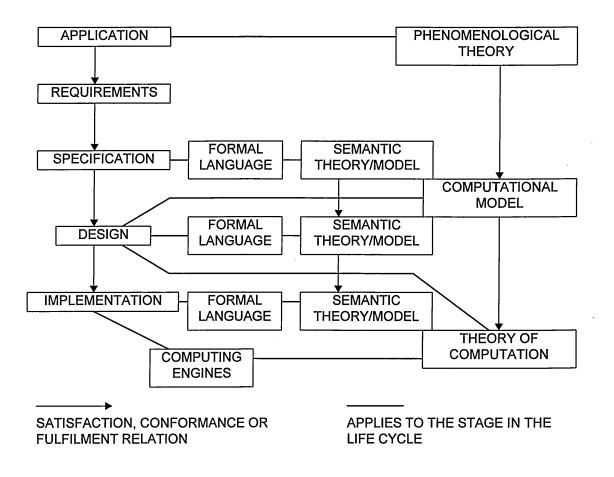

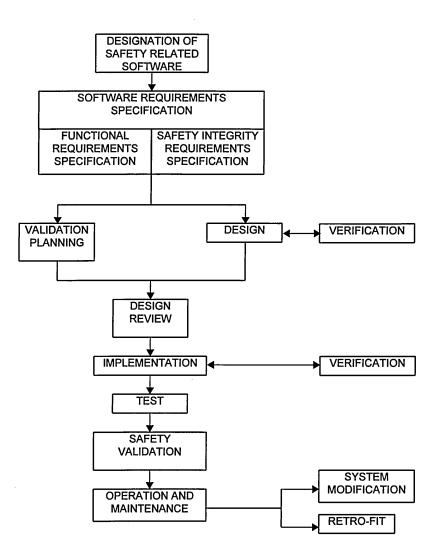

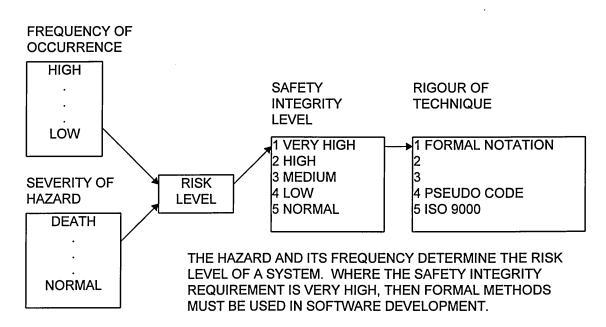

| 4. Distributed Control Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |