Research and development of CdS/CdTe solar cells incorporating ZnTe layers.

FAUZI, Fijay Bin.

Available from the Sheffield Hallam University Research Archive (SHURA) at:

http://shura.shu.ac.uk/19643/

# A Sheffield Hallam University thesis

This thesis is protected by copyright which belongs to the author.

The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

Please visit http://shura.shu.ac.uk/19643/ and http://shura.shu.ac.uk/information.html for further details about copyright and re-use permissions.

12011

Adsetts Centre, City Campus Sheffield S1 1WD

102 056 919 0

Sheffield Hallam University Learning and Information Services Adsetts Centre, City Campus Sheffield S1 1WD

REFERENCE

ProQuest Number: 10694524

#### All rights reserved

#### INFORMATION TO ALL USERS

The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

#### ProQuest 10694524

Published by ProQuest LLC (2017). Copyright of the Dissertation is held by the Author.

All rights reserved.

This work is protected against unauthorized copying under Title 17, United States Code

Microform Edition © ProQuest LLC.

ProQuest LLC. 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106 – 1346

# Research and Development of CdS/CdTe solar cells incorporating ZnTe layers

Fijay Bin Fauzi

A thesis submitted in partial fulfillment of the requirements of Sheffield Hallam University for the degree of Doctor of Philosophy

**July 2015**

# Declaration

I hereby declare that this thesis is my own work and it has not been submitted elsewhere for any award.

#### **Abstract**

This thesis presents experimental work and analysis in research and development of low-cost thin film solar cells. In this work, three semiconducting materials were studied. These semiconducting materials are from group II-VI or also known as 'two-sixers' from periodic table. The semiconductors are cadmium sulfide (CdS), cadmium telluride (CdTe) and zinc telluride (ZnTe).

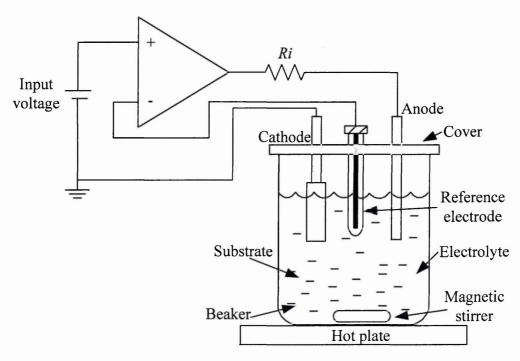

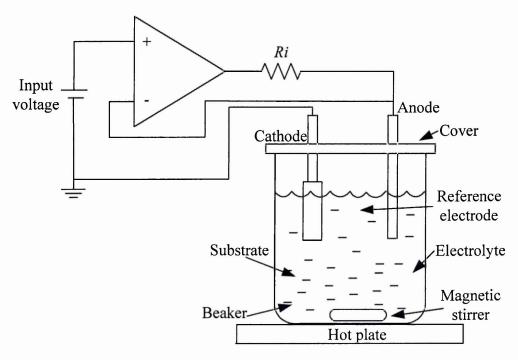

All of these layers were obtained by growing them using electrodeposition in aqueous solutions. In this project, electrodeposition using 2-electrode system was employed to deposit all of the semiconductors. The decision was taken to avoid contamination that might be happening due to the leakage of foreign ions such as K<sup>+</sup> and Ag<sup>+</sup> contained in the reference electrode into the electrolyte.

To help in optimizing the semiconducting layers, three characterization techniques were used frequently. These techniques are optical absorption, x-ray diffraction (XRD) and photoelectrochemical (PEC) cell measurements. These techniques were used to study the optical, structural and electrical conductivity type of the electrodeposited layers respectively. After optimizing the layers using the above three techniques (optical absorption, XRD and PEC), other advance analytical techniques (SEM, XRF, D.C. conductivity measurement, photoluminescence and UPS) were used to fully characterize the materials. This information was also used to further optimize the material layers.

At the later stage of this project, research was concentrated on fabricating and assessing solar cell devices. Initial devices fabricated had glass/FTO/CdS/CdTe/Au structure. Current-voltage (I-V) measurement was employed to assess the performance of solar cell devices by measuring the open circuit voltage ( $V_{oc}$ ), short circuit current density ( $J_{sc}$ ), fill factor (FF) and conversion efficiency ( $\eta$ ). The highest efficiency obtained from this solar cell structure was 10.1%. However, this structure had low fill factors in the range of 0.25 to 0.4.

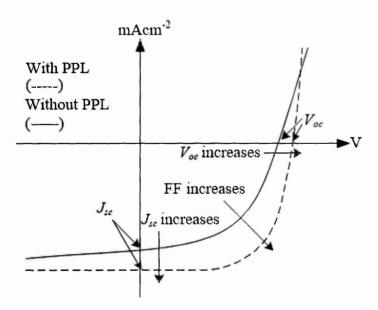

To solve this problem, an insulating layer was incorporated into the device to create metal-insulator-semiconductor type structures. Results have shown that by electrodepositing insulating p-type ZnTe layers on top of CdTe, the fill factor can be improved.

# Acknowledgement

In the name of Allah, the most Beneficent, the most Merciful. Peace and blessing of Allah be upon to His noble prophet Muhammad (Sallallahu Alaihi Wassallam).

I would like to take this opportunity to thank my Director of Studies, Professor I.M. Dharmadasa for his excellent guidance and tireless motivation. I also appreciate the contribution made by my second supervisor Dr. Aseel Hassan in helping me to complete this thesis. I remain indebted to the staff of Materials and Engineering Research Institute (MERI) especially Prof Douglas Cleaver, Deeba Zahoor, Vinay Patel, Bob Burton, Yashodhan Purandare, Vikas Kumar, Corrie Houton, Gillian Hill and others due to their sincerity of helping me in completing this research programme.

To my colleagues, D.G. Diso, O.K. Echendu, Ajith Weerasinghe, Hussein Salim, Nor Azlian Manaf, Muhammad Madugu, Olajide Olusola and Ayotunde Ojo, I would like to thank them for their helping hands and knowledge sharing.

I am indebted to the collaborators who have helped me completing the selective experiments involved in this project. Firstly, to Prof M. Dergacheva from Institute of Organic Catalyst & Electrochemistry, Kazakhstan. Mr. Leon Bowen and Mr. Matt Murray from Durham University and University of Leeds, respectively. Mr Ali Abbas from Loughborough University and lastly Prof Thad Druffel, R. Dharmadasa and their research group from University of Louisville, USA.

To my parents, Fauzi Hassan and Wan Nah Wan Ismail, I thank them for their efforts and sacrifices in raising me up and giving me love, care, support, prayer and much more. Honestly, I can't thank them enough. To my in-law parents, Abu Bakar Sudin and Che Nolia Mat Isa, I really appreciate their support and prayer to me and my family.

For my lovely wife Nurbazlin Abu Bakar, I would like to thank her for taking care of my children, Aqil Thaqif, Aiman Uqail and Ammar Muqrie. I sincerely appreciate her efforts and sacrifices in supporting me going through difficult times.

Last but not least, I would like to thank my sponsors, Ministry of Education, Malaysia and also Universiti of Malaysia, Perlis for their assistance and financial support to me and my family.

# **List of Publications**

## **Journal Publications:**

- 1. **F Fauzi**, D G Diso, O K Echendu, V Patel, Y Purandare, R Burton and I M Dharmadasa, "Development of ZnTe layers using an electrochemical technique for applications in thin-film solar cells", Semicond. Sci. Technol. **28** (2013) 045005 (10pp).

- 2. O K Echendu, A R Weerasinghe, D G Diso, F Fauzi and I M Dharmadasa, "Characterization of n-Type and p-Type ZnS Thin Layers Grown by an Electrochemical Method", Journal of Electronic Materials 42 (2013) April 2013, Volume 42, Issue 4, pp 692-700.

- 3. D G Diso, **F Fauzi**, O K Echendu, A R Weerasinghe and I M Dharmadasa, "Electrodeposition and characterisation of ZnTe layers for application in CdTe based multi-layer graded bandgap solar cells", Journal of Physics: Conference Series 286 (2011) 012040.

- 4. O K Echendu, A R Weerasinghe, **F Fauzi** and I M Dharmadasa, "High short-circuit current density CdTe solar cells using all-electrodeposited semiconductors", Thin Solid Films 556 (2014) pp 529-534.

- 5. N. A. Abdul-Manaf, O. K. Echendu, F. Fauzi, L. Bowen and I. M. Dharmadasa, "Development of polyaniline using electrochemical technique for plugging pinholes in cadmium sulfide/ cadmium telluride solar cells", Journal of Electronic Materials 43 (2014) pp 4003-4010.

- 6. I.M. Dharmadasa, O.K. Echendu, F. Fauzi, H.I. Salim, N.A. Abdul-Manaf, J.B. Jasinski, A. Sherehiy and G. Sumanasekera, "Study of Fermi level movement during CdCl2 treatment of CdTe thin films using Ultra-violet Photoemission Spectroscopy". (Submitted to Materials Chemistry and Physics on 26/09/2014).

- 7. D.G. Diso, **F. Fauzi**, O.K. Echendu and I.M. Dharmadasa, "Optimisation of CdTe Electrodeposition Voltage for Development of CdS/CdTe solar cells", (submitted to Coatings on 13/10/2014).

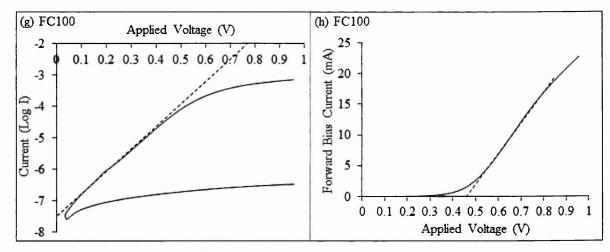

- 8. I. M. Dharmadasa, O. K. Echendu, F. Fauzi, N. A. Abdul Manaf, H. I. Salim, T. Druffel, R. Dharmadasa and B. Lavery, "Effects of CdCl2 treatment on deep levels in CdTe and their implications on thin film solar cells; A comprehensive photoluminescence study". (Submitted to Coatings on 15/12/5014).

#### **Conference Publications:**

- 1. H M Yates, D W Sheel, I M Dharmadasa, O K Echendu and **F Fauzi**, "The effects of TCO properties on all electrodeposited CdS/CdTe PV solar cells", PVSAT-9, Swansea University, 10-12 April 2013.

- 2. O K Echendu, A R Weerasinghe, D G Diso, **F Fauzi** and I M Dharmadasa, "n-CdTe based multi-layer graded bandgap solar cell using all electrodeposited semiconductors", PVSAT-9, Swansea University, 10-12 April 2013.

- 3. I M Dharmadasa, O K Echendu, R Dharmadasa and **F Fauzi**, "Distortion observed in current-voltage characteristics of photovoltaic solar cells", 27th EU PVSEC, Frankfurt, 24-28 September 2012.

- 4. **F. Fauzi**, N.A.A Manaf, O.K. Echendu and I M Dharmadasa, "Electrochemical deposition of organic and inorganic pin-hole plugging layers for CdS/CdTe solar cells" Solar Asia 2013, University of Malaya, 22-24 August 2013.

- 5. O K Echendu, **F Fauzi**, L Bowen, and I M Dharmadasa, "All electrodeposited, multilayer graded bandgap solar cells using II-VI semiconductors" 28th EU PVSEC, Paris, 30 September 4 October 2013.

- 6. N. A. Abdul-Manaf, O. K. Echendu, **F. Fauzi**, L. Bowen and I. M. Dharmadasa, "Electrodeposition and Characterization of polyaniline to develop organic/inorganic hybrid solarc cells based on cadmium telluride", 28th EU PVSEC, Paris, 30 September 4 October 2013.

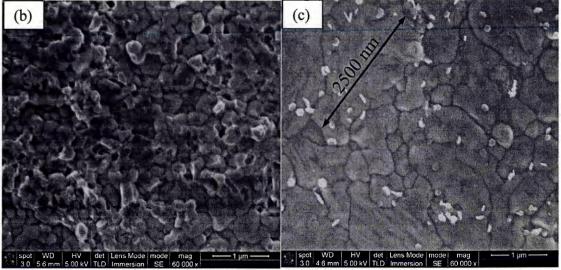

- 7. O. K. Echendu, **F. Fauzi** and I. M. Dharmadasa, "Effect of (CdCl<sub>2</sub>+CdF<sub>2</sub>) treatment on the conversion efficiency of CdS/CdTe solar cell", PVSAT-10, Loughborough University, 23-25 April 2013.

# **Table of Contents**

| Decl | laration                                                       | ii   |  |

|------|----------------------------------------------------------------|------|--|

| Abst | tract                                                          | iii  |  |

| Ackı | nowledgement                                                   | iv   |  |

| List | List of publications                                           |      |  |

| Tabl | le of contents                                                 | viii |  |

| Cha  | pter 1: Introduction                                           | 1    |  |

| 1.1  | Global needs for renewable energies                            | 1    |  |

| 1.2  | The sources of renewable energies                              | 2    |  |

|      | 1.2.1 Wind energy                                              | 2    |  |

|      | 1.2.2 Geothermal energy                                        | 5    |  |

|      | 1.2.3 Hydroelectricity                                         | . 6  |  |

|      | 1.2.4 Tidal energy                                             | 8    |  |

|      | 1.2.5 Ocean water column (wave energy)                         | 9    |  |

|      | 1.2.6 Biomass energy                                           | 10   |  |

|      | 1.2.6.1 Anaerobic digestion                                    | 11   |  |

|      | 1.2.6.2 Gasification                                           | 12   |  |

|      | 1.2.7 Solar energy                                             | 14   |  |

|      | 1.2.7.1 Solar Thermal conversion (Concentrated Solar Tower)    | 16   |  |

|      | 1.2.7.2 Photovoltaic conversion                                | 17   |  |

| 1.3  | Aims and objectives                                            |      |  |

| 1.4  | Summary                                                        | 21   |  |

| 1.5  | References                                                     | 22   |  |

| Chap | pter 2: Introduction to solar energy materials and solar cells | 25   |  |

| 2.1  | Introduction                                                   |      |  |

| 2.2  | Solar energy materials                                         |      |  |

|      | 2.2.1 Intrinsic and extrinsic materials                                | 26 |  |

|------|------------------------------------------------------------------------|----|--|

| 2.3  | Solar cells interfaces                                                 |    |  |

|      | 2.3.1 p-n junctions                                                    | 30 |  |

|      | 2.3.2 p-i-n junctions                                                  | 34 |  |

|      | 2.3.3 Hetero-junctions                                                 | 34 |  |

|      | 2.3.4 Graded bandgap multilayer devices                                | 35 |  |

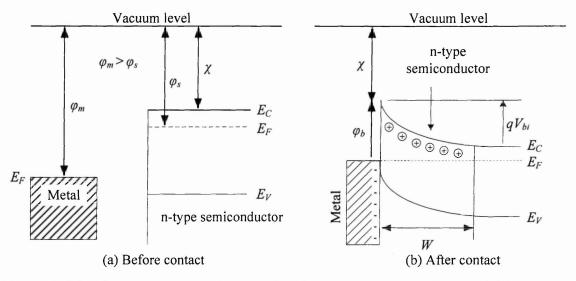

|      | 2.3.5 Metal-semiconductor (or Schottky) contact                        | 38 |  |

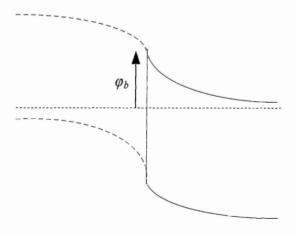

|      | 2.3.6 Metal-insulator-semiconductor (MIS) contact                      | 39 |  |

| 2.4  | Photovoltaic action                                                    | 40 |  |

| 2.5  | Role of defects and impurities in carrier generation and recombination | 44 |  |

| 2.6  | Summary                                                                |    |  |

| 2.7  | References                                                             | 47 |  |

|      |                                                                        |    |  |

| Chaj | pter 3: Photovoltaic technologies                                      | 49 |  |

|      |                                                                        |    |  |

| 3.1  | A brief history of photovoltaic research and development               | 49 |  |

| 3.2  | Types of solar cells                                                   | 50 |  |

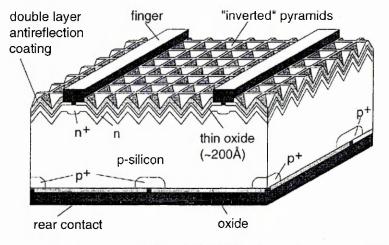

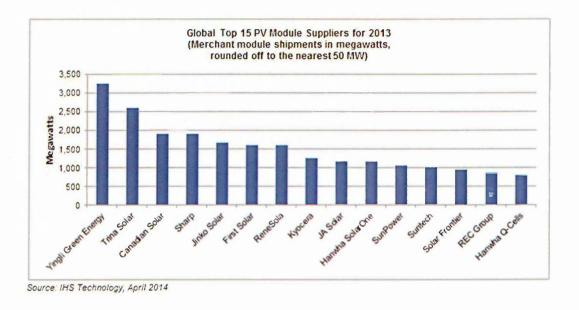

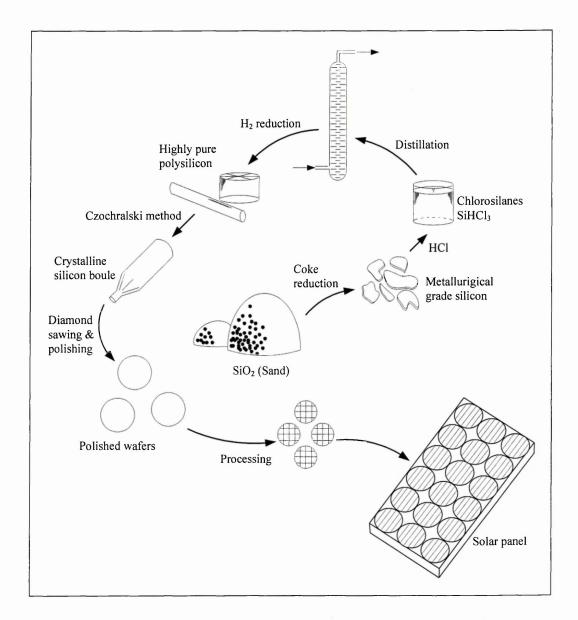

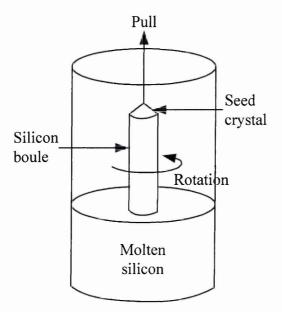

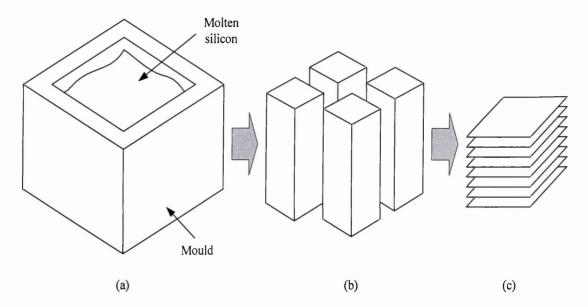

|      | 3.2.1 Silicon solar cells                                              | 50 |  |

|      | (a) Monocrystalline silicon                                            | 53 |  |

|      | (b) Multicrystalline silicon                                           | 56 |  |

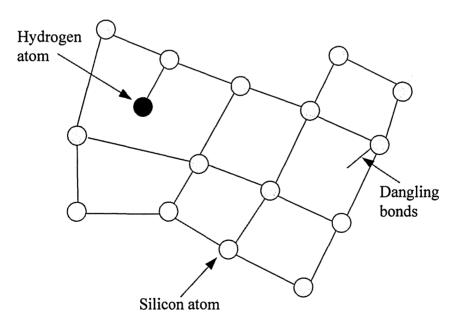

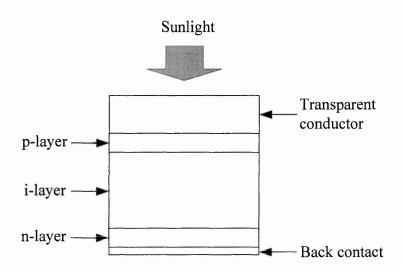

|      | (c) Amorphous silicon                                                  | 57 |  |

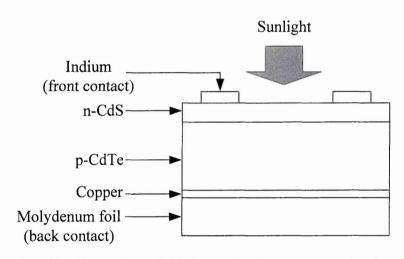

|      | 3.2.2 Chalcogenide solar cells                                         | 58 |  |

|      | 3.2.3 III-V solar cells                                                | 63 |  |

|      | 3.2.4 Dye-sensitized solar cells                                       | 64 |  |

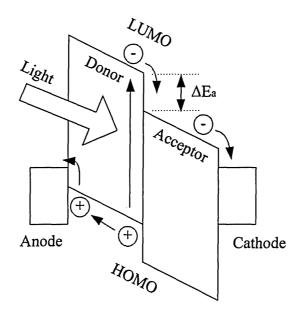

|      | 3.2.5 Organic solar cells                                              | 66 |  |

| 3.3  | Summary                                                                | 69 |  |

| 3.4  | References                                                             | 70 |  |

|      |                                                                        |    |  |

| Chap | pter 4: Deposition techniques of thin film semiconductors              | 74 |  |

|      |                                                                        |    |  |

| 4.0  | Introduction                                                           | 74 |  |

| 4.1  | Vapour phase deposition (VPD) techniques |                                                   | 74  |

|------|------------------------------------------|---------------------------------------------------|-----|

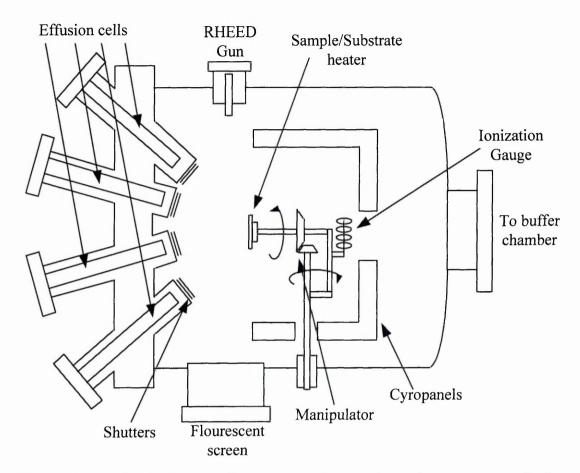

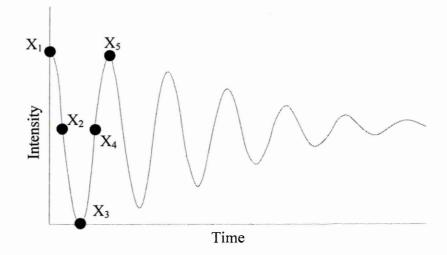

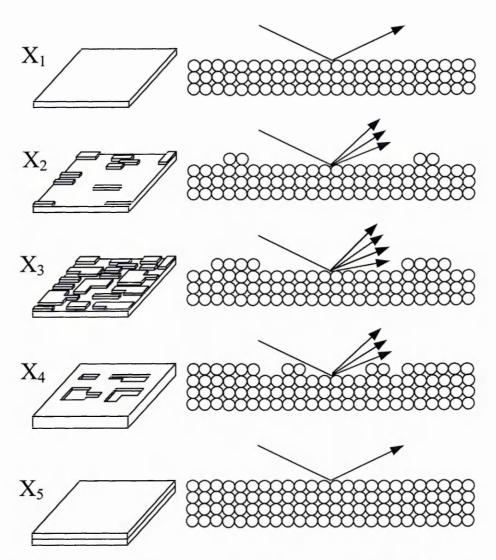

|      | 4.1.1                                    | Molecular beam epitaxy (MBE)                      | 74  |

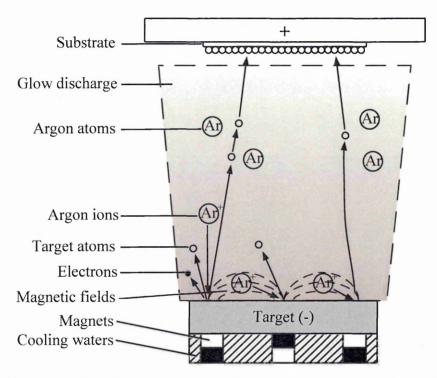

|      | 4.1.2                                    | Sputtering                                        | 74  |

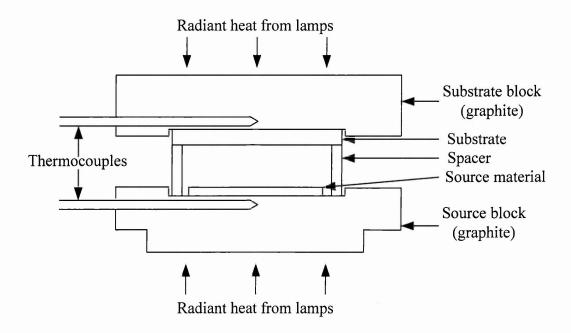

|      | 4.1.3                                    | Close space sublimation (CSS)                     | 78  |

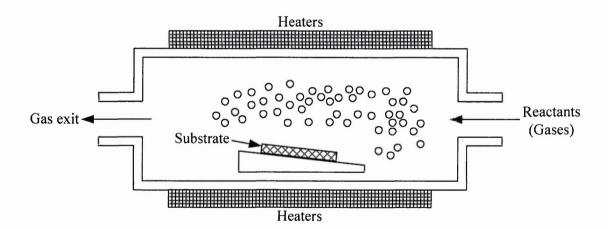

|      | 4.1.4                                    | Chemical vapour deposition (CVD)                  | 79  |

| 4.2  | Liqui                                    | d phase deposition (LPD) techniques               | 80  |

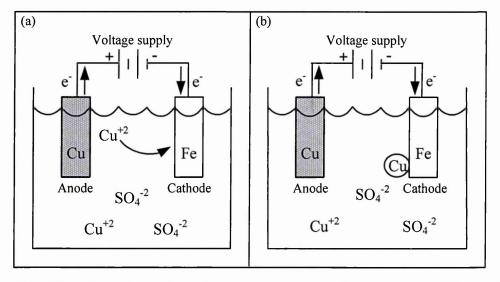

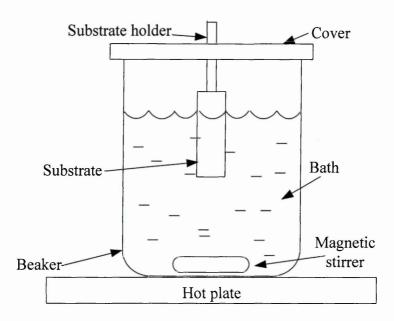

|      | 4.2.1                                    | Electrodeposition (ED)                            | 80  |

|      | 4.2.2                                    | Chemical bath deposition (CBD)                    | 84  |

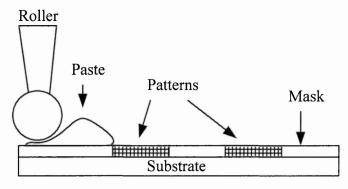

|      | 4.2.3                                    | Screen printing                                   | 85  |

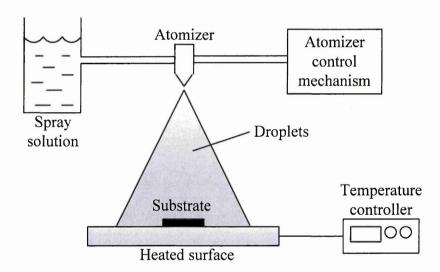

|      | 4.2.4                                    | Spray pyrolysis                                   | 86  |

| 4.3  | Summary                                  |                                                   | 87  |

| 4.4  | Refer                                    | ences                                             | 88  |

| Chaj | pter 5: N                                | Aaterials and devices characterisation techniques | 90  |

| 5.0  | Introd                                   | luction                                           | 90  |

| 5.1  | Materials characterisation techniques    |                                                   | 90  |

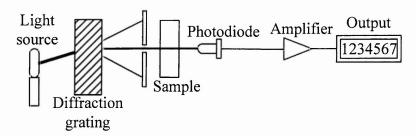

|      | 5.1.1                                    | Optical absorption                                | 90  |

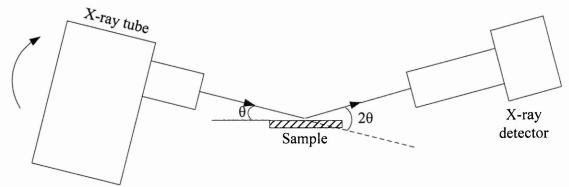

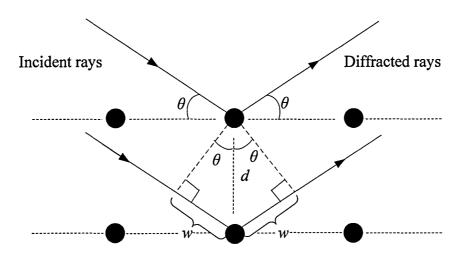

|      | 5.1.2                                    | X-ray diffraction (XRD)                           | 91  |

|      | 5.1.3                                    | Photoelectrochemical (PEC) cell measurement       | 93  |

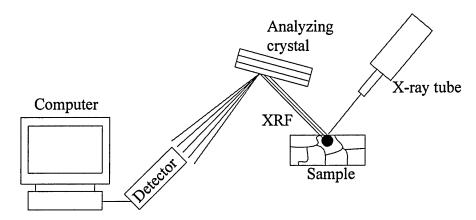

|      | 5.1.4                                    | X-ray fluorescence (XRF)                          | 95  |

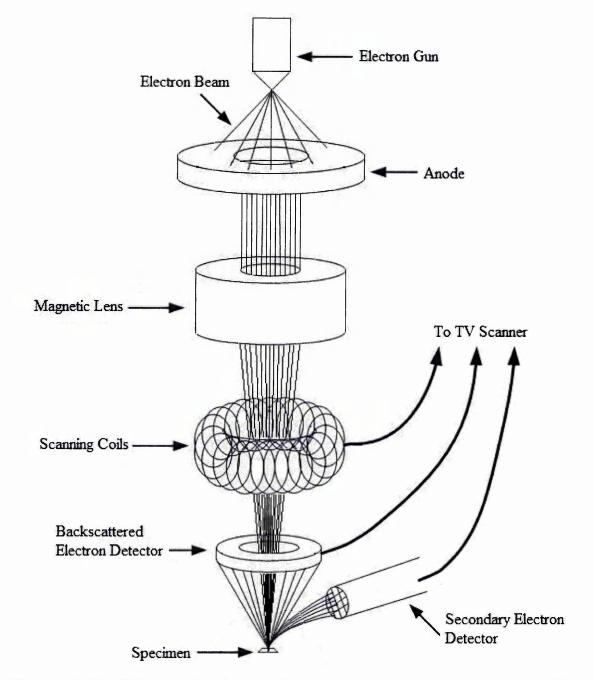

|      | 5.1.5                                    | Scanning electron microscopy (SEM)                | 97  |

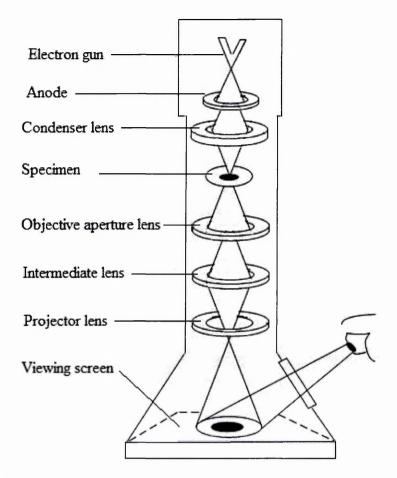

|      | 5.1.6                                    | Transmission electron microscopy (TEM)            | 98  |

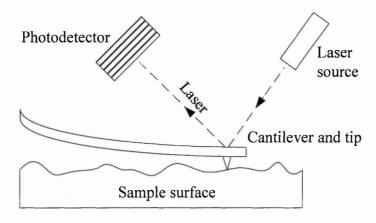

|      | 5.1.7                                    | Atomic force microscopy (AFM)                     | 99  |

|      | 5.1.8                                    | Photoluminescence (PL)                            | 100 |

|      | 5.1.9                                    | Ultraviolet photoelectron spectroscopy (UPS)      | 101 |

|      | 5.1.10                                   | DC electrical measurement                         | 102 |

| 5.2  | Device characterisation techniques       |                                                   | 104 |

|      | 5.2.1                                    | Current-voltage (I-V) measurement                 | 104 |

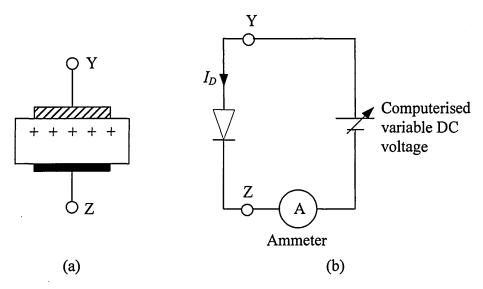

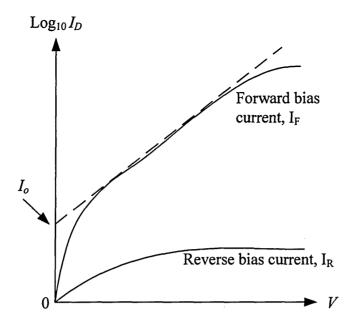

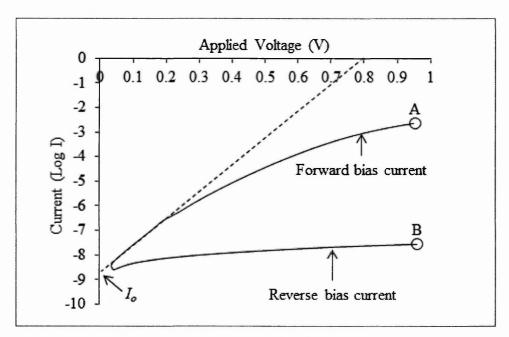

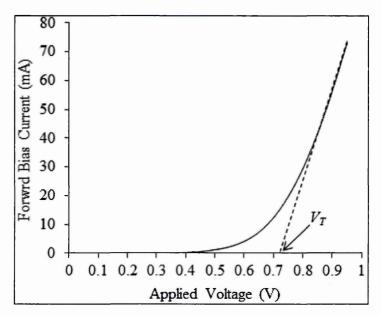

|      |                                          | 5.2.1.1 Measurement under dark condition          | 104 |

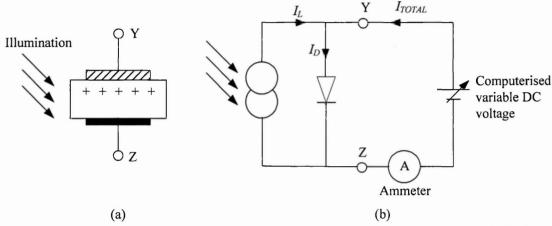

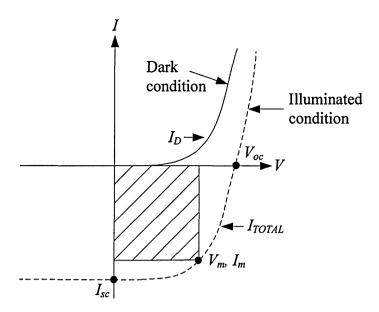

|      |                                          | 5.2.1.2 Measurement under illuminated condition   | 108 |

|      | 5.2.2                               | Capacitance-voltage (C-V) measurement                      | 112 |

|------|-------------------------------------|------------------------------------------------------------|-----|

| 5.3  | Summary                             |                                                            |     |

| 5.4  | Refer                               | ences                                                      | 110 |

|      |                                     |                                                            |     |

| Chaj | oter 6: I                           | Deposition and characterisation of window material; CdS    | 118 |

| 6.1  | Introd                              | luction                                                    | 118 |

| 6.2  | Preparation of CdS electrolyte bath |                                                            | 119 |

| 6.3  | Resul                               | Results and discussions                                    |     |

|      | 6.3.1                               | Voltammogram                                               | 119 |

|      | 6.3.2                               | Visual appearance                                          | 121 |

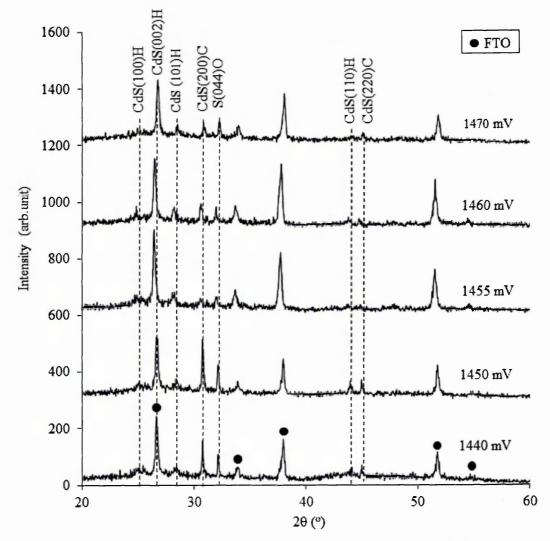

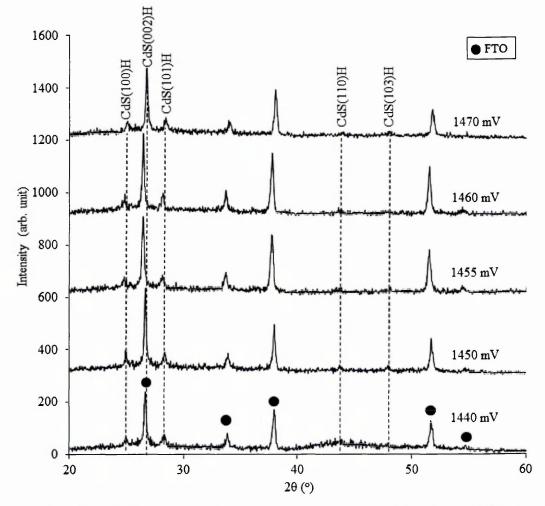

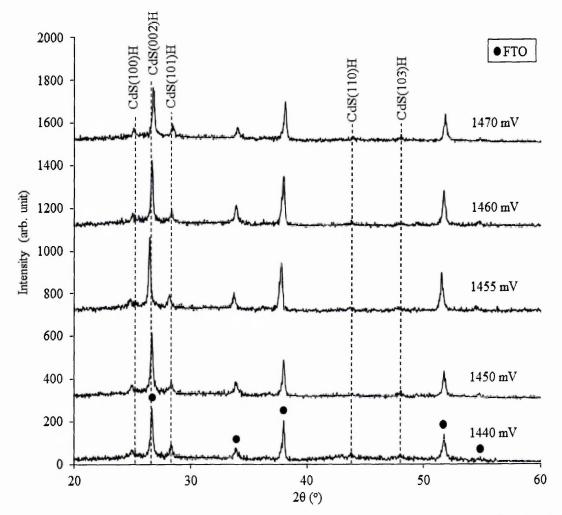

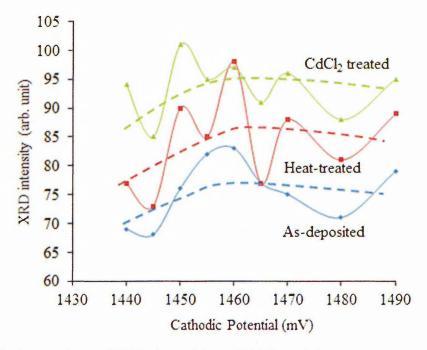

|      | 6.3.3                               | X-ray diffraction                                          | 122 |

|      | 6.3.4                               | Optical absorption spectroscopy                            | 128 |

|      | 6.3.5                               | X-ray fluorescence                                         | 132 |

|      | 6.3.6                               | Scanning electron microscope (SEM)                         | 133 |

|      | 6.3.7                               | Photoelectrochemical (PEC) cell measurement                | 136 |

|      | 6.3.8                               | D.C electrical measurement                                 | 137 |

| 6.4  | 4 Conclusion                        |                                                            | 138 |

| 6.5  | 5.5 References                      |                                                            |     |

| Chap | oter 7: D                           | Deposition and characterisation of absorber material; CdTe | 142 |

| 7.1  | Introd                              | uction                                                     | 142 |

| 7.2  | Prepar                              | ration of CdTe electrolyte bath                            | 143 |

| 7.3  | Results and discussions             |                                                            | 144 |

|      | 7.3.1                               | Voltammogram                                               | 144 |

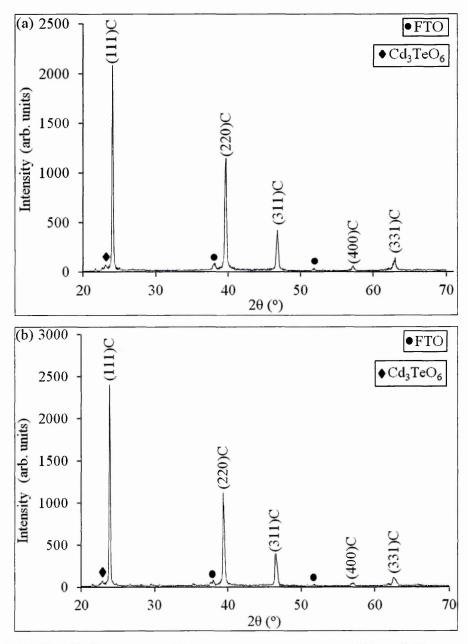

|      | 7.3.2                               | X-ray diffraction                                          | 146 |

|      | 7.3.3                               | Optical absorption spectroscopy                            | 155 |

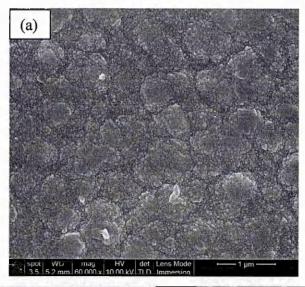

|      | 7.3.4                               | Scanning electron microscopy (SEM)                         | 158 |

|      | 7.3.5                               | Photoelectrochemical (PEC) cell measurements               | 161 |

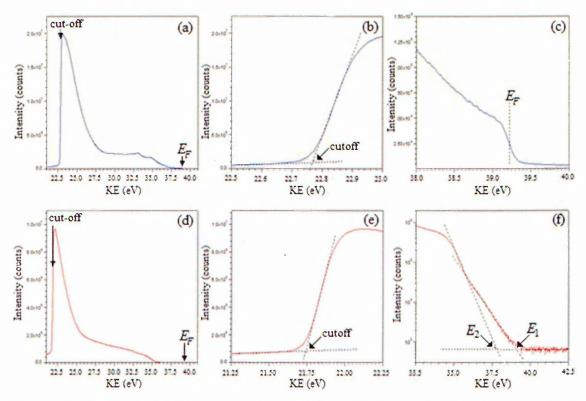

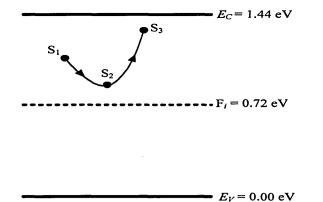

|      | 736                                 | Ultraviolet photoelectron spectroscopy (UPS)               | 163 |

|      | 7.3.7 D.C electrical conductivity n           | neasurements                     | 168 |

|------|-----------------------------------------------|----------------------------------|-----|

| 7.4  | Conclusion                                    |                                  |     |

| 7.5  | References                                    |                                  |     |

| Char | pter 8: Deposition and characterisati         | on of contacting materials InTo  | 173 |

| Cna  | pter 8: Deposition and characterisati         | on of contacting material, Zn 1e | 175 |

| 8.1  | Introduction                                  |                                  | 173 |

| 8.2  | 2 Preparation of ZnTe electrolyte bath        |                                  | 174 |

| 8.3  | Results and discussions                       |                                  | 174 |

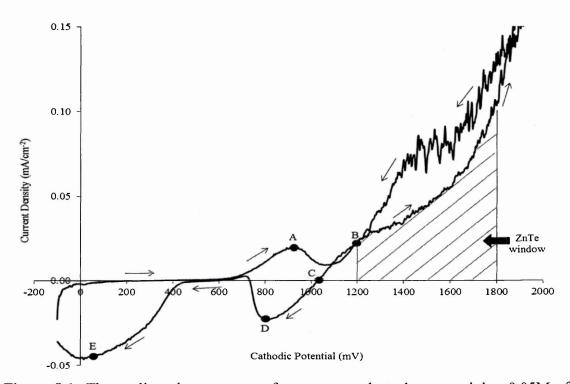

|      | 8.3.1 Voltammogram                            |                                  | 174 |

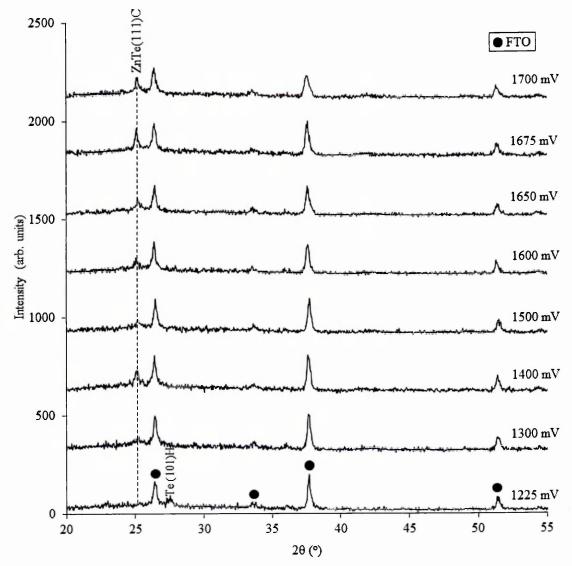

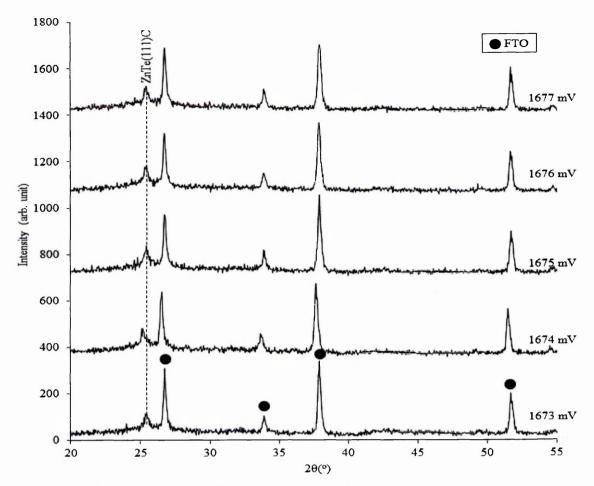

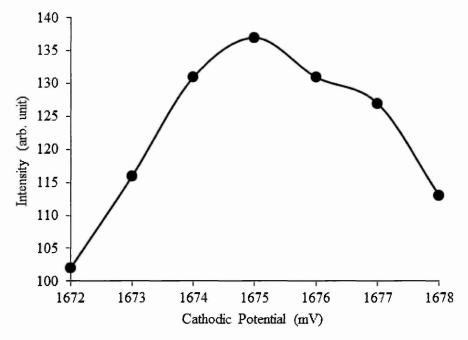

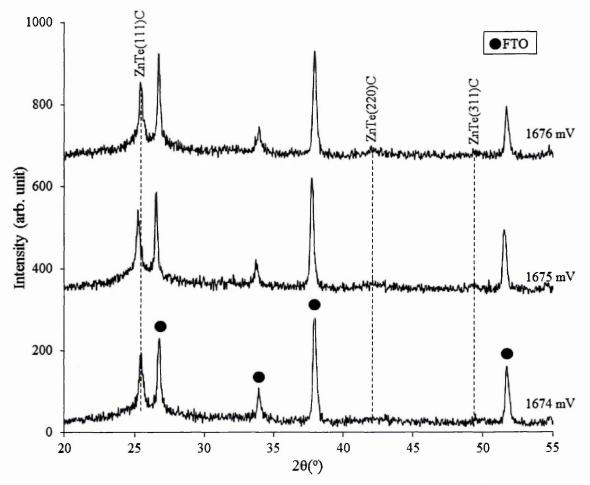

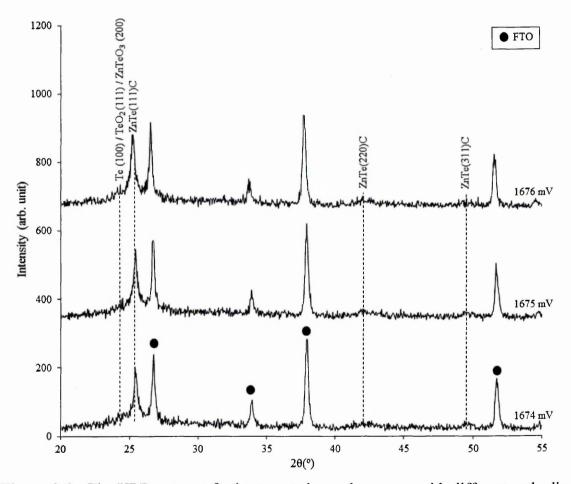

|      | 8.3.2 X-ray diffraction (XRD)                 |                                  | 176 |

|      | 8.3.3 Optical absorption spectrosco           | ору                              | 183 |

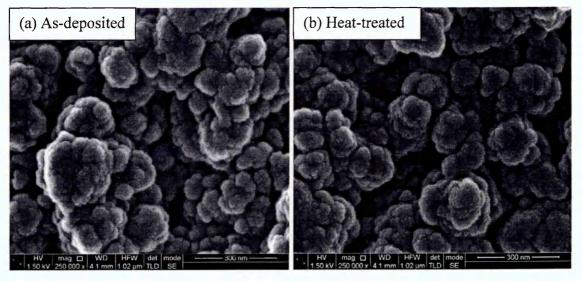

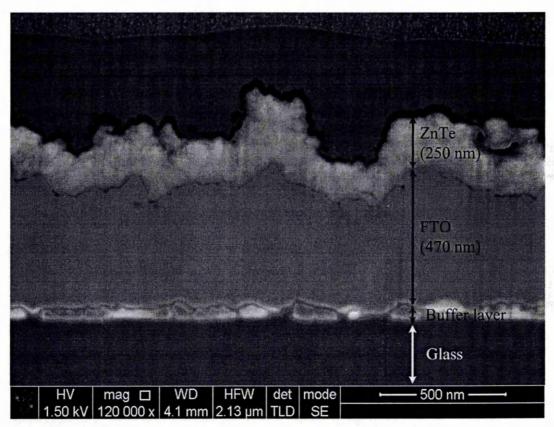

|      | 8.3.4 Scanning Electron Microscop             | py (SEM)                         | 185 |

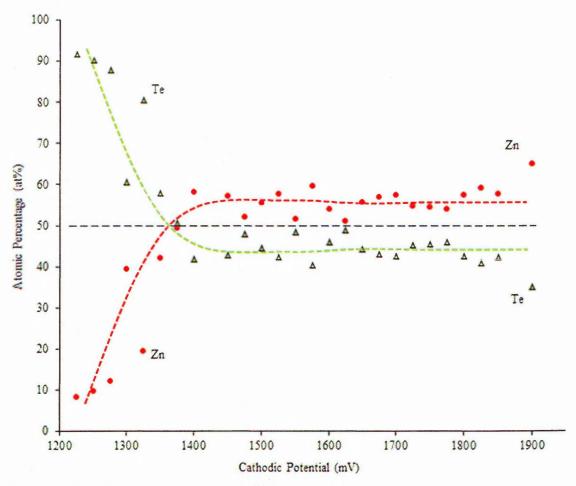

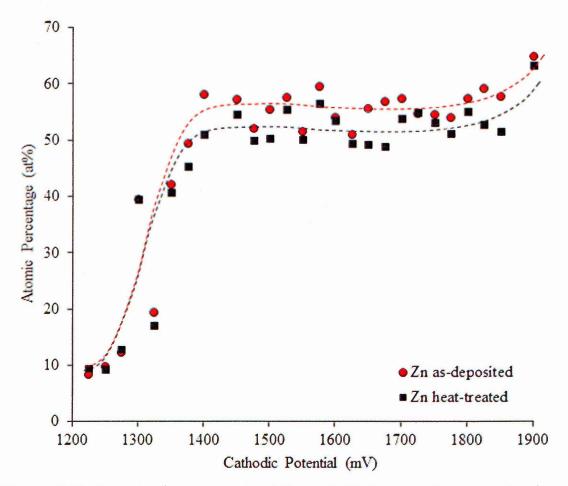

|      | 8.3.5 X-ray fluorescence (XRF)                |                                  | 187 |

|      | 8.3.6 Photoelectrochemical (PEC)              | cell measurements                | 190 |

|      | 8.3.7 D.C electrical conductivity n           | neasurements                     | 192 |

| 8.4  | Conclusion                                    |                                  | 193 |

| 8.5  | References                                    |                                  | 195 |

| Char | pter 9: CdS/CdTe solar cell devices fa        | phrication and characterization  | 196 |

| Спар | pter 3. Cus/Cure solar cen devices is         | torication and characterization  | 170 |

| 9.1  | Introduction                                  |                                  | 196 |

| 9.1  | Fabrication of glass/FTO/CdS/CdTe solar cells |                                  | 197 |

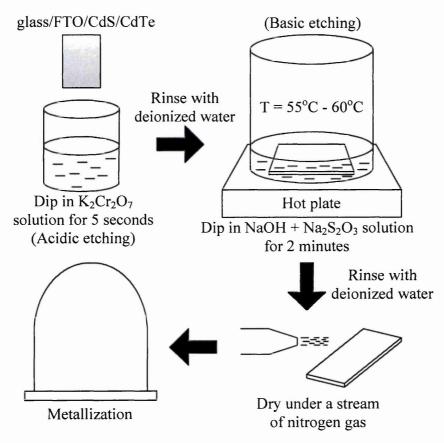

|      | 9.2.1 The etching process of CdTe             | surfaces                         | 199 |

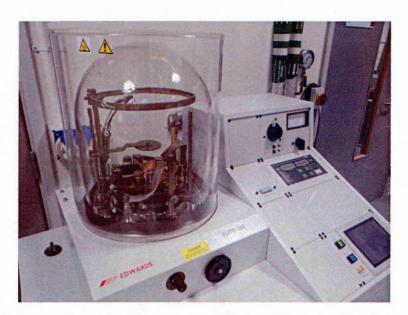

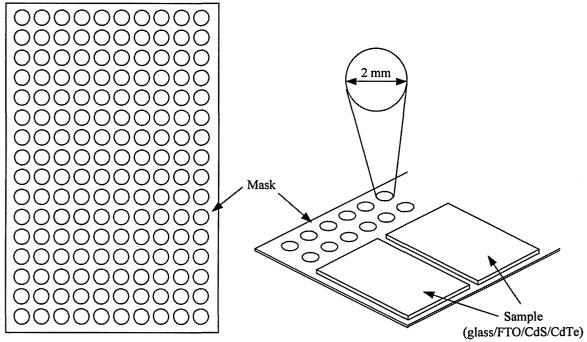

|      | 9.2.2 Deposition of metal back cor            | ntacts                           | 200 |

| 9.3  | Assessment of glass/FTO/CdS/CdTe              | Au solar cells                   | 203 |

|      | 9.3.1 Solar cells measurement und             | er illuminated condition         | 203 |

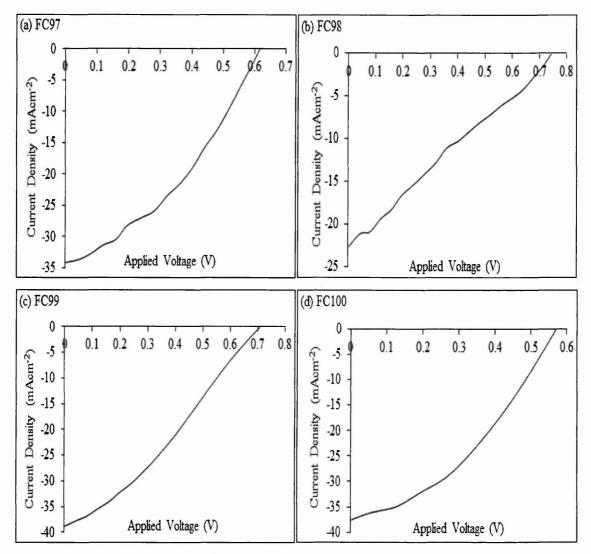

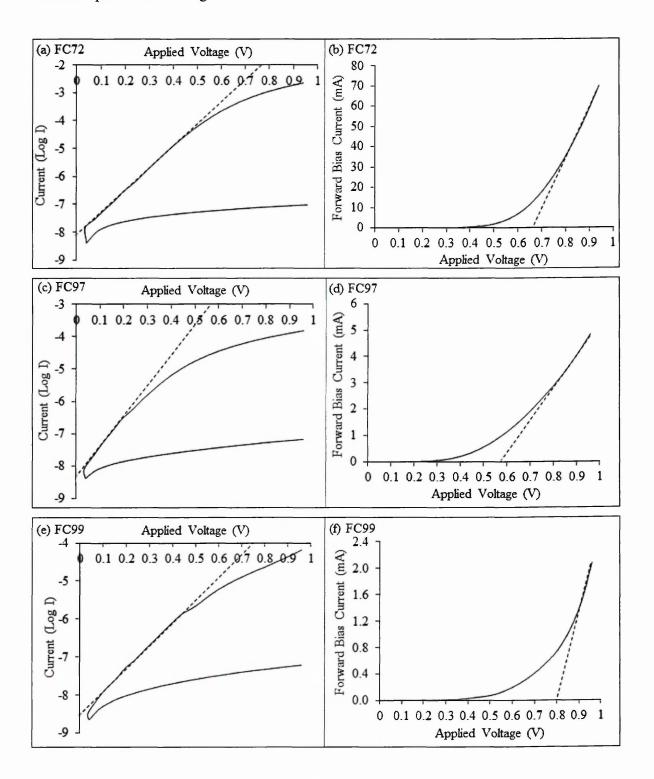

|      | 9.3.2 Solar cell device characteriza          | tion using dark I-V measurements | 217 |

| 9.4  | Photoluminescence studies                     |                                  | 221 |

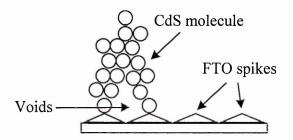

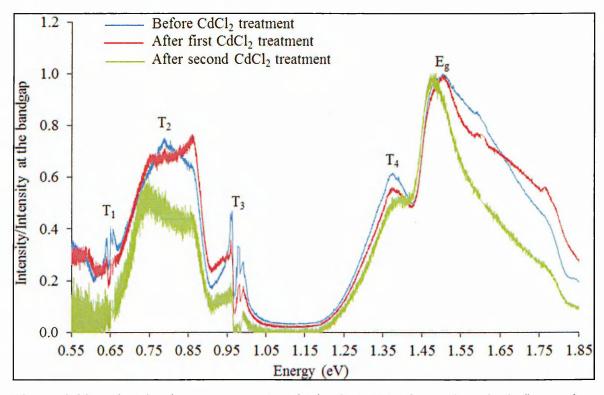

| 9.6  | Possible explanation on high current density  |                                  |     |

| 9.6  | Power density $(P_d)$ analysis                |                                  |     |

| 9.7   | Optin                                                     | nization of annealing temperature                                        | 227 |

|-------|-----------------------------------------------------------|--------------------------------------------------------------------------|-----|

| 9.8   | Conc                                                      | lusion                                                                   | 231 |

| 9.7   | Refe                                                      | rences                                                                   | 233 |

| Cha   | pter 10:                                                  | Metal-Insulator-Semiconductor (MIS) type electrical contacts in so       | lar |

| cells | 1                                                         |                                                                          | 236 |

| 10.1  | Intro                                                     | duction                                                                  | 236 |

| 10.2  | Fabri                                                     | cation of glass/FTO/n-CdS/n-CdTe/ZnTe/Au solar cells                     | 239 |

| 10.3  | 10.3 Assessment of glass/FTO/CdS/CdTe/ZnTe/Au solar cells |                                                                          | 240 |

| 10.4  | Resul                                                     | ts and discussions                                                       | 240 |

|       | 10.4.1                                                    | Reproducibility of higher device parameters $(V_{oc}, J_{sc})$ and $FF$  | 242 |

|       | 10.4.2                                                    | 2 Thickness of ZnTe pin-hole plugging layers                             | 251 |

| 10.5  | Concl                                                     | usion                                                                    | 253 |

| 10.6  | Refer                                                     | rences                                                                   | 255 |

| Cha   | pter 11:                                                  | Conclusion and future work                                               | 256 |

| 11.1  | Conclu                                                    | ısion                                                                    | 256 |

| 11.2  | Suggest                                                   | Suggestions for future work                                              |     |

|       | 11.2.1                                                    | Preparation of electrolytes using high purity chemicals                  | 257 |

|       | 11.2.2                                                    | Effective tellurium addition                                             | 258 |

|       | 11.2.3                                                    | Maintaining the effective concentration of Cd2+ ions in the bath         | 258 |

|       | 11.2.4                                                    | Reducing the resistivity of electrodeposited CdS                         | 259 |

|       | 11.2.5                                                    | Substituting fluorine doped tin oxide (FTO) with indium                  |     |

|       |                                                           | doped tin oxide (ITO)                                                    | 259 |

|       | 11.2.6                                                    | Lifetime studies of PPL                                                  | 259 |

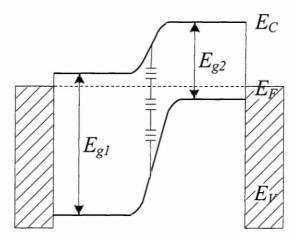

|       | 11.2.7                                                    | Graded bandgap solar cell structure                                      | 259 |

|       | 11.2.7                                                    | Incident photon to current efficiency (IPCE) or responsivity measurement | 260 |

| 11.3  | Referen                                                   | References                                                               |     |

## **Chapter 1: Introduction**

# 1.1 Global needs for renewable energies

According to the recent survey by United Nations (UN), world's population is expected to reach 9.6 billion by 2050. This is an increase of 33% from the current population that stands at 7.2 billion people [1]. One of the factors that contribute to the increase of human population is the improvement of human healthcare system. For examples, the usage of vaccine to combat fatal diseases such as tuberculosis and also the decline of birth mortality. Another factor that helps the growth of human population is the sufficient food supply due to the better advancement in agricultural technologies. The usage of synthetic fertilizers and pesticides is the methods used today to increase the yield of from the crops planted. The huge increase of human population means more energy (for example, electricity) is needed to support the continuity of convenience living.

Dependency on fossil fuels such as coal, petroleum and natural gas is not the answer for sustainable energy supply. It is because these energy sources are limited and will exhaust in the future. Burning more fossil fuels to cater the demand for energy will do more harm than good. Since fossil fuels are limited in supply, gradually the consumers will have to pay more for energy. This change is inevitable because demands for energy will exceed supplies.

It is well known that fossil fuels are one of the contributing factors to the greenhouse effect. Fossil fuels will emit greenhouse gases to the environment after burning. Carbon dioxide (CO<sub>2</sub>) and methane (CH<sub>4</sub>) are the examples of greenhouse gases. Greenhouse gases accumulated at the space will absorb the heat radiated from the sun and retransmit it back to the Earth's surface. This reaction creates global warming due to the inability of the Earth to quickly dissipate heat to the atmosphere.

In 2006, Paramount Pictures released a documentary film titled The Inconvenient Truth. This film featured Al Gore, a politician, environmental activist and also the former candidate for president of United States of America (USA). According to Al Gore, data from Keeling curve showed that the concentration of CO<sub>2</sub> (measured in parts per million volume - ppmv) in atmosphere keeps increasing every year since 1958 [2]. From this film, the viewers can learn about the negative impacts of global warming.

Among the negative impacts are massive flooding, drought, wide spreading of vectorborne diseases and many more.

In order to reverse the effects of global warming, it is necessary to reduce the carbon emission. Carbon emission can be reduced by planting more trees, driving electric vehicles, using energy efficient bulbs and also utilizing renewable energies for electricity generation.

# 1.2 The sources of renewable energy

Renewable energy is defined as "the energy from a source that is not depleted when used" [3]. The sources of renewable energy are as follows.

## 1.2.1 Wind energy

Flow of wind naturally carries kinetic energy. By using appropriate equipments, this kinetic energy can be converted into electrical energy. Wind energy is the renewable energy that has been used for more than one thousand years [4]. In Netherlands, initially wind turbines were used to drain water from the farmlands into the river. Later, wind energy was used for agricultural purposes.

In Europe, the presence of strong wind at North Sea has been exploited by nearby countries such as United Kingdom and Denmark by building onshore and offshore wind farms. Currently United Kingdom has the largest off-shore wind farm in the world known as the London Array. This wind farm has the installed capacity up to 630 MW and located 11 km to the north of North Foreland [5]. In Denmark, wind turbines with 3000 MW capacity have been installed before the end of 2005 [6]. By the end of 2007, electrical energy generated from the wind farms can supply 20% of its energy demand. Wind energy industry in Denmark also has provided jobs for nearly 29 000 people in 2008 [7].

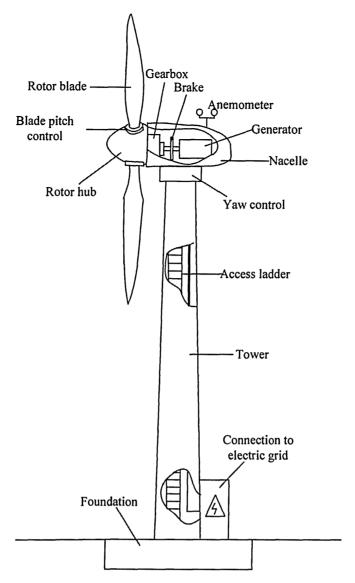

There are two types of wind turbine; horizontal axis wind turbine (HAWT) and vertical axis wind turbine (VAWT). HAWT is the one that is widely used nowadays. The schematic diagram of HAWT is shown in Figure 1.1.

Figure 1.1: Horizontal axis wind turbine (HAWT) showing its main components. Redrawn from [8].

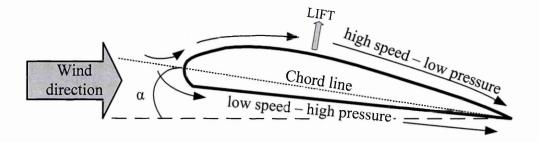

Basic components of HAWT consist of blades, gearbox, electrical generator, tower and yaw. After considering operational cost, maintenance cost and efficiency, few components are incorporated into the system such as controller, brake, anemometer and transformer. The blades are designed to have the same profiles like the aeroplane wings as shown in Figure 1.2. High speed wind flows at the top will create low pressure region while the low speed air stream at the bottom creates high pressure. The whole process finally induces lift upon the blades.

Figure 1.2: Aerodynamic helps induced lift on wind turbine blades. Redrawn from [9].

When the wind blows towards a wind turbine, the blades will rotate and so does the rotor hub. Rotor hub is connected to the low speed shaft. The connection between the low speed shaft and high speed shaft is implemented by the gearbox. Gearbox will increase the speed of the high speed shaft with respect to the low speed shaft but it depends on the gear ratios inside the gearbox.

A wind turbine is designed to operate below the maximum wind speed. This is called cut-out speed [10]. Above the cut-out speed, a wind turbine cannot withstand the force and strains asserted by the wind and could be damaged under severely harsh conditions. To solve this problem, wind turbines should have two main control mechanisms, the pitch control and yaw control.

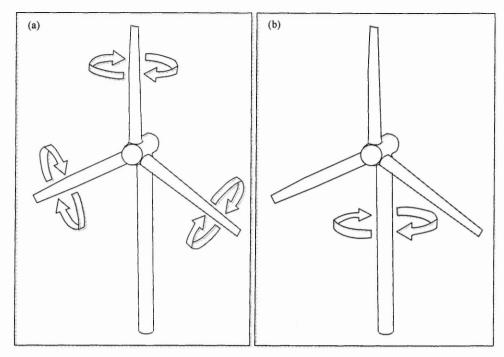

Pitch control, as shown in Figure 1.3(a) is useful in slowing down the angular speed of a wind turbine. In pitch control mechanism, the blades will adjust their orientation relative to the wind direction until the maximum angle of attack,  $\alpha$  is exceeded. When it happens, the blades are stalled and the lift will drop, thus slowing down the angular speed.

To have the maximum angular speed, the orientation of the nacelle should be directed towards the oncoming wind. Yaw control (Figure 1.3(b)) is employed to turn the nacelle vertically in order to ensure the direction of the nacelle always facing the oncoming wind.

**Figure 1.3:** Pitch control (a) and yaw control (b) are employed to safeguard wind turbine from damages and to ensure highest possible power extracted from the oncoming wind respectively. Redrawn from [11].

Wind energy is abundant, clean and can be operational for 24 hours a day. However, wind energy harvesting is location specific and in addition, the direction and speed of wind are uncontrollable. The uncontrollability of wind direction and speed make the output from wind turbine difficult to be fixed constant.

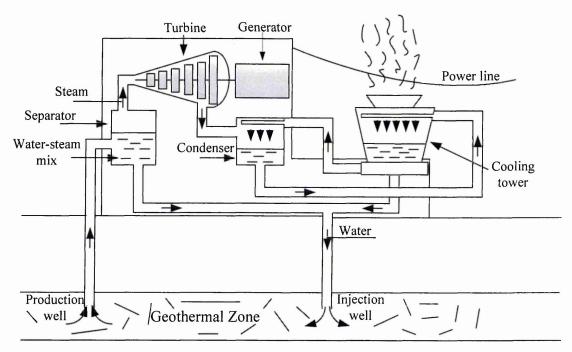

## 1.2.2 Geothermal energy

Water trapped below the surface of the Earth is heated by molten and very hot solid rocks called magma. Magma is normally found at certain places on Earth, where the volcanic activities are present. Water that comes from the rain for example, can flow between the rocks that build-up Earth's crust and finally arrive close to the magma zone. Water that is located between the Earth's surface and magma will be heated up to 280°C naturally. This area is known as geothermal zone. Geothermal zone is located between 600 to 1500 m underground [12]. To extract this heated fluid, production well must be built. Production well is created by drilling down to the geothermal zone as shown in Figure 1.4. When the geothermal zone is found, the hot fluid will come to the Earth's surface driven by its own pressure. When the fluid comes up, it will be

channelled to the separator where water and steam are separated. Steam is used to drive steam turbine and generate electricity.

After driving the steam turbine, the steam will be turned back into water by condensation and sent back to the injection well together with the water collected in the separator. It is important to send the water back to the geothermal zone because without this feedback system, the fluid extracted at the production well be depleted too fast before it is replenished. Geothermal energy is clean, renewable and has almost zero CO<sub>2</sub> emission but the cost of electricity coming from this technology is still expensive compared to fossil fuels. The main reason is; to build a geothermal power plant, the cost will be higher compared to the fossil fuel power plants. This is due to the drilling works involved.

Figure 1.4: Main features of a geothermal energy system. Redrawn from [13].

# 1.2.3 Hydroelectricity

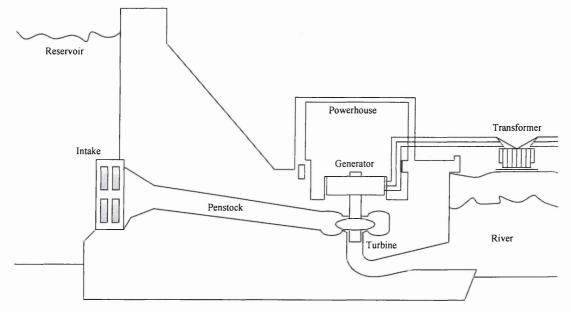

Hydroelectricity (shown in Figure 1.5) is the conversion of potential energy of water to electrical energy. Hydro power has been used for hundreds of years. People during the ancient civilisation used water mill for agricultural purposes such as grinding grains and irrigation. To utilize hydro power, dam must be built at the most strategic location across a river. When a dam is constructed, the flow of water from one side to

the other side can be controlled. Close to the dam huge water reservoir will be built to increase the water storage.

The next task for hydropower engineers is to install turbines and intakes. Installation of intakes will allow hydro power plant operators to control the flow of water through the turbines. The control of water flow through the turbines will determine the electrical power output. If the demand for electrical power is high, more intakes will be open so that more turbines will be driven thus generates more power. Hydro power plant can be built to supply electrical power in gigawatt range. Examples given, Three Gorges Dam in China (22.5 GW) [14], Itaipu Dam at Brazil and Paraguay border (14 GW) [15] and Tucurui Dam in Brazil (8 GW) [16]. Besides fossil fuel and nuclear power plants, hydropower plants also capable for supplying electricity for base load demand to households and industries. The available power, P can be calculated from Equation 1.1 [17],

$$P = \eta.\rho.Q.g.h \tag{1.1}$$

Where;

P is the power in watts  $\eta$  is the dimensionless efficiency of the turbine  $\rho$  is the density of water in kilograms per cubic metre Q is the flow in cubic metres per second Q is the acceleration due to gravity Q is the height difference between inlet and outlet

Even though hydro power has zero fuel cost and nearly zero CO<sub>2</sub> emission during operation, the cements and metals used in the construction of a dam are the sources for CO<sub>2</sub> and CH<sub>4</sub> emission. The capital cost to build a hydropower plant is hugely expensive. The cost includes civil engineering works, land reclamation, population relocation, etc. Besides that, the construction of hydropower plant could lead to the deteriorations of environmental quality nearby the power station. News regarding these issues have been reported in *Nature* magazine in May 2011 [18].

**Figure 1.5:** A typical hydroelectricity system showing its main features. Redrawn from [19].

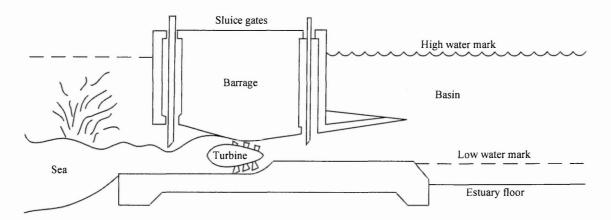

# 1.2.4 Tidal energy

Tidal power uses the same concept as in hydropower electricity (shown in Figure 1.6). In some countries where estuaries are available, water barrage can be built to capture and store huge volume of water. Water can be captured when the high tide occurs. The captured water is stored at the basin. When the tide becomes low, water from the basin will be released back to the sea. The flow of water back to the sea will drive turbines and thus generates electrical power. Tidal electricity that employs this kind of mechanism is hugely expensive and needs feasibility studies before the construction begin to ensure least impact on the environment especially aquatics life.

Figure 1.6: Schematic diagram of a typical tidal power generator. Redrawn from [20].

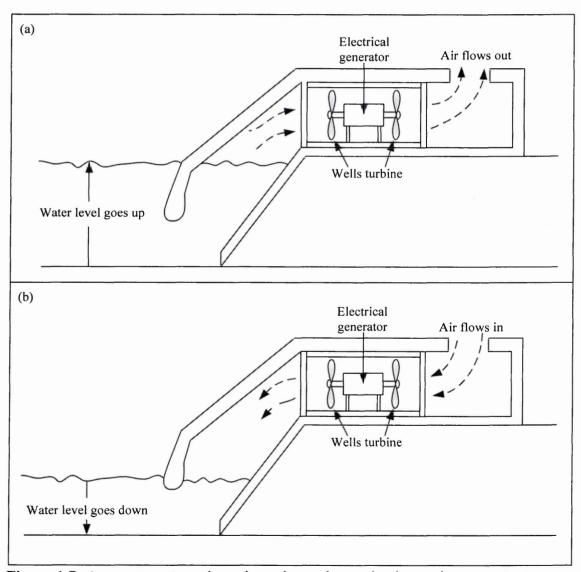

# 1.2.5 Oscillating water column (wave energy)

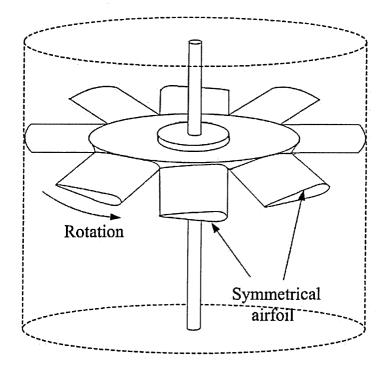

Oscillating water columns (OWC) are built along the sea shores and use air as the fluid to rotate the turbines inside. When wave hit the water columns, the air trapped inside water columns will be pushed to go inside the tunnel as shown in Figure 1.7(a). The air pressure asserted on the turbine will induce torque and rotates the turbine. When the wave recedes, the atmospheric pressure will push the air inside but from the opposite direction as shown in Figure 1.7(b). In OWC, Wells turbine is used. Wells turbine (Figure 1.7) is specially engineered so that no matter which direction the wind flows, the rotation is fixed in only one direction. This will ensure the constant rotation of turbines producing electrical power.

**Figure 1.7:** An ocean water column is engineered to maintain continuous output power from the powertrain installed inside.

**Figure 1.8:** Wells turbine has symmetrical airfoil for all blades to ensure only one-way rotation. Redrawn from [21].

# 1.2.6 Biomass energy

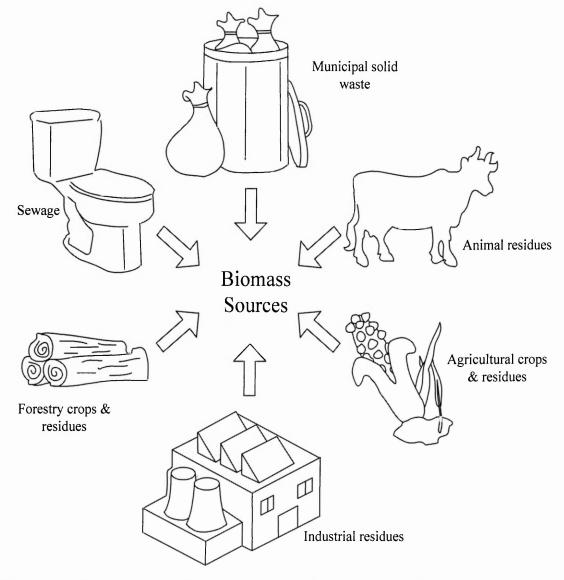

Biomass energy is already being used nowadays. Lack of landfills available today, drives the policymakers to think the alternative ways of managing wastes. Any waste that is biodegradable is the source of biomass. The sources of biomass are shown in Figure 1.9. Some biomass energy systems depend on the production of synthetic gas (syngas) from biomass sources. Syngas is the mixture of carbon monoxide (CO) and hydrogen (H<sub>2</sub>). The next sub-section will be discussing about anaerobic digestion and gasification.

Figure 1.9: Various sources for biomass energy. Redrawn from [22, 23].

# 1.2.6.1 Anaerobic digestion

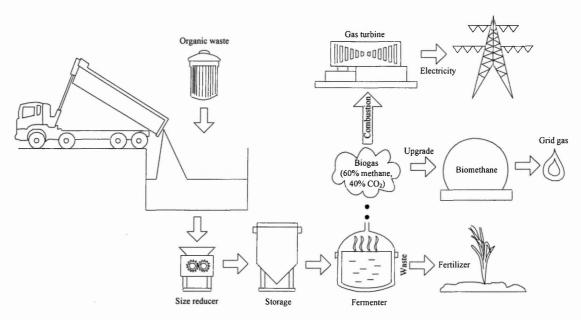

In anaerobic digestion, bacteria from methanogens family digest the biological wastes and produce CH<sub>4</sub>, H<sub>2</sub>S and NH<sub>3</sub>. Figure 1.10 shows the process of producing biogas from anaerobic digestion. Biodegradable waste is collected and dumped into the storage pit. From the storage pit, the size of waste is reduced using mincer and then stored. The waste will be transferred to the fermentation tank. In the fermentation tank, methanogens bacteria, which is naturally occurring, will digest the biological waste and produce biogas. To generate electricity from biogas, the combustion of biogas is done inside a gas turbine.

Alternatively, biogas can also be upgraded to biomethane by removing other gases. As a result, biomethane content could be 96% of methane gas [24]. Waste collected from the fermentation tank is rich in nutrients such as ammoniums and phosphates and can be used as fertilizer.

**Figure 1.10**: Electricity generation from anaerobic digestion. Redrawn from [25,26].

#### 1.2.6.2 Gasification

Gasification is a form of chemical reaction of biomasses in oxygen-starved environment. Woods together with forestry residues and industrial wastes are biomasses that cannot be biodegraded by anaerobic bacteria. Syngas can be extracted from these wastes through gasification process as shown in Figure 1.11. Any carbon containing substance can be used as the feedstock. High temperature and pressure around 1400°C and 6900 kPa [27] respectively are used in gasification process. Firstly, chemical reaction called pyrolysis happens inside the gasifier thus producing chars and volatiles such as methane, hydrogen and tars. In the next stage, carbon containing compounds react with oxygen to form CO<sub>2</sub> and heat, which later will be utilized for futher reactions.

When chars (carbon containing material) react with steam, the syngas is produced according to the chemical rection;

$$C + H_2O \rightarrow H_2 + CO \tag{1.2}$$

Gaseous constituents will go to the top of the gasifier and will undergo clean-up process. Firstly, any particle that co-exists with syngas will be removed. At the second stage, sulfur will be removed. Finally syngas that contains two of its main components (CO and H<sub>2</sub>) is produced. Steam reforming and water-gas shift are the next major steps involved in order to obtain methane and hydrogen. Both gases are normally employed for combustion in gas turbine. To minimize the waste of heat energy, steam turbine can be incorporated into the system. This is to utilize the heat energy coming out from syngas combustion and convert the heat into electrical energy.

Figure 1.11: Electricity generation from gasification. Redrawn from [28].

The main advantage of using biomass energy is the sources of biomass are easy to get. Since biomass sources can be obtained from waste, they can be classified as cheap fuels. Utilizing biomass energy is also helpful in solving landfill problems. Increasing number of population means the need for bigger landfills is inevitable. Biomass energy can help in minimizing this problem because instead of sending more wastes to the landfills, the wastes can be converted into energy.

Biomass sources carry low energy per unit weight compared to fossil fuels. However, depending on location, biomass energy can be utilized to supply electricity for base load.

## 1.2.7 Solar energy

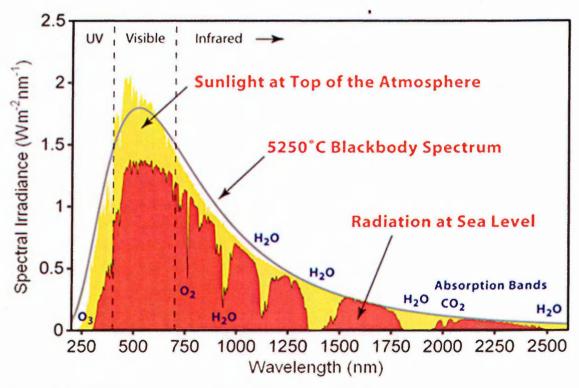

Sunlight is a form of energy originates from the sun. Sunlight emits electromagnetic radiation that consists of three radiation regions which have different frequencies. These radiations are ultraviolet (UV), visible (Vis) and infrared (IR) and commonly represented as the solar spectrum as shown in Figure 1.12. Ultraviolet radiation has wavelengths that are less than 400 nm. For visible radiation, the wavelengths are between 400 nm to 700 nm and above 700 nm is an infrared region. Figure 1.12 shows that the magnitude of spectral irradiance is different between the radiation at the top of the atmosphere and radiation at sea level. It shows that solar spectrum that reaches the Earth's surface has undergone attenuations and absorptions at the atmosphere. Hazardous ultraviolet radiation will be absorbed by the ozone layer. As a result, the solar spectrum that reaches the Earth is safe for all live forms.

**Figure 1.12:** Solar spectrum showing spectral irradiance against wavelength. Three radiation regions (UV, Vis and IR) are also shown [29].

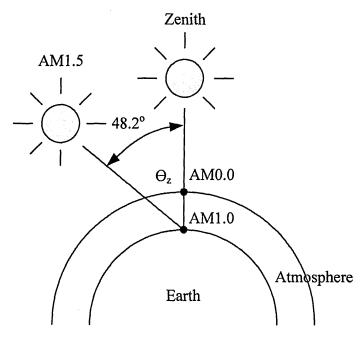

The solar irradiance (measured in Wm<sup>-2</sup>) is governed by the air mass coefficient (simply known as air mass - AM). Air mass coefficient is defined as reciprocal of cos  $\Theta_z$ . Where  $\Theta_z$  is the angle between the actual position of the sun with respect to the zenith as shown in Figure 1.13 [30].

$$AM = \frac{1}{\cos \Theta z} \tag{1.2}$$

Figure 1.13: Determination of air mass coefficient based on the position of the sun with respect to the zenith.

When the sun stands at the zenith, the air mass coefficient at the top of the atmosphere is known as AM0.0. The power incident per unit area (solar irradiance) at this location is ~1367 Wm<sup>-2</sup> [30]. This value is designated as the solar constant. At the sea level, the air mass is known as AM1.0 and the solar irradiance will further reduce to just over ~1000 Wm<sup>-2</sup> [31]. This reduction is due to the absorption and scattering of the incident radiation by particulate matter, clouds and air molecules [30]. If the sun moves 48.2° from the zenith, the power incident per unit area on the Earth's surface is equivalent to ~1000 Wm<sup>-2</sup>. At this location, air mass coefficient is known as AM1.5 and it is widely used among the solar cells researchers around the world to evaluate the performance of solar cells and solar panels [29].

There are two ways to harvest solar energy and convert it directly into heat or electrical energy. The first method is known as solar thermal conversion. Generally, thermal conversion works by absorbing heat radiated from the sun using appropriate equipments. The heat absorbed can be used for other purposes. One of the examples of utilization of solar energy is concentrated solar tower. Section 1.2.7.1 will explain more about solar thermal conversion technology.

The second method is the photovoltaic (PV) conversion. Photovoltaic cell is an electronic device that converts light energy directly into electrical energy. In this conversion, special materials are used to absorb light (photons). Energy of the photons will later be converted into electrical energy when photons interact with valence electrons inside the absorbing materials. Further explanations of photovoltaic conversion are given in section 1.2.7.2.

# 1.2.7.1 Solar thermal conversion (Concentrated Solar Tower)

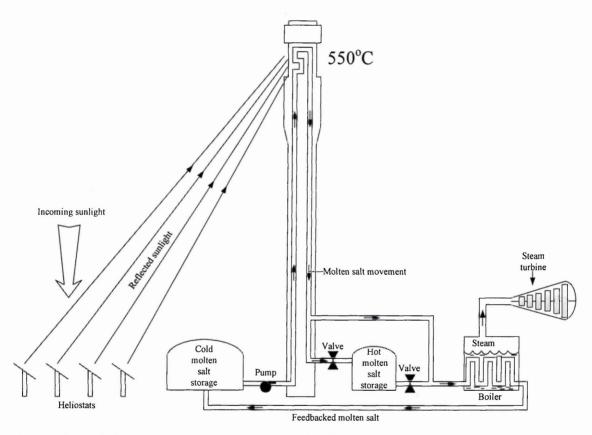

Concentrated solar tower utilizes heat from the sun. Incoming radiation is reflected towards the top of the solar tower with the help of many heliostats. During the daytime, the heliostats are controlled to assure the maximum heat radiation is projected to the top of the solar tower. Temperature at the top of the solar tower can go up to 550°C or higher depending on designed system. Figure 1.14 shows how the solar tower is operated.

Molten salt is pumped from the storage up to the top of the tower to be heated. Molten salt is used because it has higher boiling point than water and does not dissipate heat as quickly as water. The heated molten salt is channelled to the hot molten salt tank. The hot molten salt tank needs to be properly insulated because it serves as the energy storage. The heat energy stored for 15 hours has been demonstrated by Gemasolar power plant in Spain [32]. Heat energy stored here can be used during the night. The hot molten salt will be sent to the heat exchanger where it acts as a fuel to boil water and turn the water into steam. Later, the steam is used to drive the steam turbines. Electrical energy is generated when the steam turbine is connected to the electrical generator.

The first two solar towers were built in 1984. Firstly, the 2.5 MW THEMIS tower was built in the French Pyrenees, followed by the 1 MW Molten-Salt Electric Experiment in the United States of America (USA) [33]. Spain has solar towers with capacity exceeding 10 MW. The PS10 power plant with 10 MW output is the world's

first commercial solar tower [34]. United States of America currently has the largest concentrated solar power plant in the world with 354 MW capacity [35].

Solar tower is better compared to solar photovoltaic system in terms of the period of electricity generation. The utilization of molten salt as the energy storage makes possible for this system to produce electrical energy for 24 hours a day. However, this system could not encourage the public to produce their own electrical energy. Currently, many developed countries around the world such as United Kingdom, USA, Germany, etc, encourage their citizen to install their own solar panels. In return, the governments will purchase the energy produced by any household through the system called feed-in tariff.

Figure 1.14: Schematic diagram of a concentrated solar power plant.

#### 1.2.7.1 Photovoltaic (PV) conversion

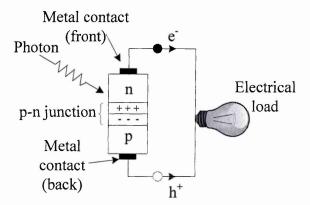

There are some materials that can absorb light (photons) and convert the energy of the incident photons into electrical energy. These materials are known as absorber materials incorporated in solar cells. When photons are absorbed, these photons will interact with the valence electrons of the solar cell materials by giving off their energy

to the valence electrons. Since valence electrons gain more energy, they will move to the higher energy states or may be liberated from the host atom. The liberated electrons are now free to move inside the crystal of the absorbing material and can create useful current if they are separated and transported to an external electrical circuit.

Four basic steps must be brought together simultaneously in order to achieve effective photovoltaic energy conversion [36]:

- i. solar cells absorb photons

- ii. charge carries (electron-hole pairs EHPs) are created

- iii. separation of charge carriers before recombination

- iv. transport of charge carriers through external circuit to provide useful electrical current.

Figure 1.15 shows how a solar cell works in converting photons into useful current. The heart of an efficient solar cell is the built-in electric field or simply a photovoltaic (PV) active junction. In simple words, the role of a PV junction (for example, p-n junction) is to sweep away photo-generated electrons and holes to the opposite directions. By sweeping electrons and holes to the opposite directions, these charge carriers will be forced to move through the external circuit thus creating an electrical current. Further explanations about p-n junction are given in Chapter 2.

Solar cells should have metal contacts at the front and the back. The role of metal contacts is to efficiently collect charge carriers by providing low electrical resistance at these interfaces. This will increase the efficiency of solar cells.

**Figure 1.15:** The role of a p-n junction is to absorb light, create electron-hole pairs and then sweep these charge carries to the opposite directions.

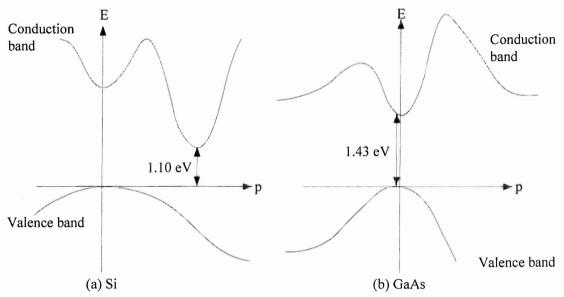

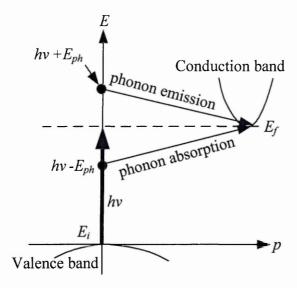

#### 1.3 Aim and objectives

During the past two decades, research progress in CdS/CdTe solar cell has been stagnated due to lack of understanding in this complex electronic device. Majority of research groups work on p-n hetero-junction structure between n-type cadmium sulfide (n-CdS) and p-type cadmium telluride (p-CdTe). After Britt and Ferekides reported 15.8% efficiency in 1993 [37], the efficiency of the CdS/CdTe just increased to 16.5% after 8 years [38].

In 2002, Dharmadasa *et al* proposed a new model to explain the photovoltaic activity of CdS/CdTe solar cells. They proposed that in the future, the development of CdTe solar cells should be based on the new design which is the n-n hetero-junction between n-CdS/n-CdTe plus large Schottky barrier at the back of the cell [39]. In this paper, they have reported 18% conversion efficiency. The solar cells were fabricated using electrodeposited CdTe from non-aqueous solution (ethylene glycol) at temperature of 160°C.

However, the primary use of ethylene glycol as the automobiles' coolant and anti-freeze agent raise concerns about the toxicity. The safer way to electrodeposit semiconducting materials is by substituting ethylene glycol with deionized or double distilled water as the solvent. In fact, the performance of CdTe solar cells electrodeposited from an aqueous electrolyte is satisfactory if judging from the reported efficiencies by BP Solar (14.2%) [40] and Baker *et al* (13.5%) [41].

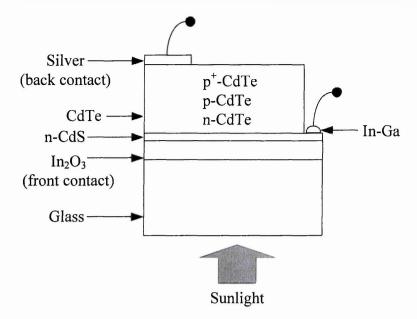

The main aim of this research project is to contribute towards the development of low-cost high efficiency thin film solar cells. Most works carried out in this project are based on the previous works reported by D.G. Diso [42]. In his works, he has identified the suitable growth voltages to electrodeposit CdTe layers using 2-electrode system in an aqueous electrolyte. From his work, he found that the suitable voltages to grow CdTe layers are from 1570 mV to 1580 mV. He also reported the highest efficiency of 7.6% with solar cell structure shown in Figure 1.16.

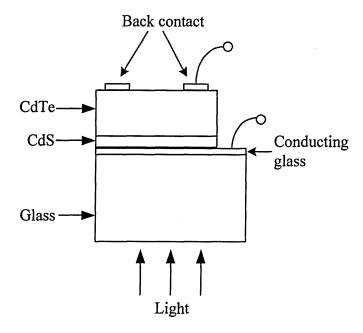

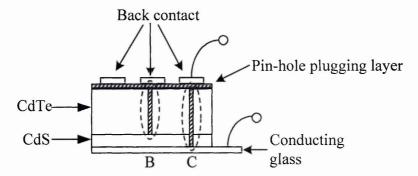

Both semiconductors; cadmium sulfide (CdS) and cadmium telluride (CdTe) layers were grown by electrodeposition. In literature, the structure is written as glass/conducting glass/CdS/CdTe/back contact [43,44]. Significance progress has been achieved previously, this research is the continuation of works from D.G. Diso [41]. In simple words, this is a long term project of making reproducible low-cost and high efficiency solar cells.

Figure 1.16: The schematic diagram of the basic CdS/CdTe solar cell.

This research project involves material growth by low-cost electroplating technique, materials characterisation, solar cell fabrication, assessment and development. Therefore, the objectives of this research are as follows:

- i. To optimise the electrodeposition of three semiconducting materials; CdS, ZnTe and CdTe using electrodeposition with 2-electrode system in aqueous electrolytes.

- ii. To study the structural, optical, electrical, compositional and morphological properties of the electrodeposited layers using facilities available at Materials and Engineering Research Institute at Sheffield Hallam University.

- iii. To fabricate CdS/CdTe thin film solar cells using all electrodeposited layers. Two solar cell structures were fabricated. Firstly, the glass/TCO/CdS/CdTe/metal structure. Secondly, the glass/TCO/CdS/CdTe/ZnTe/metal structure.

- iv. To assess the performance of the fabricated thin film solar cells using current-voltage (I-V) measurement and developed these devices by optimising all processing steps to achieve highest possible efficiencies.

# 1.4 Summary

This chapter started with the economic and environmental issues facing humanity nowadays. It is obvious that the dependency on fossil fuels is not the answer for healthier and greener planet. Gradual replacement of fossil fuels with renewable energies as the prime energy source is the best answer for energy security.

Among the renewable energies discussed in section 1.2, solar energy seems to be the best candidate for terrestrial renewable energy application [36]. Solar energy is free, abundant, environmental friendly and produces near zero carbon emission.

At the last section of this chapter, the aim and objectives of this research programmed were also presented.

#### 1.5 References

- 1. www.un.org/apps/news/story.asp?NewsID=45165, last accessed May 2014.

- 2. <a href="http://en.wikipedia.org/wiki/Keeling Curve">http://en.wikipedia.org/wiki/Keeling Curve</a>, last accessed May 2014.

- 3. <u>www.oxforddictionaries.com</u>, last accessed May 2014.

- 4. P. D. Dunn, *Renewable Energies: Sources, conversion and application*, Peter Peregrinus Ltd, London (1986).

- 5. Power from London Array, Modern power systems, **32** (12) (2012) 6.

- 6. H. Sharman, Proceedings of the Institution of Civil Engineers: Civil Engineering, **158** (2) (2005) 66-72.

- 7. Wind energy The case of Denmark, CEPOS Center for Politiske Studier September 11, 2009.

- 8. http://en.wikipedia.org/wiki/Wind turbine design, last accessed May 2014.

- 9. <u>www.diracdelta.co.uk/science/source/a/e/aerofoil/source.html</u>, last accessed June 2015.

- 10. P. Jain, Wind Energy Engineering, McGraw-Hill, New York (2011).

- 11. www.ni.com/white-paper/8189/en/, last accessed May 2014.

- 12. H.C.H. Armsted, Geothermal energy: Review of research and development, Unesco, Paris (1973).

- 13. <a href="http://visual.merriam-webster.com/energy/geothermal-fossil-energy/production">http://visual.merriam-webster.com/energy/geothermal-fossil-energy/production</a> electricity-from-geothermal-energy.php, last accessed May 2014.

- 14. Three Gorges Dam Reaches Full Power. Nature, 487 (2012) 144.

- 15. M. Rivarolo, J. Bogarin, L. Magistri and A.F. Massardo, *International Journal of Hydrogen Energy*, **37** (2012) 5434-5443.

- 16. P. M. Fearside, *Environmental Management*, **24** (1999) 483-495.

- 17. H. Wagner and J. Mathur, *Introduction to Hydro Energy Systems*, Springer, Berlin (2011).

- 18. Three Gorges Damn. Nature, 473 (2011) 424.

- 19. <a href="http://en.wikipedia.org/wiki/Hydroelectricity">http://en.wikipedia.org/wiki/Hydroelectricity</a>, last accessed May 2014.

- 20. <u>www.esru.strath.ac.uk/EandE/Web\_sites/01-02/RE\_info/Tidal%20 Power.htm</u>, last accessed May 2014.

- 21. <a href="https://coastalenergyandenvironment.web.unc.edu/ocean-energy-generating-technologies/wave-energy/oscillating-water-column/">https://coastalenergyandenvironment.web.unc.edu/ocean-energy-generating-technologies/wave-energy/oscillating-water-column/</a>, last accessed May 2014.

- 22. <a href="http://renewable-energy-watch.info/2014/01/08/turning-biomass-into-clean-energy">http://renewable-energy-watch.info/2014/01/08/turning-biomass-into-clean-energy/</a>, last accessed May 2014.

- 23. <u>www.riomay.com/renewable-technologies/biomass-energy</u>, last accessed May 2014.

- 24. <u>www.european-biogas.eu/wp-content/uploads/files/2013/10/eba\_biomethane\_factsheet.pdf</u>, last access May 2015.

- 25. <u>www.richboroughenergyplant.com/anaerobicdigestionplant.htm</u>, last accessed May 2014

- 26. <u>www.biogas-info.co.uk/index.php/what-is-anaerobic-digestion.html</u>, last accessed May 2014.

- 27. <a href="http://science.howstuffworks.com/environmental/green-tech/energy-production/gasification.htm">http://science.howstuffworks.com/environmental/green-tech/energy-production/gasification.htm</a>, last accessed May 2014.

- 28. www.chamco.net/Gasification.htm, last access May 2014.

- 29. http://en.wikipedia.org/wiki/Air mass (solar energy), last accessed May 2014.

- 30. T. Markvart, Solar Electricity, 2<sup>nd</sup> edition, John Wiley & Sons, Chichester (2000).

- 31. R. A. Messenger, *Photovoltaic Systems Engineering*, 3<sup>rd</sup> edition, CRC Press, Boca Raton (2004).

- 32. Graham Keeley. Solar energy at nights offer bright future: Plant in sunny Spain can supply 100,000 people, The Times, Oct 6 (2011), Pg. 24. Sect: News.

- 33. R. Dunn, P. Hearps, and M. Wright, *Proceedings of the IEEE*, **100** (2012) 504 515.

- 34. World's largest solar tower goes commercial, Modern Power System, **29** (5) (2009) 5.

- 35. D. Mills, Solar Energy, **76** (2004) 19-31.

- 36. I.M. Dharmadasa, *Advances in Thin-Film Solar Cells*, Pan Stanford Publishing, Singapore (2012).

- 37. J. Britt, C. Ferekides, App. Phys. Lett. **62** (22), (1993) 2851-2852.

- X. Wu, R.G. Dhere, D.S. Albin, T.A. Gessert, C. DeHart, J.C. Keane, A. Duda,

T.J. Coutts, S. Asher, D.H. Levi, H.R. Moutinho, Y. Yan, T. Moriarty,

S. Johnston, K. Emery, and P. Sheldon, 17th European Photovoltaic Solar Energy

Conference, Munich, (2001) 995.

- 39. I. M. Dharmadasa, A. P. Samantilleke, N. B. Chaure and J. Young, *Semicond. Sci. Technol.*, **17** (2002) 1238-1248.

- 40. J. M. Woodcock, A. K. Turner, M. E. Ozsan and J. G. Summers, *Proceedings of the 22<sup>nd</sup> IEEE PVSC*, New York, (1991) 842.

- 41. J. Baker, S. J. Calif, R. J. Marshall, M. Sadeghi, *US Patent 5,478,445*, December 1995.

- 42. D.G. Diso, Research and Development of CdTe based Thin Film Solar Cells, (PhD Thesis), Sheffield Hallam University (2010).

- 43. I.M. Dharmadasaa, Current Applied Physics, 9 (2009) e2-e6.

- 44. I.M. Dharmadasa, A.P. Samantilleke, J. Young and N.B. Chaure, *Proc. of 3rd World PV Conference*, Osaka (2003) 547-550.

# 2.1 Introduction

A brief introduction of solar cell and photovoltaic (PV) effect has been presented in Chapter 1. As a continuation, this chapter will firstly, introduce the intrinsic and extrinsic materials for solar cells application followed by the explanation on how the electron-hole pairs (EHPs) are created and separated inside a solar cell.

## 2.2 Solar energy materials

In physics, materials can be classified into three groups. They are conductors, insulators and semiconductors. Table 2.1 shows the classification of conductor, semiconductor and insulator materials. They are separated with each other according to their electrical conductivity and bandgap values.

**Table 2.1:** Classisfication of materials according to their electrical conductivities and bandgaps [1].

| Parameter                           | Conductors         | Semiconductors          | Insulators                |

|-------------------------------------|--------------------|-------------------------|---------------------------|

| Conductivity (S)(Ωcm) <sup>-1</sup> | $\sim 10^6 - 10^0$ | $\sim 10^{0} - 10^{-8}$ | $\sim 10^{-8} - 10^{-20}$ |

| Bandgap (E <sub>g</sub> ) (eV)      | ≤ 0.3              | ~ 0.3-2.5               | ~ 2.5-10                  |

Solar cells are fabricated from semiconductors. Materials for semiconductor are assigned into particular groups according to their position in periodic table. Table 2.2 lists the elements used for the production of semiconducting materials.

**Table 2.2:** Elements used for producing semiconducting materials according to their position in periodic table [1].

| Group - I | Group – II | Group - III | Group – IV | Group - V | Group - VI |

|-----------|------------|-------------|------------|-----------|------------|

| Cu        | Zn         | В           | С          | N         | S          |

| Ag        | Cd         | Al          | Si         | P         | Se         |

|           |            | Ga          | Ge         | As        | Те         |

|           |            | In          | Sn         | Sb        |            |

Semiconducting materials include elemental semiconductors such as carbon, silicon and germanium and also compound semiconductors. Compound semiconductors are produced from the chemical reaction of two or more elements as listed in Table 2.2. If one element from group II is chemically reacted with one element from group VI through chemical reaction, the resulting materials are known as II-VI semiconductors. Examples of II-VI semiconductors are ZnTe, CdS and CdTe. Similarly, if one element from group III is chemically reacted with one element from group V, the resulting materials are known as III-V semiconductors.

Ternary and quaternary compound semiconductors are produced through the chemical reaction of three and four elements respectively. Table 1.3 shows various types of semiconducting materials.

**Table 2.3:** Examples of semiconducting materials. Materials shown are elemental, binary, ternary and quaternary compound semiconductors.

| Semiconductor family              | Examples of Semiconductors                                       |

|-----------------------------------|------------------------------------------------------------------|

| Group IV Elemental semiconductors | C, Si, Ge                                                        |

| III-V binary semiconductors       | AlN, AlP, AlAs, GaN, GaP, GaAs, InP,                             |

| II-VI binary semiconductors       | ZnS, ZnTe, ZnO, CdS, CdSe, CdTe,                                 |

| Ternary compound semiconductors   | CuInSe <sub>2</sub> , $Cd_xHg_{(1-x)}Te$ , $Al_xGa_{(1-x)}As$    |

| Quaternary compound               | CuInGaSe <sub>2</sub> (CIGS), Cu <sub>2</sub> ZnSnS <sub>4</sub> |

| semiconductors                    |                                                                  |

# 2.2.1 Intrinsic and extrinsic materials

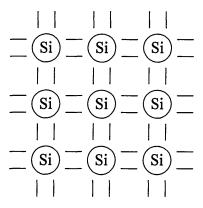

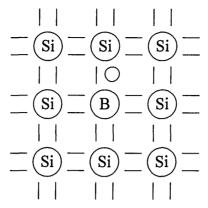

Silicon is the most researched semiconductor in the past 70 years. The discovery of p-n junction in 1940 by American physicist, Russell Ohl has led to the invention of electronics devices such as diodes, LEDs, transistors, solar cells etc [2]. Any pure material with very low impurities is called intrinsic materials. Inside intrinsic silicon, the silicon atoms are bound with each other with covalent bonding as shown in Figure 2.1.

Figure 2.1: Covalent bonding in silicon crystal lattice.

If one of the valence electrons in Figure 2.1 receives sufficient energy, for example, heat from surrounding, it can untie itself from the covalent bond and move inside the crystal. This unbound electron can now contribute to the flow of electrical current. By having more free electrons, the magnitude of electrical current can be increased.

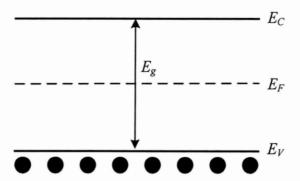

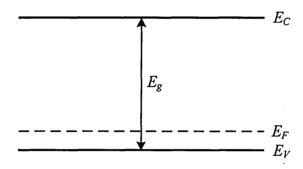

In device physics, it is more appropriate to present intrinsic semiconductors with energy band diagram as shown in Figure 2.2. A conventional energy band diagram normally shows the valence band  $(E_V)$ , conduction band  $(E_C)$ , forbidden bandgap  $(E_g)$  and Fermi level  $(E_F)$ . The black dots in Figure 2.2 represent the valence electrons. At Fermi level, the probability of finding an electron is 0.5 according to the Fermi-Dirac probability function,  $f_F(E)$  shown in Equation 2.1 [3].

$$f_F(E) = \frac{1}{1 + \exp\left(\frac{E - E_F}{kT}\right)} \tag{2.1}$$

Where;

E is the electrons energy (eV)

$E_F$  is the Fermi level (eV)

k is the Boltzmann constant  $(1.38 \times 10^{-23} \text{ JK}^{-1})$

T is the temperature (K).

**Figure 2.2:** Conventional energy band diagram of intrinsic material showing the position of valence band, conduction band and Fermi level.

The valence band represents the highest energy level occupied by electrons while the lowest unoccupied energy band is known as the conduction band. The energy gap between the bottom of the conduction band and the top of the valence band is called the bandgap. Bandgap represents the minimum energy (in eV) that is needed for an electron to be excited from the valence band to the conduction band. Different semiconductors will have different bandgap values. Conventionally, the Fermi level for an intrinsic material is positioned at the middle of the bandgap.

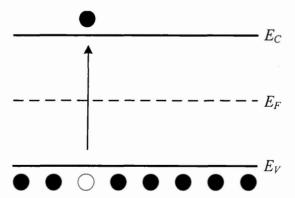

When an electron is promoted to the conduction band after receiving sufficient energy, it will create a vacancy in the valence band. This electron vacancy is known as a 'hole' and is represented by a white dot in Figure 2.3.

In order to create useful current, electrons in conduction band must be transported through an external circuit before they recombine with holes.

**Figure 2.3:** Creation of a hole in the valence band when an electron receives energy greater than the bandgap.

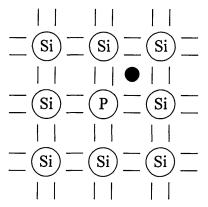

To increase the magnitude of electrical current, impurities can be added to the intrinsic materials as shown in Figure 2.4. In Figure 2.4, other elements such as phosphorus can be added into the silicon lattice. In this case, phosphorus (P) is called donor atom because it has an extra valence electron compared to silicon. This process is known as doping. By doping silicon with phosphorus, silicon now has more free electrons inside its lattice. Since it has impurities, it is no longer an intrinsic material. It has become an extrinsic material or simply known as an n-type material. The energy band diagram for n-type materials is shown in Figure 2.5. For n-type materials, the position of Fermi level is close to the conduction band.

**Figure 2.4:** Covalent bonding between silicon atoms and phosphorus (P) atoms. P is called donor atom because it has one electron more than silicon atom.

**Figure 2.5:** Energy band diagram for n-type material. Fermi level is positioned close to the conduction band.

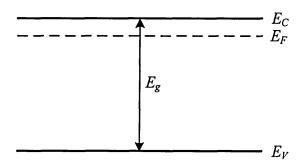

If silicon is doped by atoms that have one electron less, for example, boron (B), it is called a p-type material. Figure 2.6 shows the bonding of boron atoms with silicon atoms. Since boron has one valence electron less than silicon, it is called acceptor atom. The energy band diagram for p-type materials is shown in Figure 2.7. For p-type

materials the position of Fermi level is close to the valence band. Table 2.4 summarizes the differences between n-type and p-type materials.

**Figure 2.6:** Covalent bonding between silicon atoms and a doping atom, boron (B). B is called an acceptor atom because it has one electron less than silicon atom.

**Figure 2.7:** Energy band diagram for p-type materials. The Fermi level is positioned close to the valence band.

**Table 2.4:** Differences between n-type and p-type semiconductors.

| n-type semiconductors                   | p-type semiconductors                     |  |

|-----------------------------------------|-------------------------------------------|--|

| doped with donor atoms, native defects  | doped with acceptor atoms, native         |  |

| or composition variation                | defects or composition variation          |  |

| electrons are the majority charge       | holes are the majority charge carrier     |  |

| carrier                                 | electrons are the minority charge         |  |

| holes are the minority charge carrier   | carrier                                   |  |

| Position of Fermi level is close to the | • Position of Fermi level is close to the |  |

| conduction band                         | valence band                              |  |

## 2.3 Solar cell interfaces

# 2.3.1 p-n junction

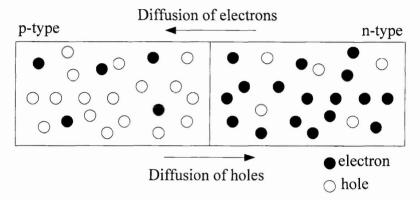

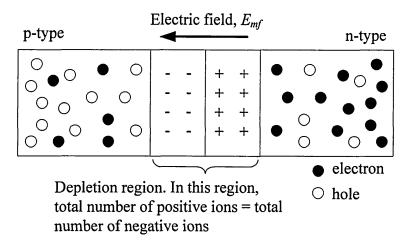

The heart of efficient solar cells lies within the photovoltaic active region. When two different semiconductors (p-type and n-type) are adjacent next to each other as shown in Figure 2.8, excessive electrons from the n-type material will diffuse into the p-type material. This leads to the leaving of positively charge ions at the vicinity of p-type material whilst the excessive holes from the p-type material diffuse into the n-type material, leaving the negatively charge ions at the vicinity of the n-type material.

Figure 2.8: Directions of diffusion of electrons and holes.

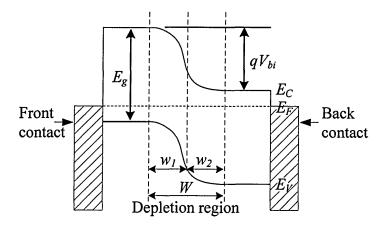

This interaction will continue until the creation of a 'barrier' with particular width that prevents excessive electrons from the n-type material diffuse into the p-type material and vice versa. This 'barrier' is known as a p-n junction. In a p-n junction, a layer of negatively charge ions now sit inside the p-type material at the vicinity of n-type material. Inside the n-type material, a layer of positively charge ions now sit at the vicinity of the p-type material. Because of two layers from differently charged ions face with each other inside the p-n junction, electric field  $\left(E_{mf} = -\frac{dV}{dx}\right)$  develops due to the electrostatic potential difference. The electric field is responsible in separation of photo-generated EHPs and minimizes the recombination. These two charged layers within the p-n junction are called depletion region because the concentration of free charge carriers is low within this region. Figure 2.9 shows the formation of p-n junction.

Figure 2.9: The formation of a p-n junction under equilibrium condition.

The formation of a p-n junction can also be represented with the energy band diagram. The band bending in Figure 2.10 represents the p-n junction or depletion region of Figure 2.9. This kind of junction is also called homo-junction because the intrinsic material used for both n- and p-type materials is same. The magnitude of the built-in potential  $V_{bi}$  (V) can be estimated using Equation (2.2) [3];

$$V_{bi} = \frac{kT}{q} \ln \left( \frac{N_a N_d}{n_i^2} \right) \tag{2.2}$$

Where;

q is the elementary charge (1.6 × 10<sup>-19</sup> C)  $N_a$  is the density of acceptor impurity atoms (cm<sup>-3</sup>) in the p-type material  $N_d$  is the density of donor impurity atoms (cm<sup>-3</sup>) in the n-type material  $n_i$  is the intrinsic concentration of electrons (cm<sup>-3</sup>)

The width of the depletion region W (cm) can be calculated using Equation 2.3 [3];

$$W = \left[\frac{2\varepsilon_s V_{bi}}{q} \left(\frac{N_a + N_d}{N_a N_d}\right)\right]^{\frac{1}{2}} \tag{2.3}$$

Where:

$\varepsilon_s$  is the permittivity of semiconductor (Fcm<sup>-1</sup>)

For the abrupt  $p^+$ -n junction where  $N_a >> N_d$ , the width of depletion region can be simplified into Equation 2.4;

$$W = \left[\frac{2\varepsilon_s V_{bi}}{qN_d}\right]^{\frac{1}{2}} \tag{2.4}$$

Figure 2.10: The band diagram of a p-n junction. The band bending represents the depletion region.

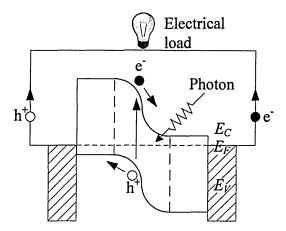

Figure 2.11 shows the role of efficient p-n junction in a solar cell. In an ideal scenario, p-n junction will absorb photons, create EHPs, separate charge carriers and transport these mobile charge carries to the external circuit to create useful current before they recombine. If the p-n junction is too narrow, recombination will easily happen because electrons can tunnel through the junction and if it is too wide, the strong electric field is absent, thus making the separation of EHPs becomes poor.

Figure 2.11: Schematic diagram showing the creation and transport of EHPs to the external circuit by a p-n junction within a solar cell.

## 2.3.2 p-i-n junction

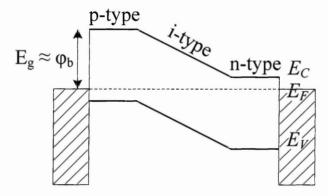

In p-i-n junctions, an intrinsic (i-type) semiconductor is sandwiched between two semiconducting layers as shown in Figure 2.12. This arrangement aligns the Fermi level of two semiconductors through the i-type material. The i-type material in the middle is responsible in creating a strong electric field for the device. It is important to note that in practical, it is very difficult to produce pure i-type semiconductor. The band diagram shown in Figure 2.12 is for pupose of discussion.

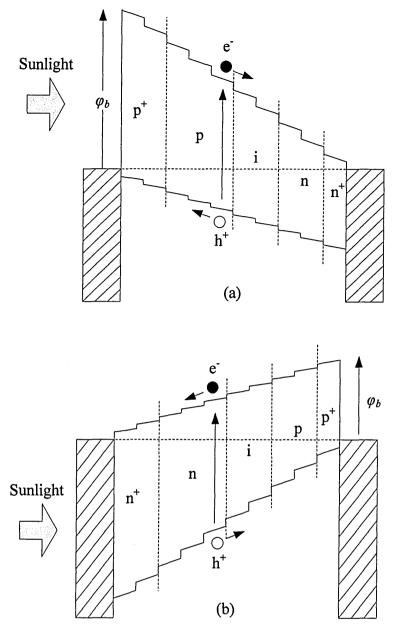

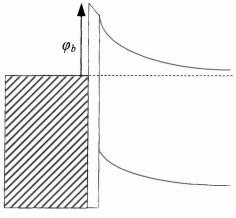

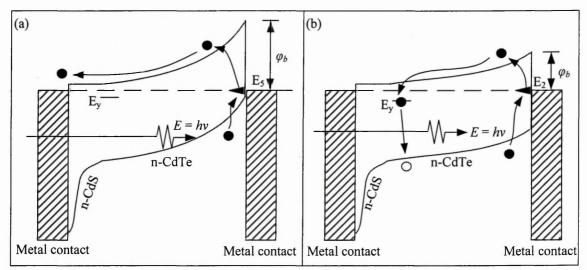

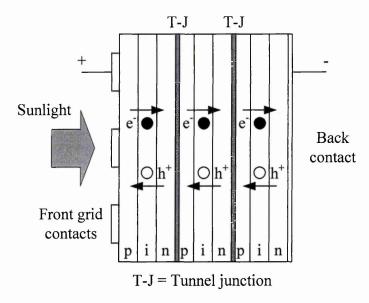

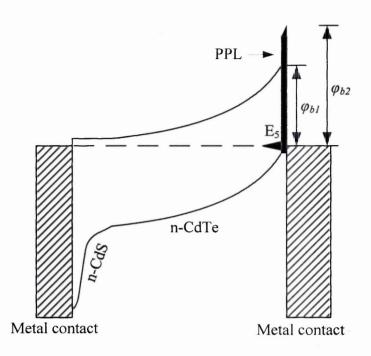

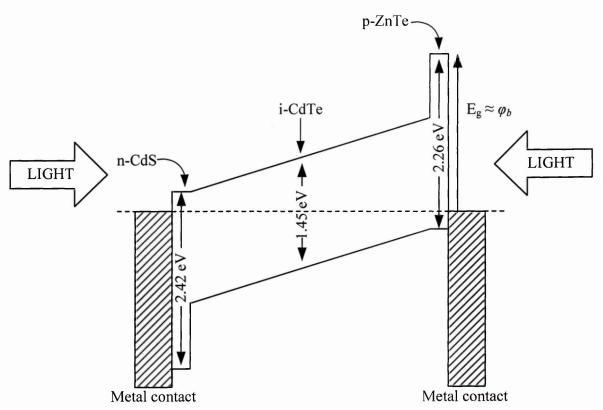

The major advantage of p-i-n structure is the possibility of getting high open circuit voltage,  $V_{oc}$  due to the presence of high potential barrier  $(\varphi_b)$  that is comparable with the band gap of the p-type materials  $(\varphi_b \approx E_g)$ . Amorphous silicon solar cell, and CdTe solar cell using p-ZnTe, i-CdTe and n-CdS are two examples of solar cells fabricated using this p-i-n structure [4-6].

Figure 2.12: p-i-n structure showing the possibility of fabricating solar cells with high potential barrier,  $(\varphi_b \approx E_g)$ .

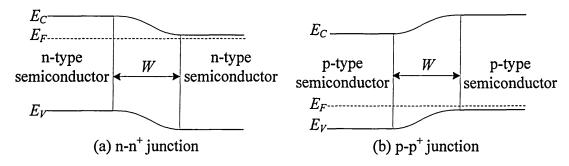

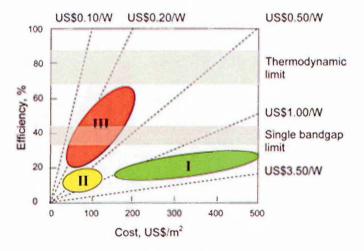

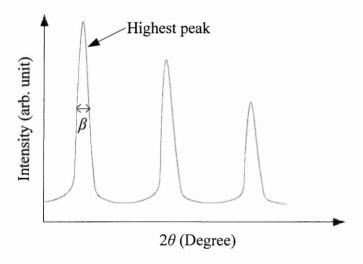

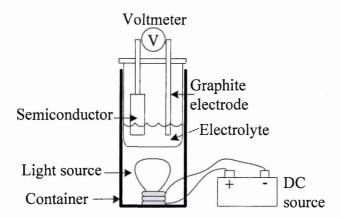

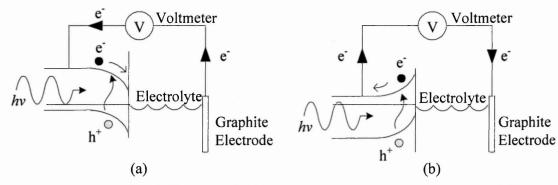

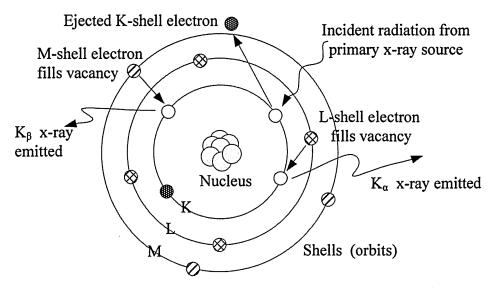

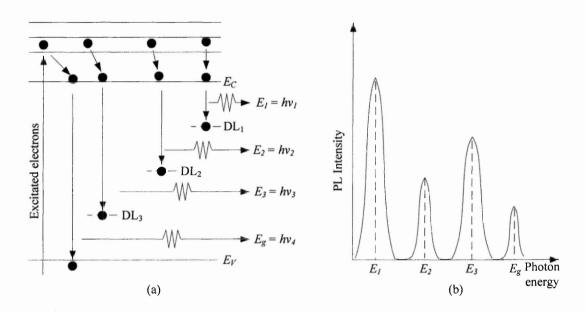

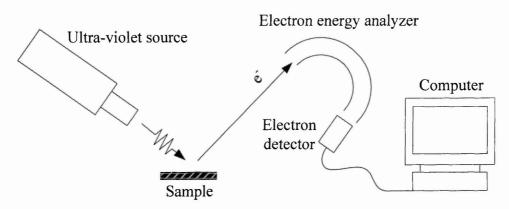

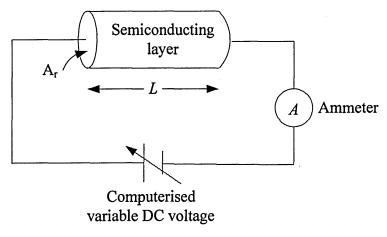

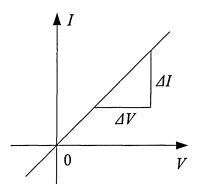

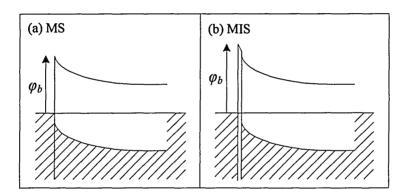

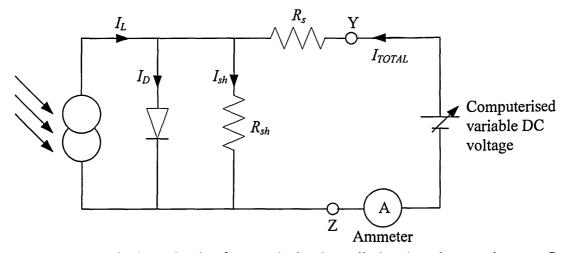

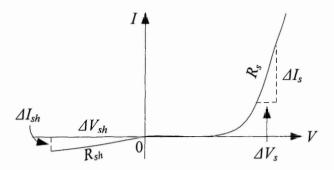

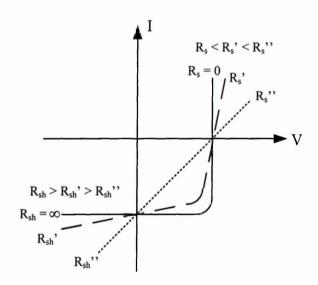

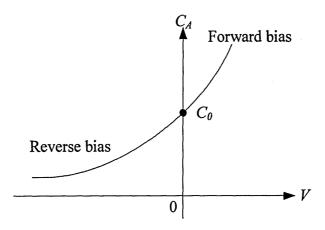

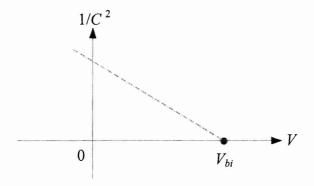

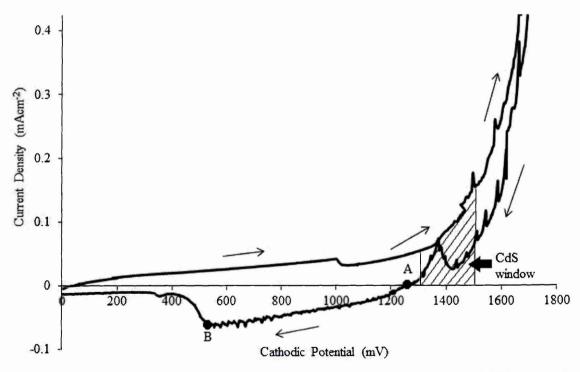

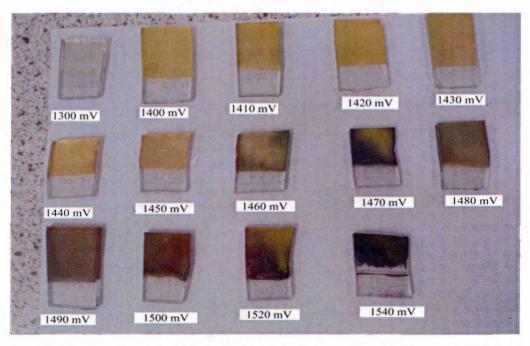

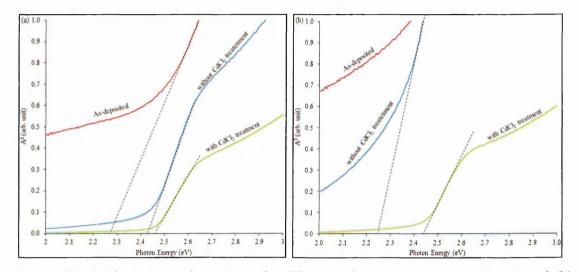

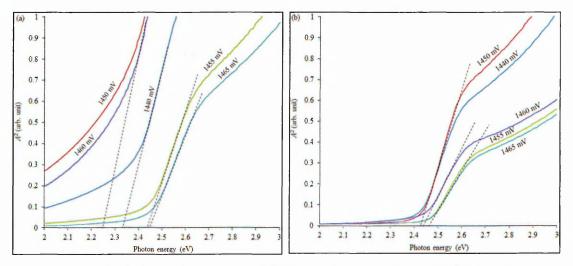

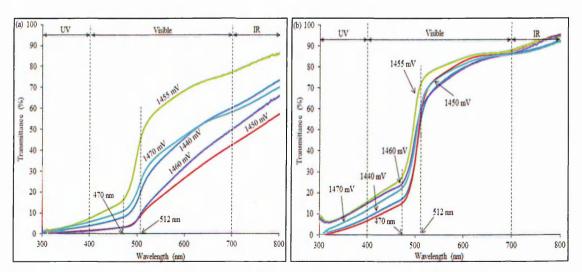

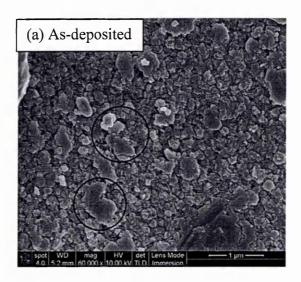

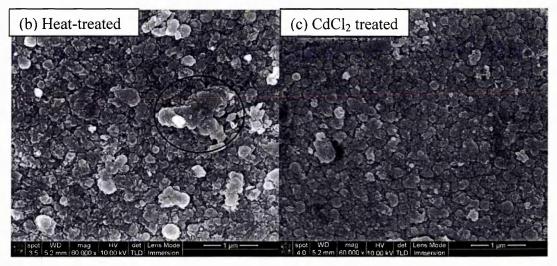

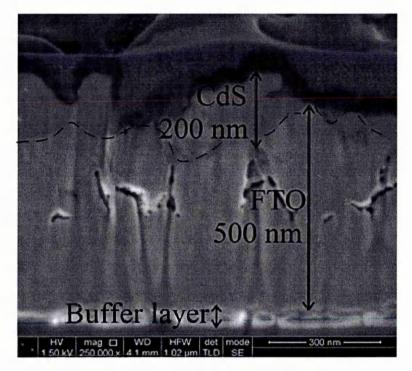

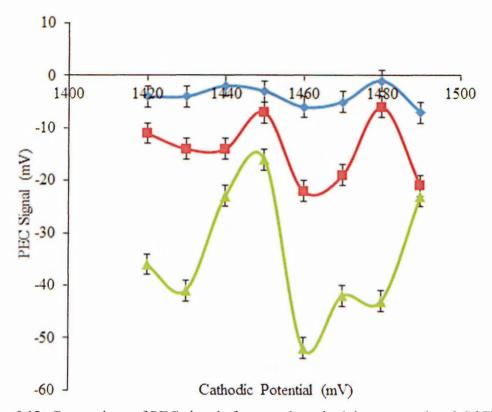

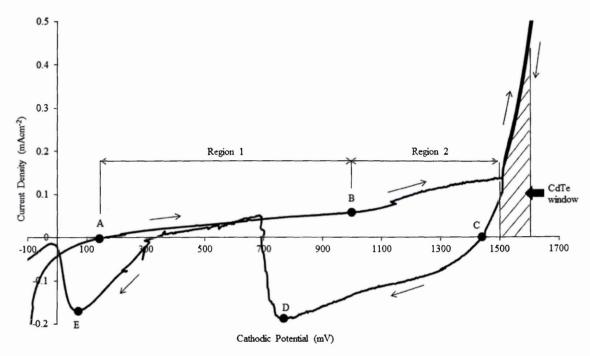

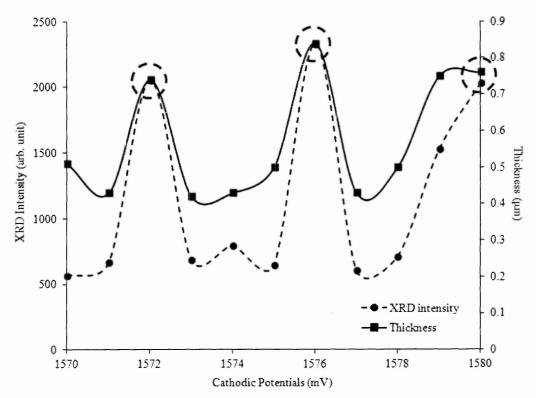

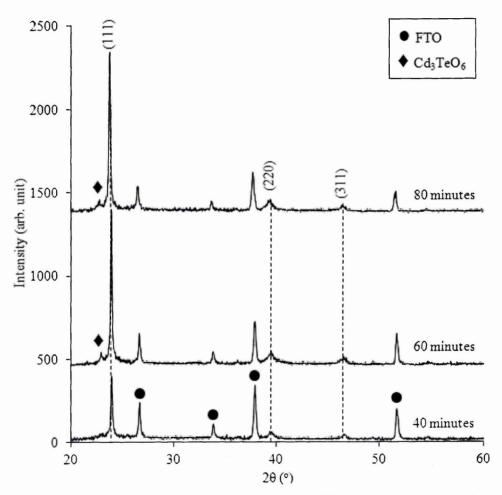

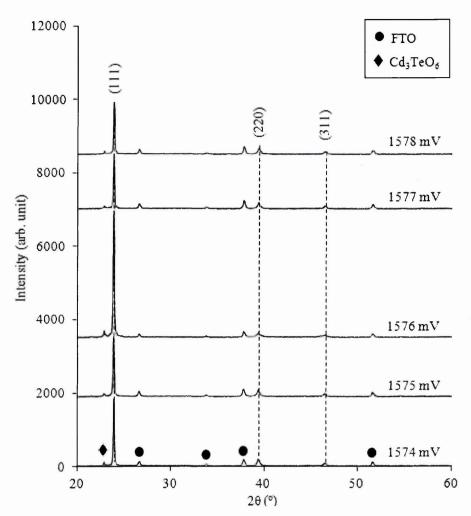

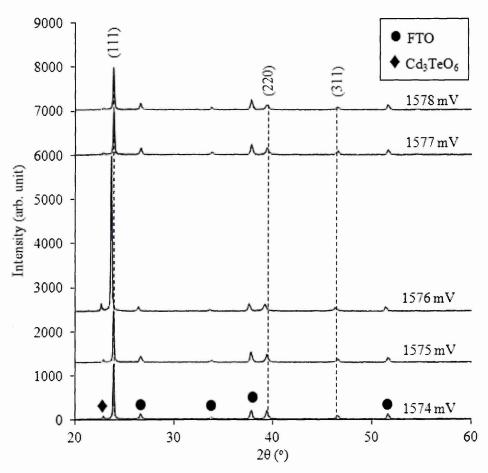

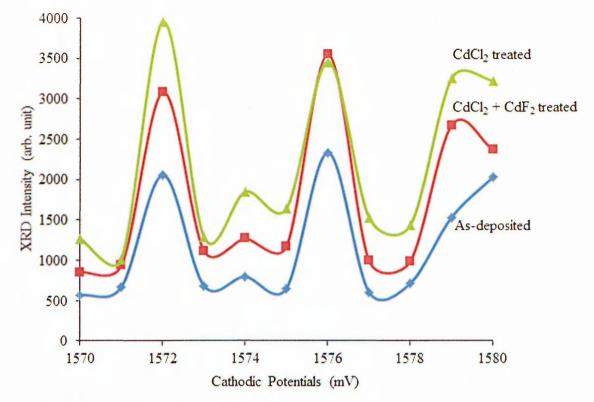

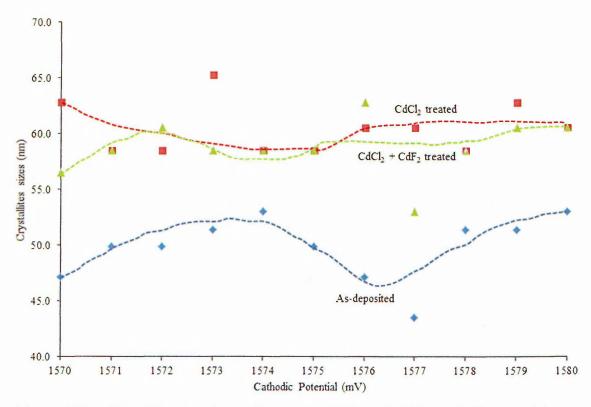

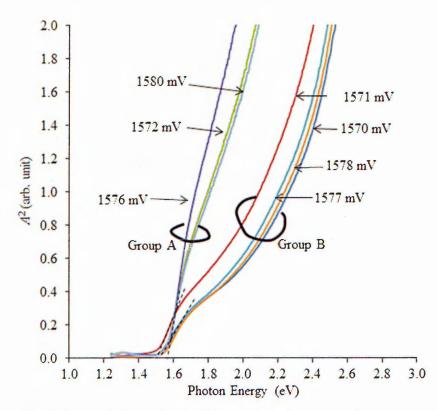

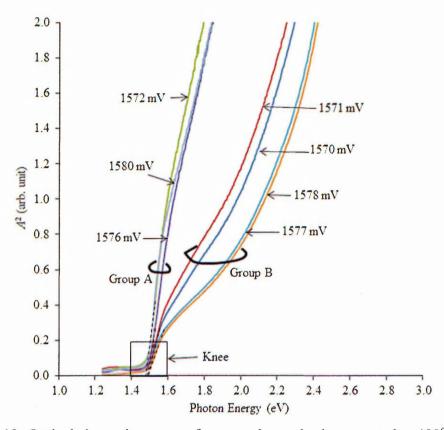

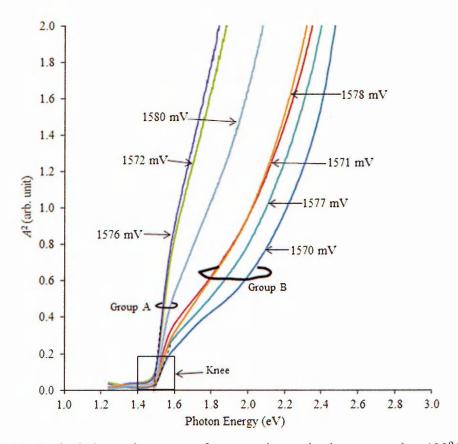

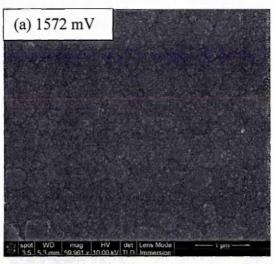

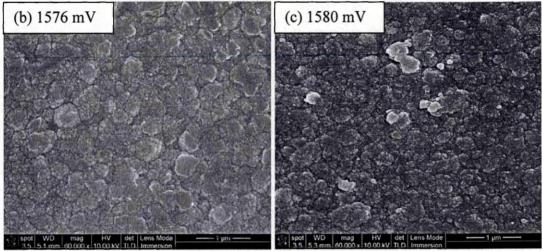

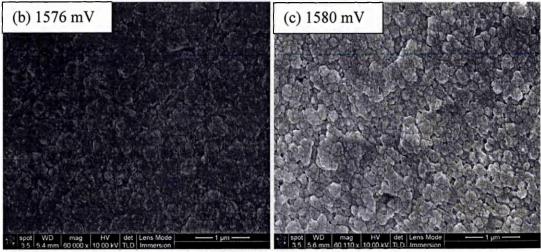

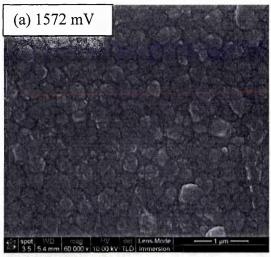

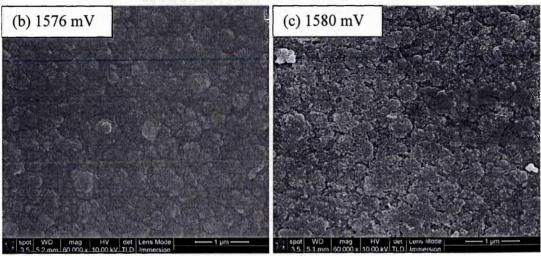

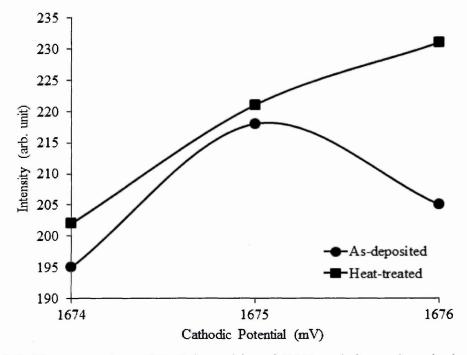

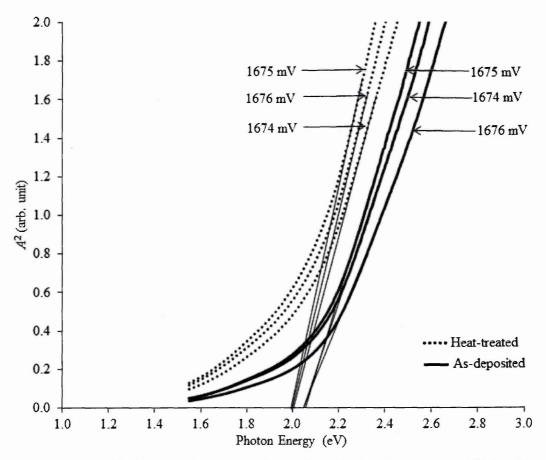

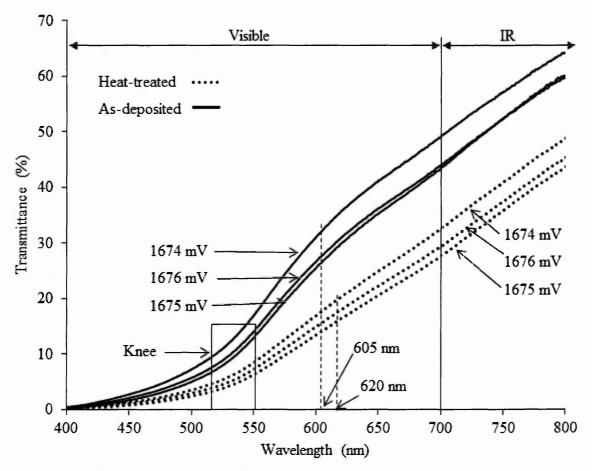

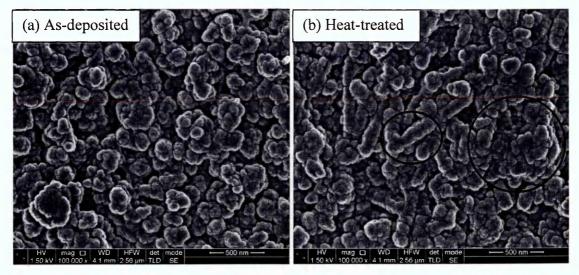

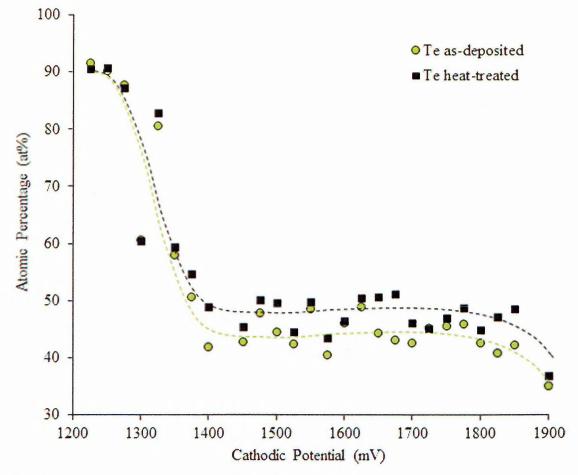

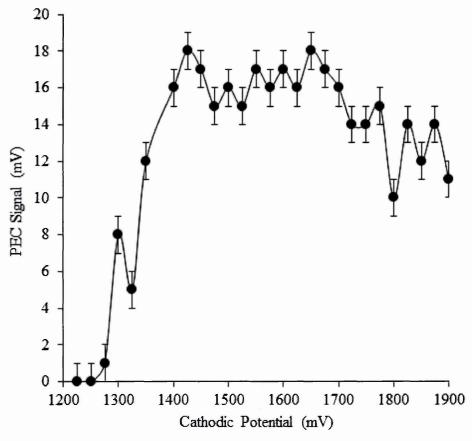

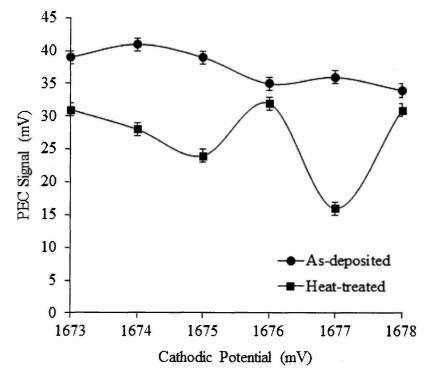

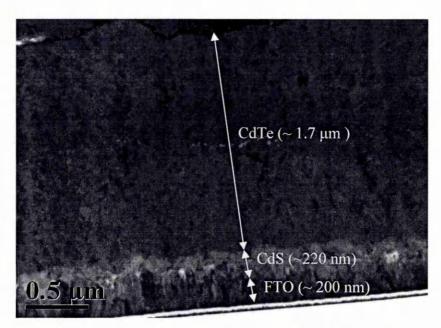

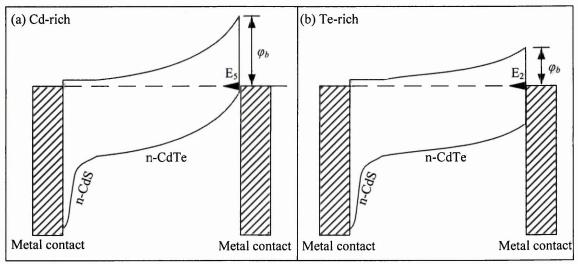

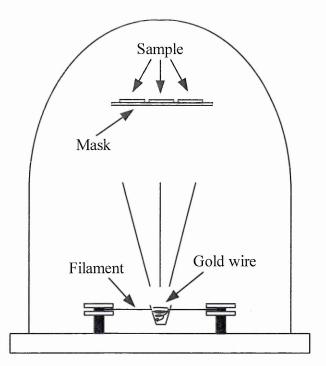

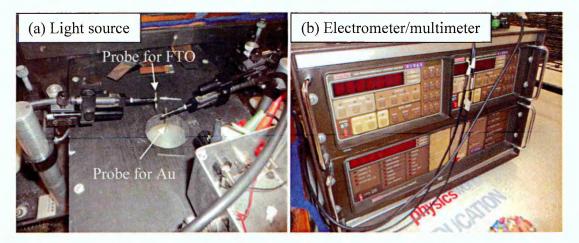

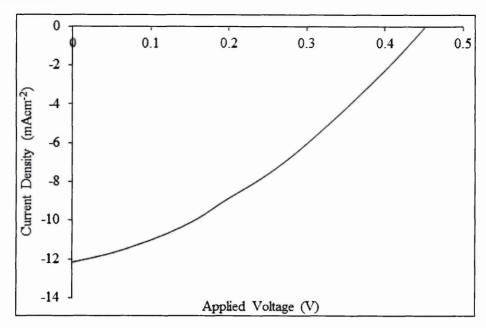

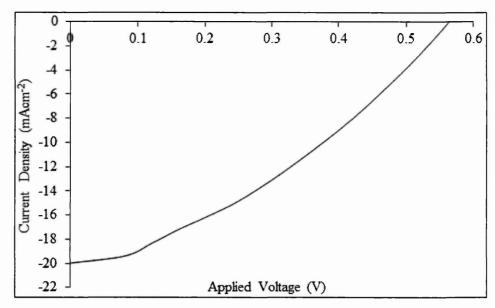

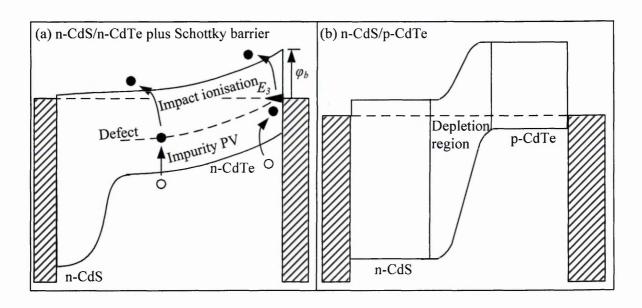

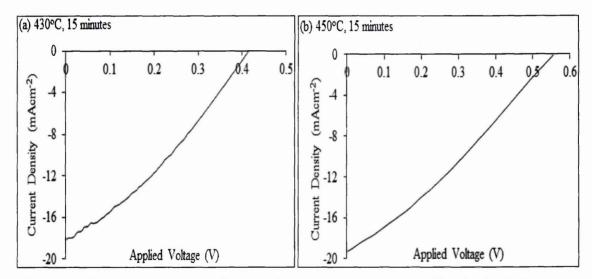

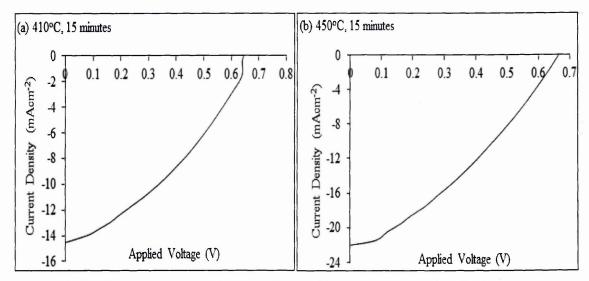

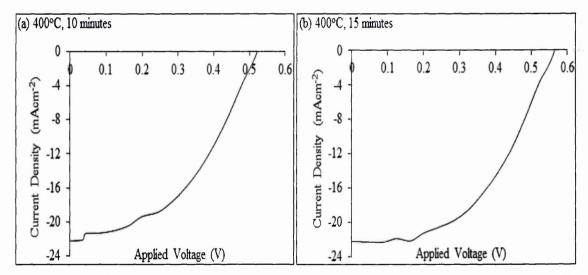

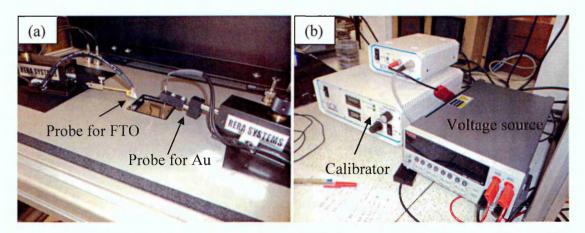

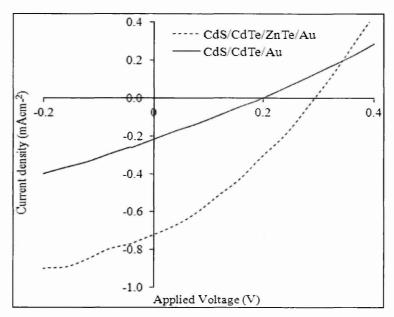

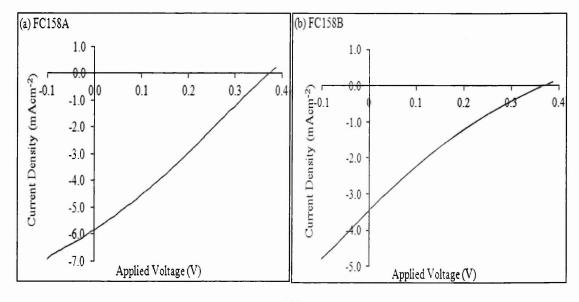

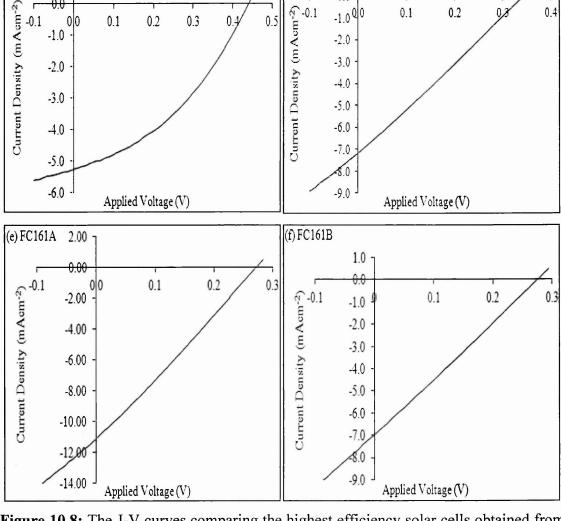

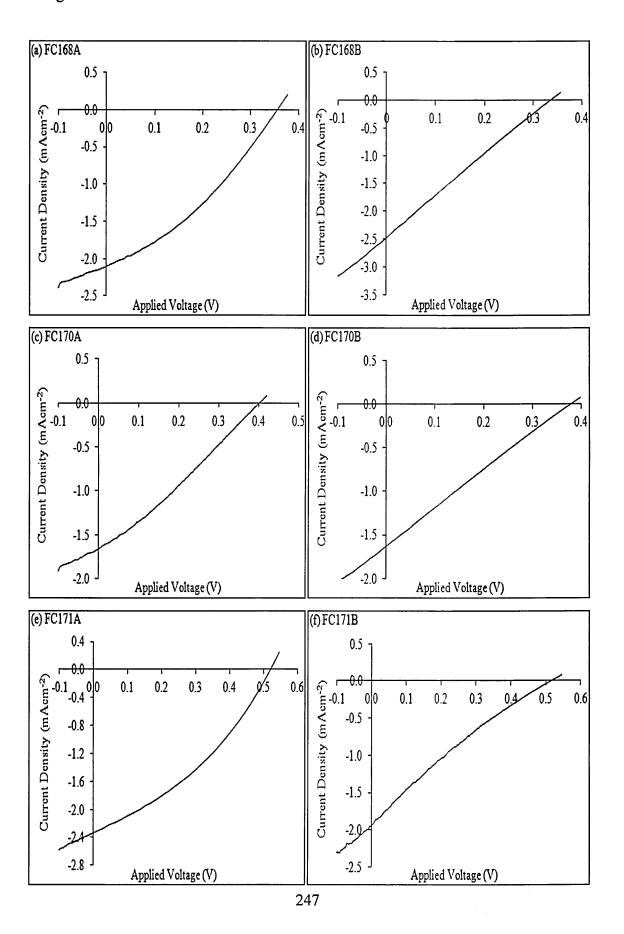

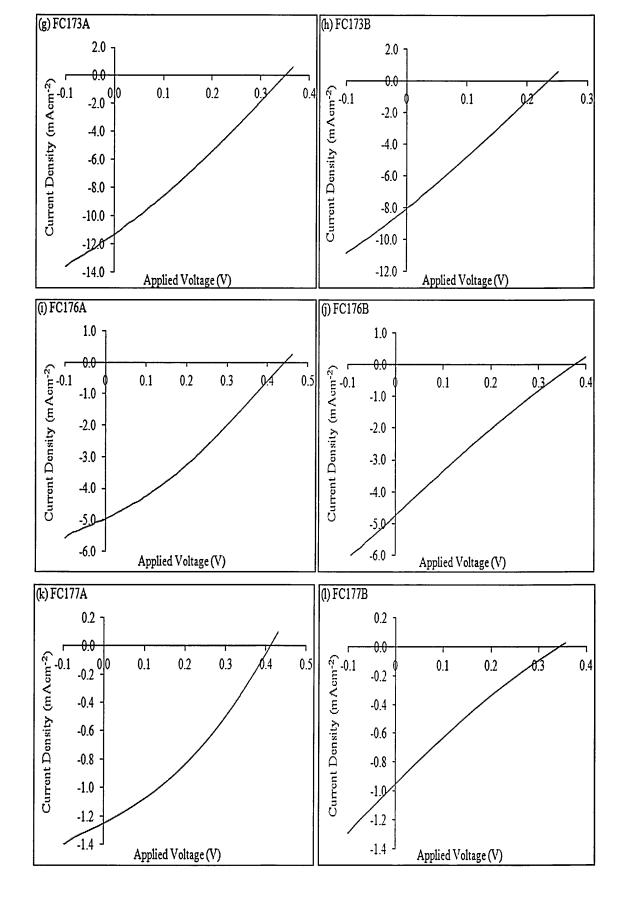

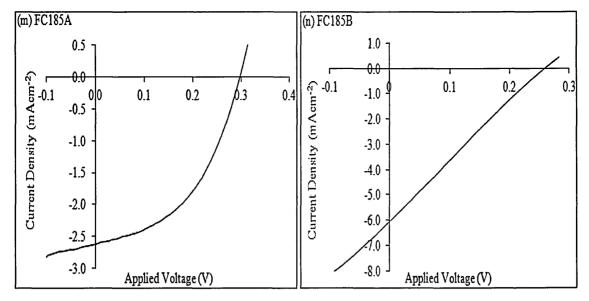

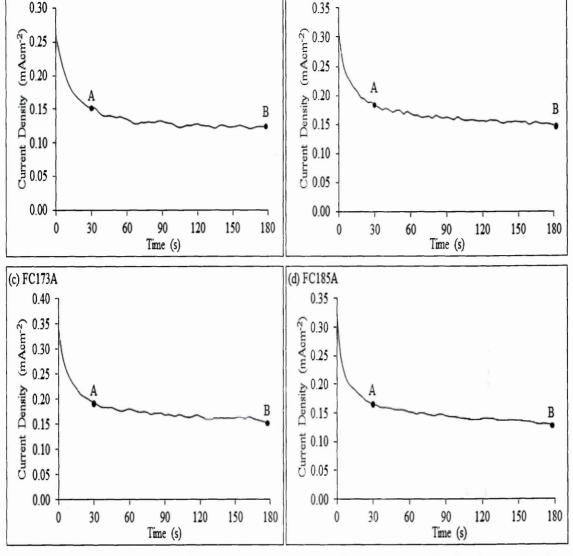

# 2.2.3 Hetero-junction