# Sheffield Hallam University

# Progress in development of graded bandgap thin film solar cells with electroplated materials

OJO, A. A. and DHARMADASA, I < http://orcid.org/0000-0001-7988-669X>

Available from Sheffield Hallam University Research Archive (SHURA) at:

https://shura.shu.ac.uk/14564/

This document is the Accepted Version [AM]

### Citation:

OJO, A. A. and DHARMADASA, I (2017). Progress in development of graded bandgap thin film solar cells with electroplated materials. Journal of Materials Science: Materials in Electronics, 28 (9), 6359-6365. [Article]

# Copyright and re-use policy

See http://shura.shu.ac.uk/information.html

#### **PROGRESS IN DEVELOPMENT OF GRADED BANDGAP THIN FILM SOLAR**

#### **CELLS WITH ELECTROPLATED MATERIALS**

A.A. Ojo\* and I.M. Dharmadasa

Electronic Materials and Sensors Group, Materials and Engineering Research Institute (MERI), Sheffield Hallam University, Sheffield S1 1WB, UK.

\*Email: <u>chartell2006@yahoo.com;</u> Tel: +44 114 225 6910 Fax: +44 114 225 6930 ABSTRACT

Photovoltaic devices are developed mainly based on p-n or p-i-n type device structures, and these devices can utilise only a fraction of the solar spectrum. In order to further improve device parameters and move towards low-cost and high-efficiency next generation solar cells, device architectures capable of harvesting all photons available should be designed and developed. One such architecture is the fully graded bandgap device structure as proposed recently based on both n-type and p-type window layers. These designs have been experimentally tested using well researched GaAs/AlGaAs system producing impressive device parameters of open circuit voltage ( $V_{oc}$ ) ~1175 mV and fill factor (FF) ~0.85. The devices have also been experimentally tested for the evidence of impurity photovoltaic (PV) effect and impact ionisation taking place within the same device. Since these structures have been experimentally proved with a well-established semiconductor, the effort has been focussed on developing these devices using low-cost and scalable electroplated semiconductors, in order to minimise manufacturing cost. This paper reviews and summarises the work carried out during the past decade on this subject. Graded bandgap devices produced using only two or three electroplated semiconductor layers have been explored and their conversion efficiencies have gradually increased from 10.0%, through 12.8% to 15.3% for different structures. While the work is progressing along this line, the paper summarises the achievements to date.

Keyword: Semiconductors, Graded bandgap, CdS/CdTe, Device configuration, Solar cells.

#### 1 INTRODUCTION

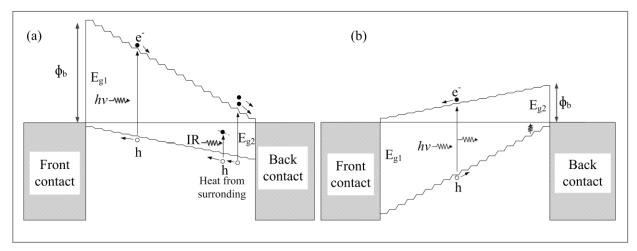

The competitiveness of solar cells lies within its conversion efficiency while its economic viability is determined by its production cost. Semiconductor (SC) deposition techniques such as electrodeposition matches the economic requirements provided efficient solar cells can be fabricated using the technique. Improvements of CdS/CdTe solar cells after about two decades of stagnation has been achieved through better understanding of materials and device issues. In a view of increasing efficiency and/or economic viability, several concepts and innovative technologies proposed include intermediate band solar cell [1], quantum dots and quantum wells solar cell [2], down and up conversion solar cell [3], plasmonic solar cell [4], hot-carrier solar cell [5], tandem solar cell with tunnel junctions [6], dye-sensitised and Perovskite solar cells [7] and graded bandgap solar cell [8-9]. Amongst the proposed concepts only tandem solar cells and graded bandgap solar cells have experimentally shown reasonable efficiency with required stability and the potential of increasing performance. The main difference between these two approaches is that the tandem solar cells efficiency increase is mostly due to increase in open-circuit voltage, Voc while in the graded bandgap solar cells the efficiency is mainly increased due to increase in the short-circuit current density, J<sub>sc</sub>. The main disadvantage of the tandem solar cell is the series connection of cells resulting into the reduction in charge carrier mobility and increase in the recombination potential of e-h pairs generated within the cell while the graded bandgap solar cell's disadvantage is the technicality of growth required. With major emphasis on graded bandgap architectures, the mechanism as proposed by Dharmadasa et al [8, 10] can be facilitated by incorporating either an n-type or p-type wide bandgap front-layer with a gradual reduction in bandgap towards p-type or n-type back layer respectively. The latter is more advantageous due to higher potential barrier height ( $\phi_b$ ) achievable for electron transport is larger than that of a device made on an n-type window layer material [11] as shown in Figure 1.

Figure 1: Schematic representation of graded bandgap solar cells based on (a) p-type window layer and (b) n-type window layer.

#### 2 THE CONCEPT AND EXPERIMENTAL VALIDATION

The concept validation was achieved using well-established Metal-Organic Vapour Phase Epitaxy (MOVPE) technique in the deposition of well-researched GaAs/AlGaAs in which 12% efficiency ( $\eta$ ) was achieved in the first run and 20% was achieved in just the second run based on improved material engineering [11]. To facilitate the device shown in Figure 1 (a), the bandgap grading was achieved by a gradual increment of Al atomic percentage to increase the bandgap of GaAs from 1.42 eV to 2.20 eV. Furthermore, the GaAs back-layer was doped n-type with Si. The Si atomic concentration was gradually reduced towards the middle of the structure, in a 3 µm thick alloy layer. Also, C concentration was increased towards the front of the device to gradually increase its p-type doping. This way, the doping profiles were changed, to vary the doping of semiconductors from n- to p- from the rear to the front of the device [10-11]. It was reported that the middle of the device shows material intrinsic properties. The hallmarks of the experimental results were the highest reported open circuit voltage ( $V_{oc}$ ) of 1175 mV and FF of ~0.85 under AM1.5 illumination condition for a single cell and the PV activity of the cell in complete darkness achieving  $V_{oc} > 700$  mV due to impurity PV effect under dark condition [12]. Furthermore, the presence of impact ionisation

was validated by the Incident Photon to Charge Carrier Efficiency (IPCE) measurement of 140% [11]. This result shows that a single photon can create more than one e-h pairs. These results confirm the presence of both impurity PV effect and impact ionisation functioning within one device making use of native defects. These results also justify the achievability of higher short-circuit current density  $J_{sc}$  above the Shockley–Queisser limit of a single *p*–*n* junction [13] for devices fabricated using multilayer graded bandgap configuration coupled with high  $V_{oc}$  (1175 mV) and the highest possible FF (0.85) values experimentally observed.

# 3 MULTILAYER GRADED BANDGAP DEVICE STRUCTURE UTILISING

#### ELECTRODEPOSITION TECHNIQUE

Electrodeposition technique is a process of coating or deposition of metal(s) or semiconductors compounds on electrically conducting substrate. Electrodeposition of semiconductors which was first introduced by Panicker et al [14] can be achieved using either a 3-electrode (3E) or 2- electrode (2E) configuration, suitable electrolyte containing the required precursors, power supply, stirrer and hot plate. It should be noted that the main difference in setup between the 3E and 2E electrodeposition configuration is the incorporation of a reference electrode (WE) as utilised in the 2E configuration. The effect of electroplating configuration on the electrodeposited semiconductor layer properties have been published by the author's group elsewhere [15]. With major advantages such as low setup cost, possibility of depositing n-, i-, and p- type semiconductor from the same electroplating setup by deposition voltage variation, self-purification, bandgap engineering, proven scalability and manufacturability [16], [17], electrodeposition is suitable for the growth of multilayer graded bandgap device structure.

#### 3.1 STAGE 1 – PRELIMINARY WORK ON GLASS/FTO/n-ZnS/n-CdS/n-CdTe/Au

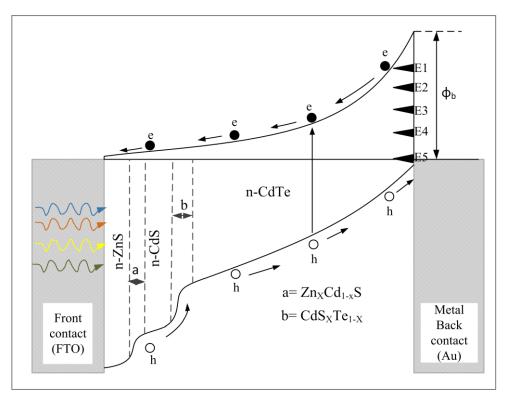

After experimentally testing the new concept of graded bandgap devices, work has begun to produce these devices using low-cost and scalable electroplated materials. For this purpose, over 14 different semiconductor layers have been established using electrodeposition technique within the authors' group [18]–[28]. The main challenge was the incorporation of different glass/FTO/WL/AL/MC, layers into glass/FTO/BL/WL/AL/MC, glass/FTO/BL/WL/AL/PPL/MC in n-n+SB, n-p, n-n-n, n-n-p, n-n-n-p configurations, where FTO is fluorine-doped tin oxide, BL is the buffer layer, WL is the window layer, AL is the absorber layer, PPL is the pinhole plugin layer, MC is the metal contact and SB is the Schottky barrier. Echendu et al [29] demonstrated the possibility of achieving high efficiency graded bandgap solar cell using all-electrodeposited glass/FTO/n-ZnS/n-CdS/n-CdTe/Au in which the n-ZnS layer is the BL, n-CdS is the WL and n-CdTe is the AL. This device structure follows the second type of graded bandgap devices as shown in Figure 1 (b) and its real situation is shown in Figure 4.

Figure 2: Typical band diagram of the glass/FTO/n-ZnS/n-CdS/n-CdTe /Au thin film solar cell.

The use of Au on *n*-type CdTe back-layer is to create a large Schottky barrier (SB) at the metal/semiconductor (M/SC) interface. It should be noted that the inclusion of the Schottky barrier structures near the back contact is capable of producing potential barrier heights of (~1.20 eV) greater than or comparable to barrier heights in p-n junction devices based on CdTe [29]. It has been experimentally shown that there are five possible Fermi level pinning positions on n-CdTe/metal interfaces [30] producing different potential barriers. In fact, this does affect the reproducibility of the devices.

The precursors present in the aqueous electrolytic bath in which ZnS was deposited were 0.3 M ZnCl<sub>2</sub> and 0.03 M (NH<sub>4</sub>)<sub>2</sub>S<sub>2</sub>O<sub>3</sub> [31], the precursors for the CdS layer were 0.3 M CdCl<sub>2</sub> and 0.03 M Na<sub>2</sub>S<sub>2</sub>O<sub>3</sub> [32] while CdTe layer was grown from aqueous electrolytic bath containing 1 M CdSO<sub>4</sub> and 1 mM TeO<sub>2</sub> [29]. The thicknesses of the electrodeposited layers are g/FTO/n-ZnS (300 nm)/n-CdS (600 nm)/n-CdTe (1700 nm)/Au as calculated using Faraday's equation as shown in eq. (1). The electronic parameters measured for completed devices are tabulated in Table 1.

$$T = \frac{JtM}{nFd} \tag{1}$$

It should be noted that in between subsequently deposited layers, the materials were rinsed, dried in a stream of nitrogen and treated both chemically and thermally to improve the electronic properties of the deposited layers [33]. The glass/FTO/n-ZnS layers were heat treated between (300 and 350) °C for (10 to 15) minutes while both the glass/FTO/n-ZnS/n-CdS and the glass/FTO/n-ZnS/n-CdS/n-CdTe layers were treated between (400 and 450) °C in air for (15 to 20) minutes in the presence of CdCl<sub>2</sub> after deposition. After the completion of growth and treatment, the layers were acidically etched using solution containing potassium dichromate (K<sub>2</sub>Cr<sub>2</sub>O<sub>7</sub>) and concentrated sulphuric acid (H<sub>2</sub>SO<sub>4</sub>) and alkalinically etched using solution containing sodium hydroxide (NaOH) and sodium thiosulfate (Na<sub>2</sub>S<sub>2</sub>O<sub>3</sub>) for the duration of 2 seconds and 2 minutes respectively to make the CdTe surface Cd-rich and

improve the metal/semiconductor contact [30, 34]. To avoid the back-layer oxidation, immediately after etching, 100 nm Au contacts were evaporated in a high vacuum system with the aid of a 2 mm diameter metal mask. The treatment and etching processes were unique for all the devices fabricated and discussed in this review. Using the same precursors for ZnS and CdTe, Echendu et al [35] fabricated a glass/FTO/n-ZnS/n-CdTe layer with the major consideration of reducing the thickness of ZnS from 300 to 200 nm, while the CdTe thickness remained at 1700 nm. Due to inter-diffusion, the formation of an intermediate material such as ZnCdS<sub>x</sub>Te<sub>1-x</sub> is generated during heat treatment resulting in a gradedbandgap configuration [35]. At AM1.5 illuminated condition, the champion cell conversion efficiency of 10.4% was observed with the measured value of J<sub>sc</sub> higher than the Shockley-Queisser limit of a single p-n junction [13]. This is due to the multi-layer and multi-junction n-n-n+SB device configurations theoretically proposed [10, 36] and experimentally tested [8, 11] in the literature, although, FF was low and a comparatively low Voc were observed. The low Voc values as reported in this work indicate the presence of leakage paths which might also be due to low-purity precursors utilised in the deposition of the semiconductor layers. The main challenge for the reported work was the low fill factor (FF) values. Under the dark condition, the series resistance  $(R_s)$  was high and the shunt resistance  $(R_{sh})$  was low. The observed doping density (N<sub>D</sub>) of  $8.1 \times 10^{14}$  cm<sup>-3</sup> falls within the doping concentration of reported high-efficiency solar cells ( $\sim 1.0 \times 10^{14} - 5 \times 10^{15} \text{ cm}^{-3}$ ) [37-38].

| DEVICE CONFIGURATION                                     | PARAMETERS UNDER AM1.5<br>ILLUMINATED CONDITION |                                          |                         |      | PARAMETERS UNDER<br>DARK CONDITION |                             |                           | Ref. |

|----------------------------------------------------------|-------------------------------------------------|------------------------------------------|-------------------------|------|------------------------------------|-----------------------------|---------------------------|------|

|                                                          | η<br>(%)                                        | J <sub>sc</sub><br>(mAcm <sup>-2</sup> ) | V <sub>oc</sub><br>(mV) | FF   | R <sub>s</sub><br>(Ω)              | $R_{sh}\left(\Omega\right)$ | $N_D$ (cm <sup>-3</sup> ) |      |

| n-ZnS/n-CdS/n-CdTe/Au                                    | 10.4                                            | 40.8                                     | 640                     | 0.40 | 175                                | $4.6 \times 10^{3}$         | $8.1 \times 10^{14}$      | [29] |

| $n\text{-}ZnS/ZnCdS_{x}Te_{1\text{-}x}/n\text{-}CdTe/Au$ | 12.0                                            | 47.8                                     | 646                     | 0.39 |                                    |                             |                           | [35] |

| n-ZnS/n-CdS/n-CdTe/Au                                    | 12.8                                            | 41.5                                     | 670                     | 0.46 | 1351                               | $8.1 \times 10^{6}$         | 5.2×10 <sup>15</sup>      | [39] |

| n-In <sub>x</sub> Se <sub>y</sub> /n-CdS/n-CdTe/Au       | 10.0                                            | 38.1                                     | 640                     | 0.41 | 309                                | $4.5 \times 10^{3}$         | $2.0 \times 10^{14}$      | [50] |

| n-CdS/n-CdTe/p-CdTe/Au                                   | 15.3                                            | 33.8                                     | 730                     | 0.62 | 500                                | 7.2×10 <sup>6</sup>         | 6.6×10 <sup>14</sup>      | [49] |

Table 1: Graded bandgap device parameters reported under both AM1.5 illuminated condition and dark conditions.

#### 3.2 STAGE 2 – OPTIMISATION OF MATERIALS AND DEVICE STRUCTURES

#### 3.2.1 PRECURSOR REPLACEMENT AND THICKNESS OPTIMISATION

Further improvement in material properties in both ZnS and CdS due to changes in deposition precursors as documented by Madugu et al [19] and Abdul-Manaf et al [24] respectively led to the enhancement in the n-ZnS/n-CdS/n-CdTe/Au type solar cell's efficiency as reported by Olusola [39]. The ZnS precursors were replaced with 0.15 M ZnSO<sub>4</sub> and 0.15 M (NH<sub>4</sub>)<sub>2</sub>S<sub>2</sub>O<sub>3</sub> [19]. The culmination of the concentration and precursor utilised by Madugu et al [19] is the growth of both n- and p- type ZnS from the same aqueous electrolytic bath by intrinsic doping. While the CdS precursors as documented by Echendu et al [29] were replaced with 0.3 M CdCl<sub>2</sub> and 0.03 M (NH<sub>4</sub>)<sub>2</sub>S<sub>2</sub>O<sub>3</sub> [24]. The replacement of the Na<sub>2</sub>S<sub>2</sub>O<sub>3</sub> with (NH<sub>4</sub>)<sub>2</sub>S<sub>2</sub>O<sub>3</sub> was due to the possibility of absorption, adsorption and accumulation of Na in the electrolyte on the grown CdS layer. It is well known that CdS is intrinsically an n-type material due to defects such as Cd interstitials and S vacancies in the crystal lattice [40] while Na is a p-type dopant in CdS. Therefore, the introduction of p-dopant into an n-type layer will increase the resistivity of the deposited layer due to compensation which might have a negative impact on the fabricated PV devices. The CdTe layer was deposited from a similar aqueous electrolyte by Echendu et al containing 1 M CdSO<sub>4</sub> and 1 mM TeO<sub>2</sub> [29]. The thicknesses of all the layers incorporated by Olusola [39] were optimised and reduced to 100 nm for the n-ZnS layer and 150 nm for the n-CdS layer to decrease the effect of parasitic absorption [41] on the fabricated solar cell devices. The CdTe layer thickness was also reduced to 1200 nm. As observed in Table 1, a champion conversion efficiency of 12.8% was observed at AM1.5 with improvement in the J<sub>sc</sub> which might be due to high transmittance of both the BL and WL due to the reduction in thicknesses. A comparative improvement in both the  $V_{oc}$  and FF were also observed which might be attributed to improvement in material quality. The increase in  $V_{oc}$  signifies a comparative reduction in the shunt while the improvement in the FF can be attributed to the increase in the  $R_{sh}$  although the  $R_s$  observed were still high.

#### 3.2.2 BUFFER LAYER ALTERATION (In<sub>x</sub>Se<sub>y</sub>)

Although CdS proves the best heterojunction partner to CdTe due to the comparatively low lattice mismatch of 10% [42]  $In_xSe_y$  was incorporated into the glass/FTO/n- $In_xSe_y$ /n-CdS/n-CdTe/Au due to its excellent wetting property on FTO surface [20]. The  $In_xSe_y$  was deposited from an aqueous electrolytic bath containing 0.10 M InCl<sub>3</sub> and 0.025 M SeO<sub>2</sub> [20]. At a low  $In_xSe_y$  thickness of ~80 nm incorporated in the device structure, a bandgap of 2.89 eV was achieved through bandgap engineering which is one of the advantages of electrodeposition technique. This could be accomplished through the deposition voltage variation to increase the concentration of one of the constituents [43-44] and/or through thickness optimisation [45], [46] which is not limited to electrodeposition.

The CdS and CdTe thicknesses utilised in this work were 150 nm and 2500 nm respectively. The CdS layers were deposited from an aqueous electrolyte containing 0.075 M CdCl<sub>2</sub> and 0.15 M (NH<sub>4</sub>)<sub>2</sub>S<sub>2</sub>O<sub>3</sub> [24] while the CdTe layers were deposited from 1 M CdSO<sub>4</sub> and 1 mM TeO<sub>2</sub> [29] aqueous electrolyte. The glass/FTO/n-In<sub>x</sub>Se<sub>y</sub> was treated at 300°C for 10 minutes in air while the subsequent glass/FTO/n-In<sub>x</sub>Se<sub>y</sub>/n-CdS and glass/FTO/n-In<sub>x</sub>Se<sub>y</sub>/n-CdS/n-CdTe layers were treated between (400 and 450)°C in air for (15 to 20) minutes in the presence of CdCl<sub>2</sub> after deposition. The highest efficiency observed was 10.0% at AM1.5, with a fill factor of 0.41, V<sub>oc</sub> of 640 mV and J<sub>sc</sub> of 38.1 mAcm<sup>-2</sup>. Although the doping density of the absorber material falls within the high-efficiency solar cell range of (~1.0×10<sup>14</sup> – 5×10<sup>15</sup> cm<sup>-3</sup>) [37-38], the low R<sub>sh</sub> which suggest high leakage current was observed in dark condition as shown in Table 1. From observation, an alteration in buffer layer from ZnS to In<sub>x</sub>Se<sub>y</sub> do not show any significant improvement in the electronic parameters of the fabricated cell. The

highpoint in this work is the possibility of bandgap engineering of  $In_xSe_y$  and its incorporation in a glass/FTO/n-In<sub>x</sub>Se<sub>y</sub>/n-CdS/n-CdTe/Au device structure.

#### 3.2.3 MULTILAYER CONFIGURATION

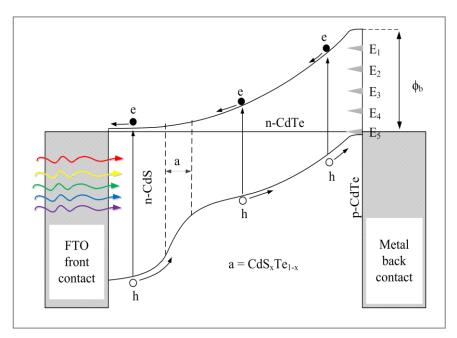

The glass/FTO/n-CdS/n-CdTe/p-CdTe/Au was initialised to reduce deposition and treatment complexity by eliminating the use of buffer layer and optimising the window layer. In addition, there is a possibility of Na leaching from the glass layer into the semiconductor layer when subjected to subsequent heating of the glass/FTO. Provided the semiconductor layer are p-type, the leaching of Na which is a p-type dopant to both CdS and CdTe is advantageous but it might result into high resistivity of the layer due to compensation if the semiconductor layers are n-type. In this work, the optimisation of CdS layer as presented by Ojo et al [47] took into consideration the electroplating mechanism, effect of CdS thickness and parasitic absorption. Based on these findings, 120 nm thick CdS layer was utilised using 0.3 M CdCl<sub>2</sub> and 0.03 M (NH<sub>4</sub>)<sub>2</sub>S<sub>2</sub>O<sub>3</sub> [24] while the CdTe layer was electrodeposited from an aqueous electrolyte containing 1 M Cd(NO<sub>3</sub>)<sub>2</sub> and ~1 mM TeO<sub>2</sub> [28]. The 1200 nm *n*-CdTe and 30 nm *p*-CdTe were grown in a continuous deposition process in the same aqueous electrolytic bath by changing only the deposition voltage [28]. The ability to grow both n-type and p-type semiconductor layers in the same bath through intrinsic doping earmarks the advantages of electrodeposition [48].

Figure 3: Typical band diagram of the glass/FTO/n-CdS/n-CdTe/p-CdTe /Au thin film solar cell.

The incorporation of the thin p-CdTe layer was necessitated to set the Fermi level (FL) close to the valence band to achieve high barrier height of ~1.20 eV. This p-CdTe layer was also introduced to remove reproducibility issues due to Fermi level pinning possibilities at one of the five different energy levels [30]. The thickness of the p-CdTe layer has also been optimised to achieve high-performance devices.

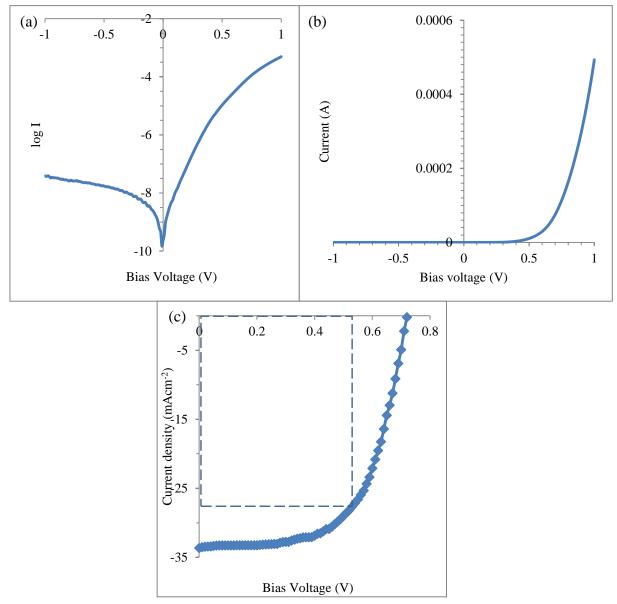

Figure 4: Typical (a) log-linear and (b) linear-linear current–voltage curves of g/FTO/n-CdS/n-CdTe/p-CdTe/Au under dark conditions, while (c) is the I-V curve under A.M1.5 illuminated conditions.

From the fabricated glass/FTO/n-CdS/n-CdTe/p-CdTe/Au structures, champion cell conversion efficiency of 15.3% under AM1.5 illumination was observed. The I-V curves of the devices are shown in Figure 4 and summarised in Table 1. Furthermore, an improved  $V_{oc}$  of 730 mV and FF of 0.62 were reported which might be due to improved material processing step as documented by Ojo et al [49]. The yield recorded in this set of experiment was 100% but the variation in device parameters and consistency still requires improvement. The

observed  $R_s$  of 500  $\Omega$  measured for the champion cells are high and reduction of this should further improve the FF and the  $J_{sc}$ . In a view of increasing conversion efficiency and reducing the  $R_s$  copper-gold contacts were evaporated on a direct replica of the glass/FTO/n-CdS/n-CdTe/p-CdTe to achieve glass/FTO/n-CdS/n-CdTe/p-CdTe/Cu-Au devices. A champion efficiency of 18.5% was observed under AM1.5 conditions. But due to instability and reproducibility issues, the results have not been published yet until the electronic parameters of the fabricated cells can be stabilised and further experimentation performed.

#### 4 CONCLUSION

The utilisation of electrodeposition technique under both 3-electrode and 2-electrode configuration show promises in the fabrication of high-efficiency solar cell using graded bandgap multilayer device configuration. This review iterates the gradual development in attaining high efficiency using graded bandgap configuration. As expected, these preliminary studies on n-n-n plus large Schottky barrier and n-n-p structures produced PV active devices showing best efficiencies of 12.8% and 15.3% respectively. It is evident that improvement in device properties such as  $R_s$ ,  $R_{sh}$ , FF, and  $V_{oc}$  is required. Furthermore, work on the incorporation of the p-type window layer as shown in Figure 1 (a) are continuing as proposed by Dharmadasa et al [10] to achieve even more efficient devices. This structure is more capable of producing high  $V_{oc}$  values as demonstrated by GaAs/AlGAs systems.

#### ACKNOWLEDGEMENT

The principal author would like to thank the Tertiary Education Fund (TETFund) Nigeria, Sheffield Hallam University and Ekiti State University (EKSU), Nigeria, for their support to undertake this research.

#### REFERENCES

- M. Wolf, "Limitations and Possibilities for Improvement of Photovoltaic Solar Energy Converters: Part I: Considerations for Earth's Surface Operation," *Proc. IRE*, vol. 48, no. 7, pp. 1246–1263, 1960.

- [2] K. W. J. Barnham and G. Duggan, "A new approach to high-efficiency multi-band-gap solar cells," *J. Appl. Phys.*, vol. 67, no. 7, pp. 3490–3493, 1990.

- [3] T. Trupke, M. A. Green, and P. Würfel, "Improving solar cell efficiencies by down-conversion of high-energy photons," *J. Appl. Phys.*, vol. 92, no. 3, 2002.

- [4] Y. Y. Lee, W. J. Ho, and Y. T. Chen, "Performance of plasmonic silicon solar cells using indium nanoparticles deposited on a patterned TiO2 matrix," *Thin Solid Films*, vol. 570, no. PB, pp. 194–199, 2014.

- [5] Y. Takeda and T. Motohiro, "Highly efficient solar cells using hot carriers generated by two-step excitation," *Sol. Energy Mater. Sol. Cells*, vol. 95, no. 9, pp. 2638–2644, 2011.

- [6] J. F. Geisz, D. J. Friedman, J. S. Ward, A. Duda, W. J. Olavarria, T. E. Moriarty, J. T. Kiehl, M. J. Romero, A. G. Norman, and K. M. Jones, "40.8% efficient inverted triple-junction solar cell with two independently metamorphic junctions," *Appl. Phys. Lett.*, vol. 93, no. 12, 2008.

- [7] A. B. F. Martinson, M. S. Góes, F. Fabregat-Santiago, J. Bisquert, M. J. Pellin, and J. T. Hupp, "Electron Transport in Dye-Sensitized Solar Cells Based on ZnO Nanotubes: Evidence for Highly Efficient Charge Collection and Exceptionally Rapid Dynamics," *J. Phys. Chem. A*, vol. 113, no. 16, pp. 4015–4021, 2009.

- [8] I. M. Dharmadasa, J. S. Roberts, and G. Hill, "Third generation multi-layer graded band gap solar cells for achieving high conversion efficiencies II: Experimental results," *Sol. Energy Mater. Sol. Cells*, vol. 88, no. 4, pp. 413–422, 2005.

- [9] T. Stelzner, M. Pietsch, G. Andrä, F. Falk, E. Ose, and S. Christiansen, "Silicon nanowire-based solar cells," *Nanotechnology*, vol. 19, no. 29, p. 295203, 2008.

- [10] I. M. Dharmadasa, "Third generation multi-layer tandem solar cells for achieving high conversion efficiencies," *Sol. Energy Mater. Sol. Cells*, vol. 85, no. 2, pp. 293–300, 2005.

- [11] I. M. Dharmadasa, A. A. Ojo, H. I. Salim, and R. Dharmadasa, "Next generation solar cells based on graded bandgap device structures utilising rod-type nano-materials," *Energies*, vol. 8, no. 6, pp. 5440–5458, 2015.

- [12] I. M. Dharmadasa, O. Elsherif, and G. J. Tolan, "Solar Cells Active in Complete Darkness," J. Phys. Conf. Ser., vol. 286, p. 12041, 2011.

- [13] W. Shockley and H. J. Queisser, "Detailed Balance Limit of Efficiency of p-n Junction Solar Cells," J. Appl. Phys., vol. 32, no. 3, p. 510, 1961.

- [14] M. P. R. Panicker, M. Knaster, and F. A. Kroger, "Cathodic Deposition of CdTe from Aqueous Electrolytes," *J. Electrochem. Soc.*, vol. 125, no. 4, p. 566, 1978.

- [15] O. K. Echendu, K. B. Okeoma, C. I. Oriaku, and I. M. Dharmadasa, "Electrochemical Deposition of CdTe Semiconductor Thin Films for Solar Cell Application Using Two-Electrode and Three-Electrode Configurations: A Comparative Study," *Adv. Mater. Sci. Eng.*, vol. 2016, pp. 1–8, 2016.

- [16] I. M. Dharmadasa and J. Haigh, "Strengths and Advantages of Electrodeposition as a Semiconductor Growth Technique for Applications in Macroelectronic Devices," J. *Electrochem. Soc.*, vol. 153, no. 1, p. G47, 2006.

- [17] S. Bonilla and E. A. Dalchiele, "397 ELECTROCHEMICAL DEPOSITION AND CHARACTERIZATION OF CdTe P O L Y C R Y S T A L L I N E T H I N FILMS," vol. 204, 1991.

- [18] O. K. Echendu, a. R. Weerasinghe, D. G. Diso, F. Fauzi, and I. M. Dharmadasa, "Characterization of n-Type and p-Type ZnS Thin Layers Grown by an Electrochemical Method," *J. Electron. Mater.*, vol. 42, no. 4, pp. 692–700, 2013.

- [19] M. L. Madugu, O. I.-O. Olusola, O. K. Echendu, B. Kadem, and I. M. Dharmadasa, "Intrinsic Doping in Electrodeposited ZnS Thin Films for Application in Large-Area Optoelectronic Devices," *J. Electron. Mater.*, 2016.

- [20] M. L. Madugu, L. Bowen, O. K. Echendu, and I. M. Dharmadasa, "Preparation of indium selenide thin film by electrochemical technique," J. Mater. Sci. Mater. Electron., vol. 25, pp. 3977–3983, 2014.

- [21] O. I. Olusola, M. L. Madugu, N. A. Abdul-Manaf, and I. M. Dharmadasa, "Growth and characterisation of n- and p-type ZnTe thin films for applications in electronic devices," *Curr. Appl. Phys.*, vol. 16, no. 2, pp. 120–130, 2016.

- [22] O. I. Olusola, V. Patel, and I. M. Dharmadasa, "OPTIMISATION OF pH FOR ELECTRODEPOSITION OF n-CdSe THIN FILMS FOR APPLICATIONS IN PHOTOVOLTAIC DEVICES," *EUPVSEC 2014 Conf. Proc.*, no. July 2016, pp. 1852–1856, 2014.

- [23] O. I. Olusola, O. K. Echendu, and I. M. Dharmadasa, "Development of CdSe thin films for application in electronic devices," *J. Mater. Sci. Mater. Electron.*, vol. 26, no. 2, pp. 1066–1076, 2014.

- [24] N. A. Abdul-Manaf, A. R. Weerasinghe, O. K. Echendu, and I. M. Dharmadasa, "Electro-plating and characterisation of cadmium sulphide thin films using ammonium thiosulphate as the sulphur source," *J. Mater. Sci. Mater. Electron.*, vol. 26, no. 4, pp. 2418–2429, 2015.

- [25] H. I. Salim, O. I. Olusola, A. A. A. Ojo, K. A. Urasov, M. B. Dergacheva, and I. M. Dharmadasa, "Electrodeposition and characterisation of CdS thin films using thiourea precursor for application in solar cells," *J. Mater. Sci. Mater. Electron.*, vol. 27, no. 7, pp. 6786–6799, 2016.

- [26] A. A. Ojo and I. M. Dharmadasa, "Investigation of electronic quality of electrodeposited cadmium sulphide layers from thiourea precursor for use in large area electronics," *Mater. Chem. Phys.*, vol. 180, pp. 14–28, 2016.

- [27] N. Abdul-Manaf, H. Salim, M. Madugu, O. Olusola, and I. Dharmadasa, "Electro-Plating and Characterisation of CdTe Thin Films Using CdCl2 as the Cadmium Source," *Energies*, vol. 8, no. 10, pp. 10883–10903, 2015.

- [28] H. I. Salim, V. Patel, a. Abbas, J. M. Walls, and I. M. Dharmadasa, "Electrodeposition of CdTe thin films using nitrate precursor for applications in solar cells," *J. Mater. Sci. Mater. Electron.*, vol. 26, no. 5, pp. 3119–3128, 2015.

- [29] O. Echendu and I. Dharmadasa, "Graded-Bandgap Solar Cells Using All-Electrodeposited ZnS, CdS and CdTe Thin-Films," *Energies*, vol. 8, no. 5, pp. 4416– 4435, May 2015.

- [30] I. M. Dharmadasa, "Recent developments and progress on electrical contacts to CdTe, CdS and ZnSe with special reference to barrier contacts to CdTe," vol. 36, no. 4, pp. 249–290, 1998.

- [31] O. K. Echendu and I. M. Dharmadasa, "Effects of Thickness and Annealing on Optoelectronic Properties of Electrodeposited ZnS Thin Films for Photonic Device Applications," *J. Electron. Mater.*, vol. 43, no. 3, pp. 791–801, 2013.

- [32] O. K. Echendu, U. S. Mbamara, K. B. Okeoma, C. Iroegbu, C. A. Madu, I. C. Ndukwe, and I. M. Dharmadasa, "Effects of deposition time and post-deposition annealing on the physical and chemical properties of electrodeposited CdS thin films for solar cell application," *J. Mater. Sci. Mater. Electron.*, 2016.

- [33] I. M. Dharmadasa, "Review of the CdCl2 Treatment Used in CdS/CdTe Thin Film

Solar Cell Development and New Evidence towards Improved Understanding," *Coatings*, vol. 4, no. 2, pp. 282–307, 2014.

- [34] I. M. Dharmadasa, C. J. Blomfield, C. G. Scott, R. Coratger, F. Ajustron, and J. Beauvillain, "METAL / n-CdTe INTERFACES: A STUDY OF ELECTRICAL CONTACTS BY DEEP LEVEL TRANSIENT SPECTROSCOPY," vol. 42, no. 4, pp. 1–10, 1998.

- [35] O. K. Echendu, F. Fauzi, A. R. Weerasinghe, and I. M. Dharmadasa, "High shortcircuit current density CdTe solar cells using all-electrodeposited semiconductors," *Thin Solid Films*, vol. 556, pp. 529–534, 2014.

- [36] A. De Vos, "Detailed balance limit of the efficiency of tandem solar cells," *J. Phys. D. Appl. Phys.*, vol. 13, no. 5, pp. 839–846, 2000.

- [37] B. M. Basol and B. McCandless, "Brief review of cadmium telluride-based photovoltaic technologies," *J. Photonics Energy*, vol. 4, p. 40996, 2014.

- [38] M. Gloeckler, I. Sankin, and Z. Zhao, "CdTe solar cells at the threshold to 20% efficiency," *IEEE J. Photovoltaics*, vol. 3, no. 4, pp. 1389–1393, 2013.

- [39] O. I. Olusola, "Optoelectronic devices based on graded bandgap structures utilising electroplated semiconductors," Sheffield Hallam University, 2016.

- [40] R. Lozada-Morales and O. Zelaya-Angel, "Photoluminescence analysis of CdS thin films under phase transition," *Thin Solid Films*, vol. 281–282, no. 1–2, pp. 386–389, 1996.

- [41] J. E. Granata and J. R. Sites, "Effect of CdS thickness on CdS/CdTe quantum efficiency," Conf. Rec. Twenty Fifth IEEE Photovolt. Spec. Conf. 1996, pp. 853–856, 2000.

- [42] N. Romeo, A. Bosio, V. Canevari, and A. Podestà, "Recent progress on CdTe/CdS thin film solar cells," Sol. Energy, vol. 77, no. 6, pp. 795–801, 2004.

- [43] O. I. Olusola, H. I. Salim, and I. M. Dharmadasa, "One-sided rectifying p-n junction diodes fabricated from n-CdS and p-ZnTe: Te semiconductors," *Mater. Res. Express*, vol. 3, no. 9, p. 95904, Sep. 2016.

- [44] I. M. Dharmadasa, R. P. Burton, and M. Simmonds, "Electrodeposition of CuInSe2 layers using a two-electrode system for applications in multi-layer graded bandgap solar cells," *Sol. Energy Mater. Sol. Cells*, vol. 90, no. 15, pp. 2191–2200, 2006.

- [45] E. S. M. Goh, T. P. Chen, C. Q. Sun, and Y. C. Liu, "Thickness effect on the band gap and optical properties of germanium thin films," J. Appl. Phys., vol. 107, no. 2, p. 24305, Jan. 2010.

- [46] M. Ben Rabeh, N. Khedmi, M. A. Fodha, and M. Kanzari, "The effect of thickness on optical band gap and N-type conductivity of CuInS2 thin films annealed in air atmosphere," *Energy Procedia*, vol. 44, no. May 2013, pp. 52–60, 2014.

- [47] A. A. Ojo, H. I. Salim, O. I. Olusola, M. L. Madugu, and I. M. Dharmadasa, "Effect of thickness: a case study of electrodeposited CdS in CdS/CdTe based photovoltaic devices," *J. Mater. Sci. Mater. Electron.*, pp. 1–10, Oct. 2016.

- [48] I. M. Dharmadasa, Advances in thin-film solar cells. Singapore: Pan Stanford, 2013.

- [49] A. A. Ojo and I. M. Dharmadasa, "15.3% efficient graded bandgap solar cells fabricated using electroplated CdS and CdTe thin films," *Sol. Energy*, vol. 136, pp. 10–14, 2016.

- [50] M. L. Madugu, "Processing of Semiconductors and Thin Film Solar Cells Using Electroplating," Sheffield Hallam University, 2016.

# LIST OF FIGURES

| Figure 1: Schematic representation of graded bandgap solar cells based on (a) p-type wind | low  |

|-------------------------------------------------------------------------------------------|------|

| ayer and (b) n-type window layer.                                                         | 2    |

| Figure 2: Typical band diagram of the glass/FTO/n-ZnS/n-CdS/n-CdTe /Au thin film so       | olar |

| ell.                                                                                      | 2    |

| Figure 3: Typical band diagram of the glass/FTO/n-CdS/n-CdTe/p-CdTe /Au thin film so      | olar |

| ell.                                                                                      | 2    |

| Figure 4: Typical (a) log-linear and (b) linear-linear current-voltage curves of g/FTC    | )/n- |

| CdS/n-CdTe/p-CdTe/Au under dark conditions, while (c) is the I-V curve under A.M          | [1.5 |

| lluminated conditions.                                                                    | 2    |